ASIC-Readout Electronics

The CIPix ASIC-Chip

The CIPix board

FPGA based readout of the CIPix board

Goal of the CASCADE-detector development project is to provide a position sensitive instrument that allows to detect neutrons at highest count rates with the best possible spatial resolution at large areas. Immediately these targets imply a very large number of detection channels and an immense overall increase in data rate, compared to currently employed technology. With the general capacity of the CASCADE-detector front-end to meet such specifications, the bottle neck in data acquisition is shifted towards readout electronics. Every single neutron detection event, coming in at very high rates, has to be labled with position information as well as eventually a time-stamp for time-of-flight applications and stored in some adequate format. CASCADE has extended their goals to include readout-electronics in order to maintain scaleability of the entire data acquisition system.

CASCADE enjoyes the vivid synergies with high energy physics at Heidelberg University through a collaboration with the Heidelberg ASIC-Laboratory. The ASIC-Lab has developed the analog readout ASIC-chip CIPix as an excerpt from the previously developed HELIX-Chip. CIPix is primarily employed by Prof. Straumann et al. at the university of Zürich for the readout of the inner proportional chamber of the H1-Detector at DESY. Employment of the CIPix as readout front-end electronics for CASCADE results in a readout bandwidth (no. of channels x single pixel acquisition rate capacity), degree of miniaturization as well as reduction in cost, novel to neutron applications.

The CIPix ASIC-Chip

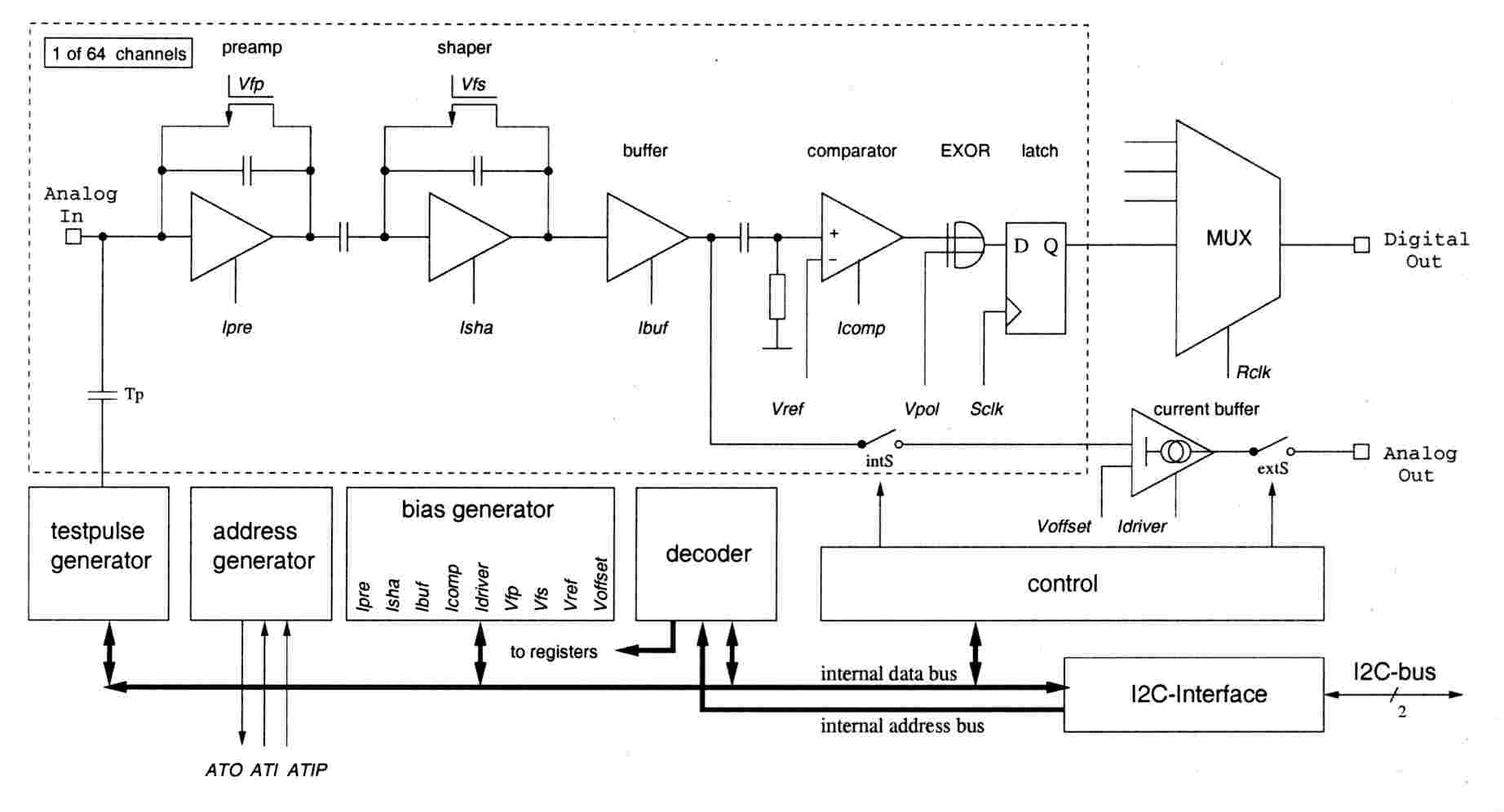

CIPix integrates 64 individual analog input channels designed to cope with 10MHz data acquisition rate on every channel. Each one is equipped with an individual low-noise pre-amp, a shaper, a buffer and a discriminator, where shaping time, gain and discriminator levels can be programmed on-line via a digital interface. The 64 digital output channels are mulitplexed 4:1 and transfered at 40MHz to the succeeding data acquisition chain.

|

Internal block-schematic for one of 64 channels on the readout ASIC CIPix. |

The CIPix board

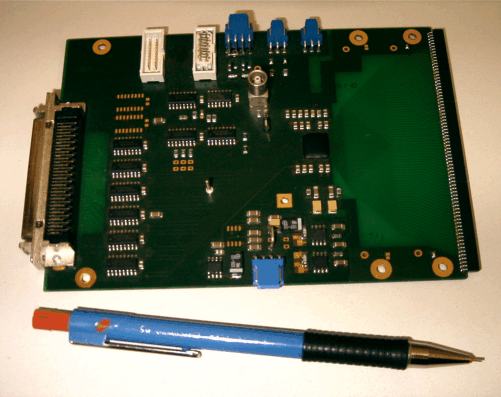

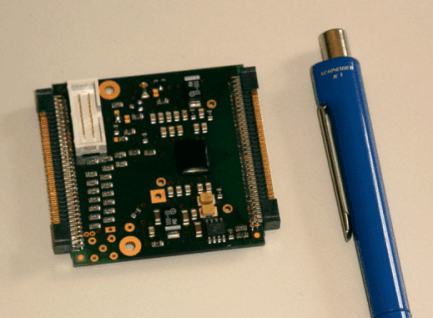

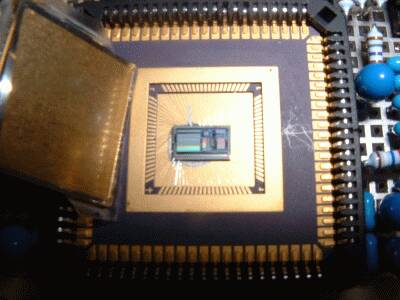

|

For first evaluative tests, the chip was bonded into a commercial chip-package, which was be mounted onto a test-board. |

On a first test-board, communication with the CIPix could be established to an extend that the chip could be programmed and programmation confirmed successful. The experience won was then used for the development of a professional electronics board, which provides diverse infrastructure to the chip, carries the CIPix directly bonded on board and includes the analog geometrical fan-in from detector dimensions to the multiply staggered input channels on the chip. Mounted to this board, the CIPix has now been employed for first measurements on a CASCADE Neutron-Detector.

FPGA based readout of the CIPix board

Due to the high data rate, the CIPix is capable of (64 readout channels, firing at a maximum of 10 MHz each) a high bandwidth real-time system will be necessary to handle further data processing. FPGA technology is very suitable for this task. It can be used to de-multiplex all the digital output signals of the ASIC and to reconstruct the neutron events in terms of position and time. Furthermore, an FPGA allows to histogram and store data in local memory or to send it as event data to any further back-end electronic system.

After the CIPix became available to us, setup and tests towards an entire system began. The data chain, started with a CASCADE-Detector equipped with a CIPix readout. The ASIC was read out by an FPGA, which was used for data processing and compression. Data could then be transferred via VME to a computer. This system was finally evaluated on a neutron beam at ILL.

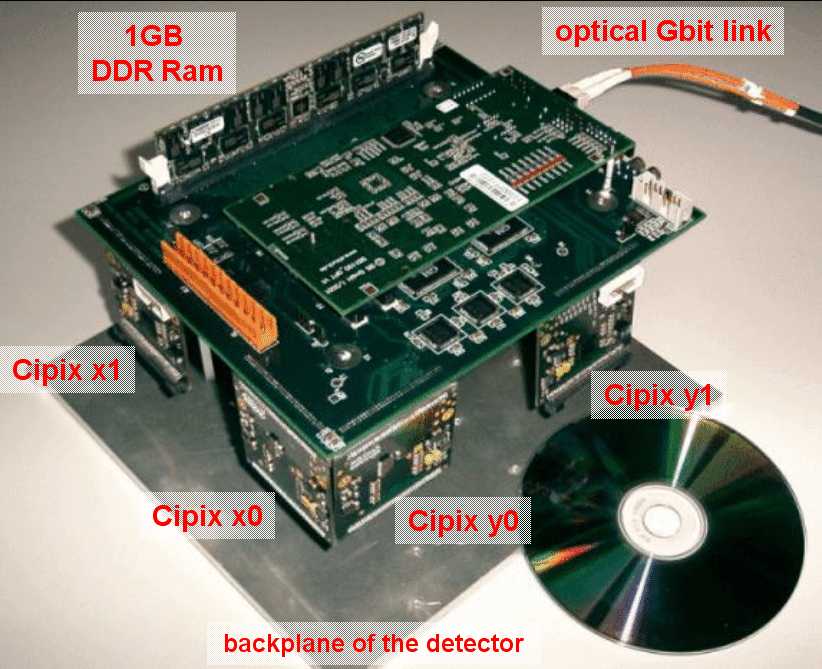

Based upon this experience, a new FPGA board was designed and produced (see the next two pictures). Equipped with a Xilinx 'VIRTEX II' FPGA it is capable of simultaneously reading out four CIPix boards and will be employed on the new 2D CASCADE detector. Event reconstruction (position and time) as well as control of the 4 CIPix boards will be done by the FPGA. Furthermore SRAM and 1GB of DDR-RAM are available locally on the detector so that data can be stored in any format desired by the user. Data transfer to a PC or workstation is realized via an optical link (1GBit/s). The entire electronic readout system is located on the backside of the detector-module. It will be decoupled galvanically from other instrument control systems.