### Designing with VHDL

### (control questions)

# Simple concurrent assignments

```

LIBRARY IEEE;

USE IEEE.STD LOGIC 1164.ALL;

entity a2of3 is

port (a0 : in std_logic;

al : in std_logic;

a2 : in std_logic;

y : out std_logic);

end a2of3;

architecture al of a2of3 is

architecture a2 of a2of3 is

signal g0, g1, g2 : std logic;

signal g0, g1, g2 : std logic;

begin

begin

g0 \ll a0 and a1;

g2 \ll a2 and a0;

g1 <= a1 and a2;

y <= g0 or (g1 or g2);</pre>

g2 \ll a2 and a0;

g1 \leq a1 and a2;

y \leq g0 \text{ or } g1 \text{ or } g2;

q0 \ll a0 and a1;

end;

end;

```

The two architectures are 1) equivalent; 2) different

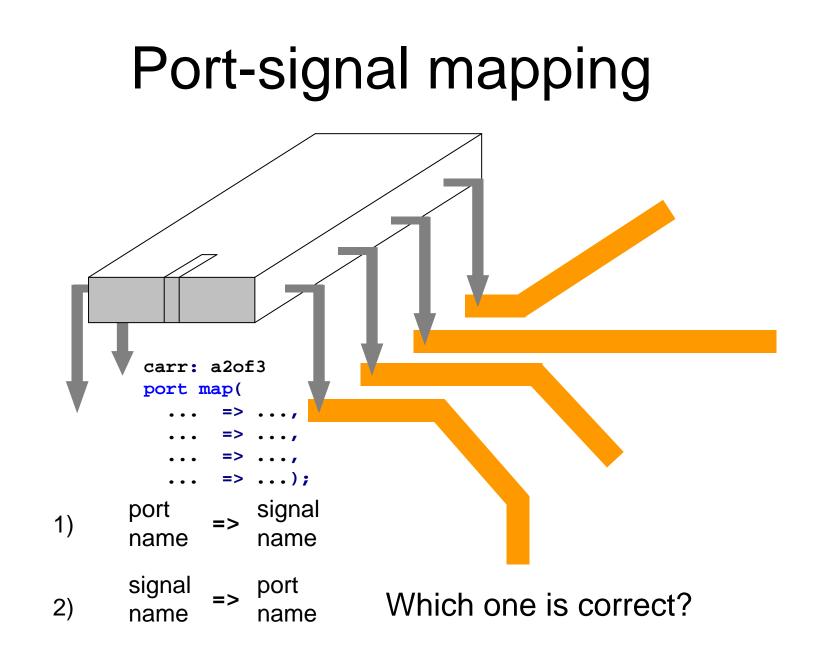

#### Instantiation of sub-blocks

```

-- component declaration

component a2of3 is

port (a0 : in std logic;

al : in std_logic;

a2 : in std logic;

y : out std logic);

end component;

b)

a)

C)

carr: a2of3

carr: a2of3

port map(

carr: a2of3

port map(a, cin, b, cout);

a0 => a,

port map(a, b, cin, cout);

al => b,

. . .

. . .

a2 => cin,

У

=> cout);

```

The three instantiations are 1) equivalent; 2) all different; 3) one (which?) differs from the others

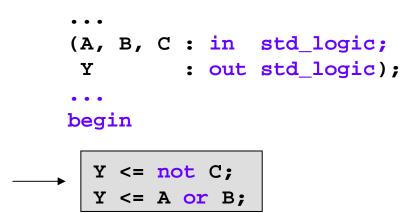

#### Multiple drivers

end;

This code is

OK, the first assignment will be just ignored;

not allowed;

3) allowed, but represents an inverter and an or-gate with outputs shorted together

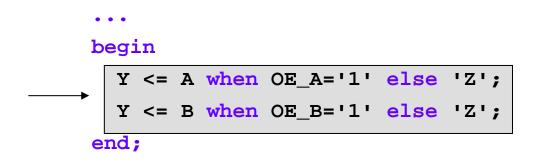

#### Multiple drivers

This is allowed only when the signals are of the type

```

1) std_logic

```

2) std\_ulogic

#### 3) **bit**

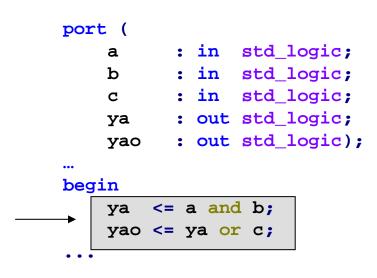

#### Ports and signals

1) This code is OK

2) A modification is necessary to get this code compiled (what?)

#### Data types

subtype reg\_data is std\_logic\_vector(31 downto 0); subtype reg\_cmd is std\_logic\_vector( 0 downto 3); subtype byte is std\_logic\_vector( 8 downto 1); subtype fixedp is std\_logic\_vector( 7 downto -2); type mem\_array is array(0 to 63) of reg\_data; type dat\_array is array(7 to 0) of reg\_data; type addr\_data is std\_logic\_vector(15 downto 0); type state\_type is (idle, run, stop, finish); type state\_type is (idle, out, stop, finish);

#### Which declarations are not correct and why?

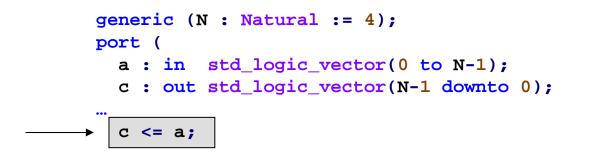

#### Ranges

The code is not correct, as the indexes of the two vectors have different directions

The code is correct, c(0) is connected to a(N-1)

The code is correct, c(0) is connected to a(0)

#### Constants

```

constant Nbits : Integer := 8;

constant Nwords : Natural := 6;

constant LowIdx : Positive := 0;

```

constant all0 : std\_logic\_vector(Nbits-1 downto 0) = (others => '0');

constant Tco : real := 5 ns; constant Tsetup : time := 2 ns; constant Thold : integer := 1 ns; constant Tdel : time := 3;

Which declarations are not correct and why?

#### **Concurrent assignments**

- y <= (a or b) and not c;

- y <= a or b and not c;

- y <= a and b or not c;

- y <= a and b and not c;

- y <= (a nor b) nor c;</pre>

- y <= a nor b nor c;</pre>

- y <= (a nand b) nand c;

- y <= a nand b nand c;</pre>

- y <= a xor b and c;

- y <= (a xor b) and c;

#### Which assignments are not correct and why?

# Conditional and selected assignments

y <= (a or b) when c ='0';

with a & b & c select

y <= '1' when "110"| "100"| "010",

'0' when "011"| "110",

'-' when others;</pre>

Why these assignments are not correct?

#### Generate

```

generic (N : Natural := 4);

port (

a : in std logic vector(N-1 downto 0);

g: in std_logic;

c : out std logic vector(N-1 downto 0) );

end for_gen;

architecture ... of for gen is

signal i : Integer;

begin

gn: for i in 0 to N-1 generate

c(i) \ll a(i) and g;

end generate;

The range must be exactly the same

incl. the direction (downto) as in the

declaration of c() and a()

?

The index i of c(i) and a(i) must be within

the limits 0...N-1

```

The declaration of *i* is necessary ? *i* is automatically declared within the **for...generate**

loop

#### The integer type

How many bits will be used to store the following integers:

| signal | my_int1 :            | Integer | range | -1  | to | 16; |

|--------|----------------------|---------|-------|-----|----|-----|

| 5      | 6                    |         | 4     |     |    |     |

|        |                      |         |       |     |    |     |

|        |                      |         |       |     |    |     |

| signal | <pre>my_int2 :</pre> | Integer | range | -32 | to | 2;  |

| 0      | 0                    |         | 7     |     |    |     |

| 6      | 8                    |         | 1     |     |    |     |

#### Mathematical operations with integers

```

process

variable byte : Integer range 0 to 16#FF#;

variable sint : Integer range -128 to 127;

variable word : Integer range 0 to 16#FFFF#;

variable intg : Integer range -2**15 to 2**15-1;

begin

```

| byte := | 20;              |

|---------|------------------|

| byte := | -20;             |

| sint := | -20;             |

| sint := | 150;             |

| word := | -1;              |

| word := | 1000** <b>2;</b> |

| word := | 16#1000#;        |

Which assignments are not correct and why?

#### Adder

```

LIBRARY IEEE;

USE IEEE.STD LOGIC 1164.ALL;

USE IEEE.STD LOGIC UNSIGNED.all;

entity adder is

generic (N : Natural := 8);

port (

cin: in std logic;

: in std logic_vector(N-1 downto 0);

а

: in std logic vector(N-1 downto 0);

b

cout: out std logic;

: out std logic vector(N-1 downto 0));

V

end adder:

architecture behav of adder is

signal sum : std logic_vector(N downto 0);

begin

sum <= cin + ('0' \& a) + ('0' \& b);

<= sum(y'range);

У

cout <= sum(sum'high);</pre>

end;

```

This adder was designed for adding two std\_logic\_vectors representing unsigned integers.

Can we use the generated hardware to add correctly **a** and **b** if they represent signed integers?

#### Signal VS. variable

| signal si : Integer range -7 to 7;<br>begin<br>process |      | Hint: the l | eft |

|--------------------------------------------------------|------|-------------|-----|

| variable vi : Integer range -7 to 7;                   |      | l <b>!</b>  |     |

| begin                                                  | SÌ   | vi          |     |

| si <= 0;                                               |      |             |     |

| vi := 0;                                               |      |             |     |

| si <= si + 1;                                          |      |             |     |

| vi := vi + 1;                                          |      |             |     |

| wait for 10 ns;                                        | 1 -6 | 1 -6        |     |

| si <= si + 1;                                          |      |             |     |

| vi := vi + 1;                                          |      |             |     |

| wait for 10 ns;                                        | -5 2 | -5 2        |     |

| si <= si + 1;                                          |      |             |     |

| vi := si;                                              |      |             |     |

| wait for 10 ns;                                        | -4 3 | -5-42       | 3   |

| wait;                                                  |      |             |     |

| end process;                                           |      |             |     |

lint: the leftmost is the initial value

Which is the correct value of si and vi after the waits?

#### DFF with asynchronous reset

```

process(clk, rst_n)

begin

if rst_n = '0' then q <= '0'; end if;

if clk'event and clk='1' then

q <= d;

end if;

end process;</pre>

```

Find the errors!

```

process(clk)

begin

if rst_n = '0' then q <= '0';

elsif clk'event and clk='1' then

q <= d;

end if;

end process;</pre>

```

```

process(clk, rst_n)

begin

if rst_n = '0' then q <= '0';

elsif clk'event and clk then

q <= d;

end if;

end process;</pre>

```

#### Decoder with enable

This entity is supposed to be a decoder with enable, but has a bug (syntax & compile is OK)

```

""

port (

a : in std_logic_vector(1 downto 0);

e : in std_logic;

y : out std_logic_vector(2 downto 0));

""

process(a, e)

begin

if a = "00" then y <= "00" & e;

elsif a = "01" then y <= '0' & e & '0';

elsif a = "10" then y <= e & "00";

end if;

end process;</pre>

```

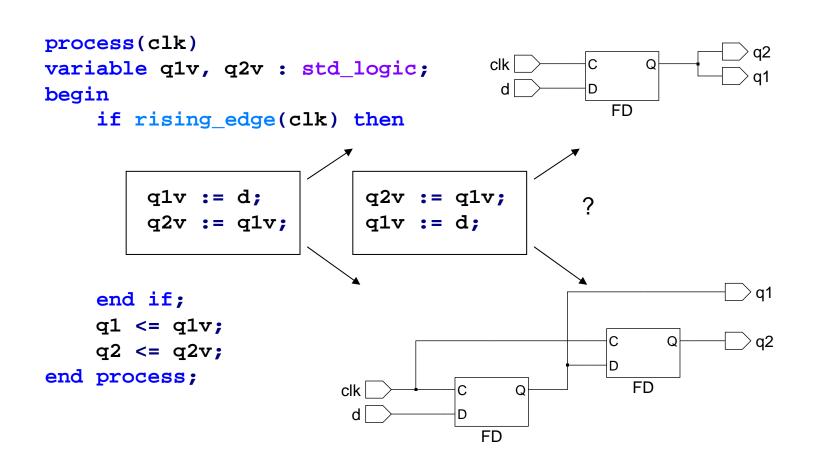

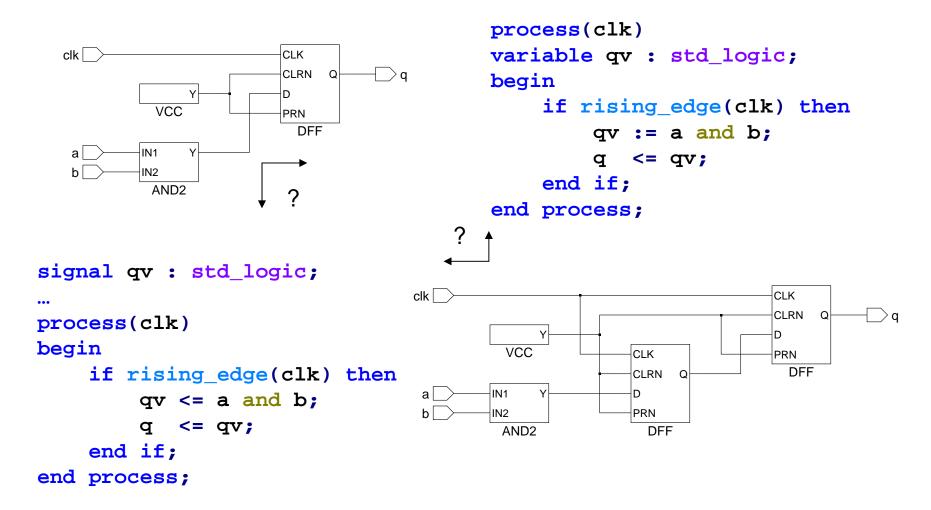

#### DFFs with variables(1)

#### DFFs with variables(2)

#### State machines in VHDL

```

type state_type is (S0, SL, SR, SA);

signal present st, next st : state type;

R

R

LL

> LL

begin

W

W

LR

>LR

process(present st, L, R, W)

clk

clk

begin

rst n

rst n

next st <= present st;</pre>

statem

case present_st is

when S0 => if W = '1' then next_st <= SA; LR <= '1'; LL <= '1';</pre>

elsif L = '1' then next st <= SL; LL <= '1';</pre>

elsif R = '1' then next_st <= SR; LR <= '1';</pre>

end if;

when SL => if L = '0' and R = '1' then next_st <= SR; LR <= '1'; LL <= '0';

else next st <= S0; LR <= '0'; LL <= '0';</pre>

end if;

when SR => if L = '1' then next st <= SL; LL <= '1';

else next st <= S0; LL <= '0'; LR <= '0';</pre>

end if;

when SA => next st <= S0; LL <= '0'; LR <= '0';

synthesis without

end case;

end process;

errors!

process(clk, rst n)

begin

rst n = '0'

then present st <= S0;

if

elsif clk'event and clk='1' then present st <= next st;

end if;

What is wrong in this description?

end process;

end;

```

#### State machine - encoding

- 1. A state machine with 5 states, encoded binary will have:

- a) 8 states in total

- b) 5 states in total

- c) 32 states in total

- 2. The same state machine encoded one-hot will have:

- a) 5 states in total

- b) 32 states in total

- c) 8 states in total

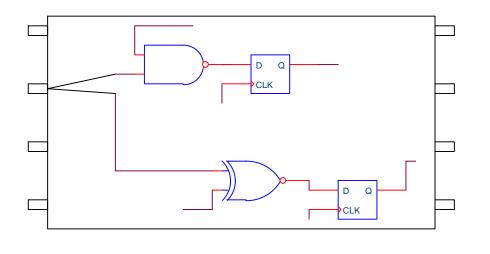

#### Synchronize input signals

Which one of the two schemes should be avoided and why?

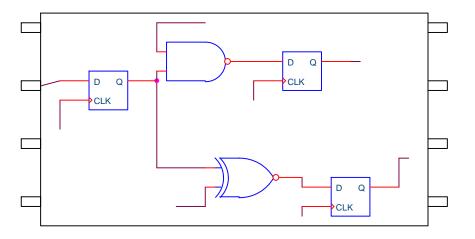

#### Simple test bench example

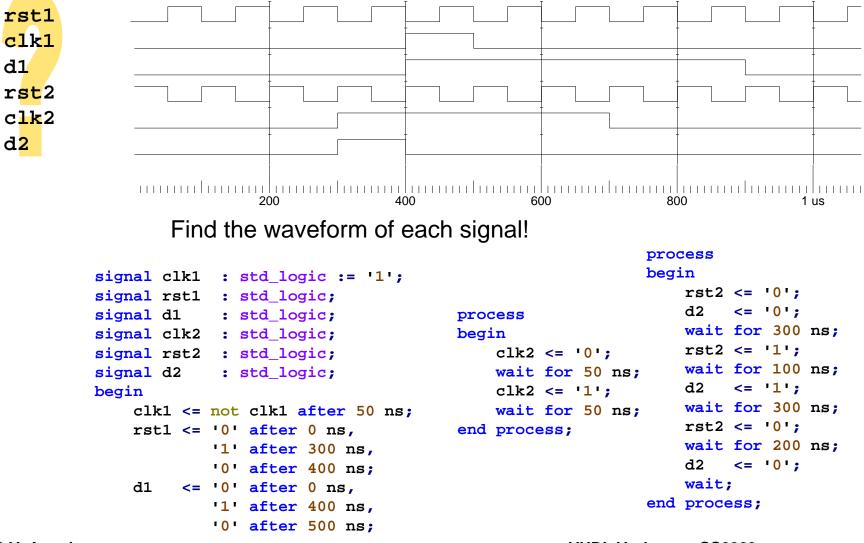

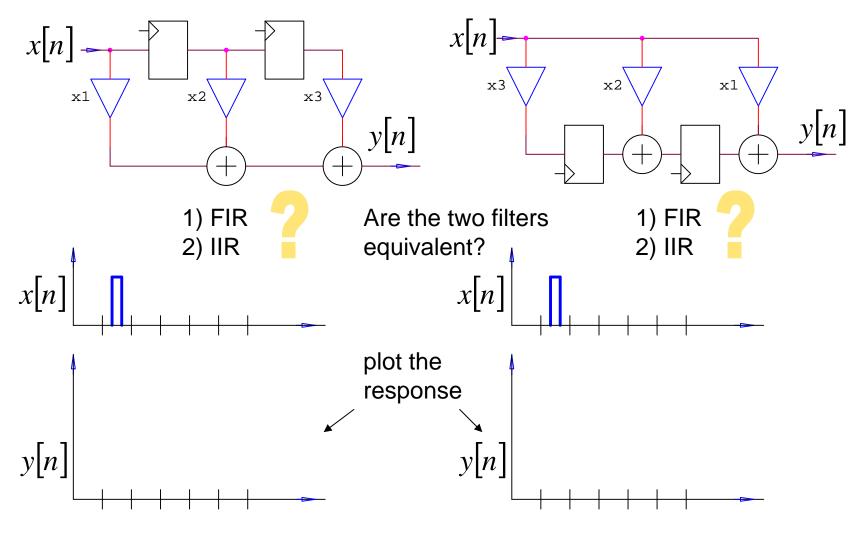

## Digital Filters(1)

#### Digital Filters(2)

#

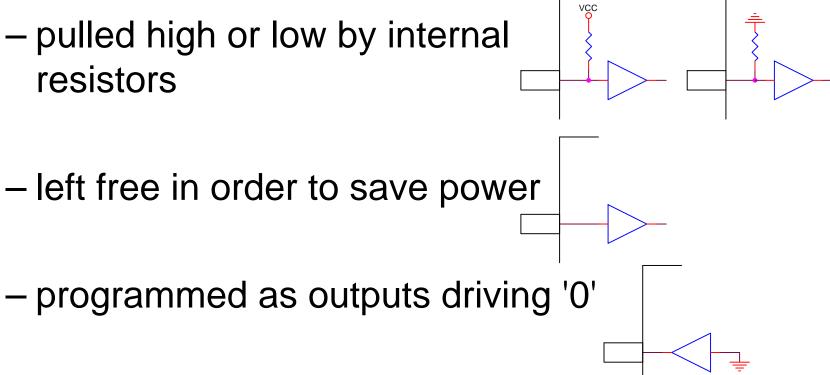

- The unused unconnected input pins should be

- pulled high or low by internal resistors

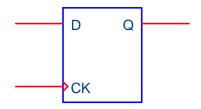

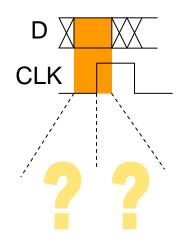

# Timing(1)

- Positive setup time means

- the D input must be stable some time before the rising edge of the clock

- the D input must be stable some time after the rising edge of the clock

- Positive hold time means

- the D input must be stable some time before the rising edge of the clock

- the D input must be stable some time after the rising edge of the clock

# Timing(2)

- The operation of a chip at 1 Hz can be affected by:

- setup time violations

- hold time violations

- The operation of a chip at 100 MHz can be affected by:

- setup time violations

- hold time violations

## Special cores, I/O timing

- In order to multiply the input clock by 5/7 we can use a

- PLL 7 – DLL

- In order to achieve identical setup/hold times on all bits of a synchronous 32-bit input bus we must first use the D-flip-flops

- in the core logic cells

- in the I/O cells