# Department of Physics and Astronomy

Heidelberg University

Master Thesis

in Physics

submitted by

Heiko Christian Augustin

born in Saarlouis

2014

(Updated: 19.06.2015)

# Characterization of a novel HV-MAPS Sensor with two Amplification Stages

#### and

### first examination of thinned MuPix Sensors

This Master Thesis has been carried out by

Heiko Christian Augustin

at the

Physikalischen Institut Heidelberg

under the supervision of

Prof. Dr. André Schöning

**Abstract** The Mu3e experiment searches for the lepton flavor violating decay  $\mu^+ \to e^+e^-e^+$  which is heavily suppressed in the Standard Model (SM) with a branching ratio below  $10^{-54}$ . The observation of a signal would be a clear sign for new physics. To achieve the projected sensitivity of 1 in  $10^{16}$  muon decays, background processes have to be suppressed below this level. Thus the experiment has to provide a good momentum, time and vertex resolution in an environment with muon decay rates up to  $\mathcal{O}(10^9~s^{-1})$ .

Due to the low energetic decay particles of maximal 53 MeV, multiple scattering in the detector components is limiting the momentum and vertex resolution. As a result the material budget of the detector has to be minimized. Therefore, the tracking detector consists of novel silicon detectors, fabricated in High-Voltage Monolithic Active Pixel (HV-MAPS) technology, which can be thinned down to  $50\mu m$ . This allows to reduce the material budget to  $\sim 1\%$  radiation length per tracking layer. The HV-MAPS technology incorporates active pixel sensors and readout electronics on a single chip and uses a depleted diode for fast charge collection.

In this thesis a framework was developed to test and characterize the MuPix6 HV-MAPS prototype which introduces a new two staged amplification scheme, aiming to amplify the signal pulses by a factor of 3 compared to previous prototypes. Besides, for the first time ever industrially thinned  $50\mu m$  MuPix4 sensors have been available for testing.

First characterization results from measurements in the laboratory and from testbeam campaigns with a 250 MeV pion beam are presented. A pixel signal-to-noise ratio (SNR) of 15 was determined for a Fe-55 equivalent signal and the chip time resolution was measured to be 16 ns. The MuPix6 performance is consistent with the performance of the previous MuPix4 prototype and provides a safety margin against digital cross talk through the enhanced signal. Further, thinned MuPix4 sensors have been tested and no significant performance impairment has been observed.

**Zusammenfassung** Das Mu3e Experiment sucht nach dem Leptonflavorzahl-verletzenden Zerfall  $\mu \to eee$ , welcher im Standard Model der Teilchenphysik mit einem Verzweigungverhältnis von weniger als  $10^{-54}$  sehr stark unterdrückt ist. Jedes beobachtete Signalereignis ist somit ein klares Zeichen für neue Physik. Um die angestrebte Sensitivität von einem in  $10^{16}$  Zerfällen erreichen zu können, müssen Beiträge von Hintergrundprozessen unter diese Schwelle reduziert werden. Somit muss der Detector eine sehr gute Zeit-, Impuls- und Vertexauflösung bereitstellen, bei bis zu  $10^9$  Myonzerfällen pro Sekunde. Aufgrund der niedrigen Energie der Zerfallsteilchen werden diese im Detektor Material stark gestreut, wodurch die Impuls- und Vertexauflösung begrenzt ist. Somit müssen die Detektorlagen möglichst dünn sein. Der Spurdetektor wird daher aus dünnen, neuartigen Siliziumsensoren gebaut, die sogenannten hochspannungsgetriebenen monolitischen aktiven Pixelsensoren (HV-MAPS), welche auf  $50\mu m$  Dicke gedünnt werden können. Somit reduziert sich die Materialmenge auf  $\sim 1\%$  Strahlungslänge. Die HV-MAPS Technologie kombiniert aktive Pixelsensoren und Ausleseelektronik auf einem Chip und benutzt eine in Sperrrichtung betriebene Diode zur Detektion ionisierende Strahlung, die eine schnelle Ladungssammlung garantiert.

In Rahmen dieser Arbeit wurde ein Testsetup entwickelt, um die MuPix6 Chips zu testen und zu charakterisieren. Im MuPix6 Prototyp wird eine neue zwei-stufige Signalverstärkung getestet, die das Signal um einen Faktor 3 zusätzlich verstärken soll. Außerdem können erstmals industriell gedünnte  $50\mu m$  MuPix4 Sensoren untersucht werden. Erste Charakterisierungsergebnisse aus Labor und Teststrahl Messungen werden vorgestellt. Ein Pixel-Signal-zu-Rausch-Verhältnis (SNR) von 15 wurde für ein auf Fe-55 geeichtes Signal gemessen und die Zeitauflösung des Chips zu 16 ns bestimmt. Der MuPix6 stellt ein mit den MuPix4 Prototypen vergleichbares SNR bereit und bietet zusätzlich eine Sicherheit gegen digitales Übersprechen auf Grund des erhöhten Signals. Desweiteren wurden gedünnten Chips untersucht und kein Einfluss des Dünnens auf das Chipverhalten festgestellt.

# **Contents**

| I | Int         | troduction                                                             | 1                     |  |  |  |

|---|-------------|------------------------------------------------------------------------|-----------------------|--|--|--|

| 1 | Intro       | Introduction                                                           |                       |  |  |  |

| 2 | The 2.1 2.2 | The Standard Model of Particle Physics                                 | 1<br>1<br>1<br>1<br>1 |  |  |  |

| 3 | The         | Mu3e Experiment                                                        | 1                     |  |  |  |

|   | 3.1         | The Experimental Situation - Searches for lepton flavor violating muon |                       |  |  |  |

|   |             | decays                                                                 | 1                     |  |  |  |

|   |             | 3.1.1 SINDRUM                                                          | 2                     |  |  |  |

|   |             | 3.1.2 MEG                                                              | 2                     |  |  |  |

|   |             | 3.1.3 Conversion Experiments                                           | 2                     |  |  |  |

|   | 3.2         | The Signal Decay                                                       | 2                     |  |  |  |

|   | 3.3         | The Backgrounds                                                        | 2                     |  |  |  |

|   |             | 3.3.1 Internal Conversion                                              | 2                     |  |  |  |

|   |             | 3.3.2 Accidental Background                                            | 2                     |  |  |  |

|   | 3.4         | The Detector Requirements                                              | 2                     |  |  |  |

|   | 3.5         | The Mu3e Detector                                                      | 2                     |  |  |  |

|   |             | 3.5.1 The Muon Beam & Stopping Target                                  | 2                     |  |  |  |

|   |             | 3.5.2 The Tracking Detector                                            | 2                     |  |  |  |

|   |             | 3.5.3 The Fiber Detector                                               | 2                     |  |  |  |

|   |             | 3.5.4 The Tile Detector                                                | 2                     |  |  |  |

|   | 3.6         | The Readout Concept                                                    | 2                     |  |  |  |

|   | 3.7         | The Cooling                                                            | 2                     |  |  |  |

| 4 | Inte        | raction with Matter and Detection of charged particles                 | 29                    |  |  |  |

| - | 4.1         | Interaction with Matter                                                | 2                     |  |  |  |

|   |             | 4.1.1 Heavy Particles                                                  | 2                     |  |  |  |

|   |             | 4.1.2 Electrons and Positrons                                          | 3                     |  |  |  |

|   | 4.2         | Multiple Coulomb Scattering                                            | 3                     |  |  |  |

|   | 4.3         | Particle Detectors                                                     | 3                     |  |  |  |

| 5 | Sem         | niconductor Physics                                                    | 3                     |  |  |  |

| - | 5.1         | Silicon                                                                | 3                     |  |  |  |

|   | 5.2         | Doping                                                                 | 3                     |  |  |  |

|     | 5.3<br>5.4<br>5.5               | PN-junction Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | Pixe 6.1 6.2 6.3                | Idetectors and the HV-MAPS technology43Pixel detectors45Monolithic active pixel sensors (MAPS)45High voltage monolithic active pixel sensors (HV-MAPS)466.3.1 The Concept466.3.2 The MuPix Prototypes46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11  | Se                              | tup 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

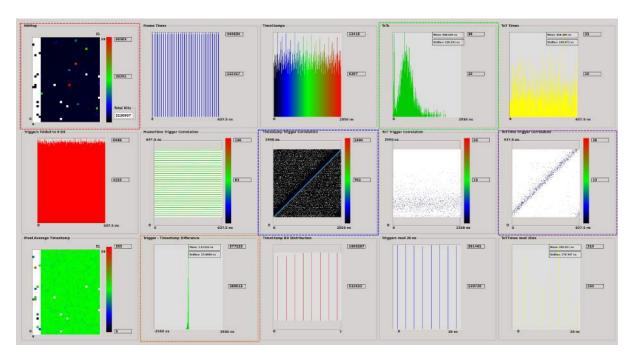

| 7   | 7.1<br>7.2<br>7.3<br>7.4<br>7.5 | Mupix       49         Mupix6       50         7.2.1 The Chip       50         7.2.2 The Pixel       50         7.2.3 The Digital Part       52         7.2.4 Signal Shaping       54         7.2.5 The Readout       55         7.2.6 The Sensor I/O       57         The Single Setup       59         7.4.1 The PCB       59         7.4.2 The FPGA       61         7.4.3 The Trigger System       61         7.4.4 The Mechanics       62         The Software       62         7.5.1 The FPGA Firmware       62         7.5.2 Graphical User Interface(GUI)       64         7.5.3 Data Format       65         7.5.4 Readout Software       66         Setup Improvements       66         7.6.1 Cable Cross Talk       67 |

| 8   | The                             | MuPix Telescope 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 111 | Me                              | easurements 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9   | <b>Mea</b> 9.1                  | Surements Methods & Setups         73           Measured Variables         73           9.1.1 The Hitbus         73           9.1.2 The Digital Hit Information         73           9.1.3 The Power Concumption         73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|    | 9.2   | Signal Sources                                                   | 5          |

|----|-------|------------------------------------------------------------------|------------|

|    |       | 9.2.1 Injection                                                  | 5          |

|    |       | 9.2.2 850 nm Infrared Laser                                      | 5          |

|    |       |                                                                  | 5          |

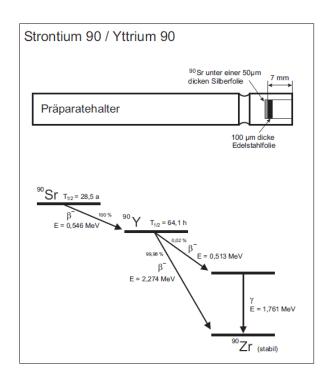

|    |       | 9.2.4 MeV Electrons from Strontium-90                            | 6          |

|    | 9.3   |                                                                  | 7          |

|    |       | -                                                                | 7          |

|    |       | •                                                                | 7          |

|    | 9.4   |                                                                  | 7          |

|    |       |                                                                  | 7          |

|    |       | 1                                                                | 9          |

|    |       |                                                                  | -          |

| 10 | Lab   | Characterization 8                                               | 1          |

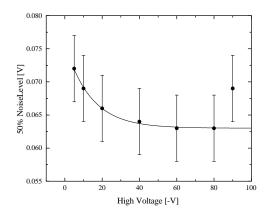

|    | 10.1  | Influence of HV                                                  | <i>i</i> 1 |

|    |       |                                                                  | 31         |

|    |       |                                                                  | 3          |

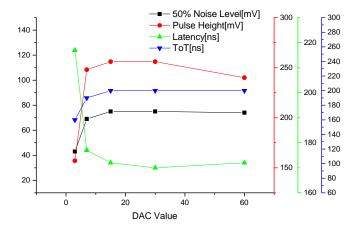

|    | 10.2  |                                                                  | 3          |

|    |       |                                                                  | 86         |

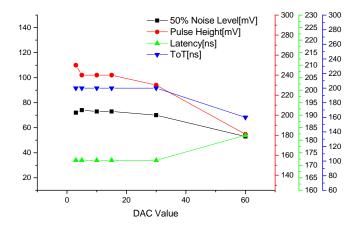

|    |       |                                                                  | 39         |

|    |       |                                                                  | 1          |

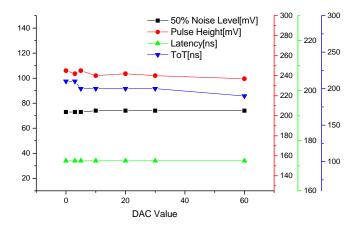

|    |       |                                                                  | )2         |

|    |       |                                                                  | 96         |

|    |       | 1                                                                | 9          |

|    |       | 10.8.1 SNR and Noise                                             | 9          |

|    |       | 10.8.2 Tuning                                                    | 1          |

|    | 10.9  | The Detection Diode                                              |            |

|    |       | 10.9.1 Measurement Setup                                         | )4         |

|    |       | 10.9.2 The U-I-Diagram                                           |            |

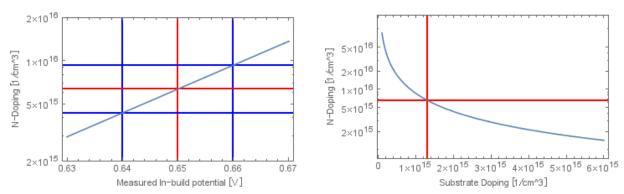

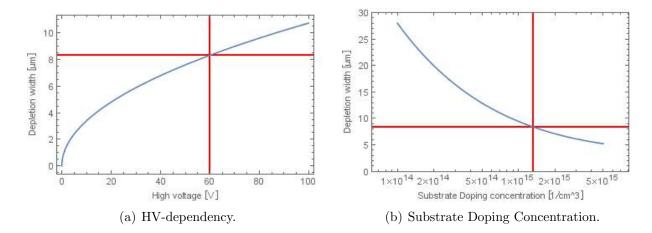

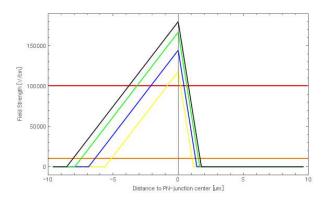

|    |       | 10.9.3 Reverse Engineering of the N-Well Doping Concentration 10 |            |

|    | 10.10 | OThinned Mupix4 Observations                                     |            |

|    |       |                                                                  |            |

| 11 | Test  | beam Characterization 10                                         | 9          |

|    |       | Testbeam Campaigns                                               | 9          |

|    |       | Setups                                                           | 0          |

|    |       | 11.2.1 July Testbeam                                             | .1         |

|    |       | 11.2.2 October Testbeam                                          | 2          |

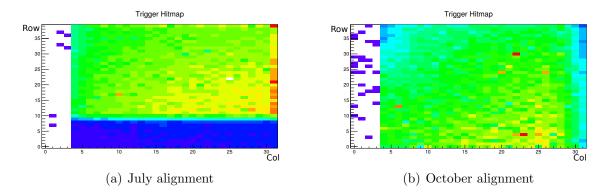

|    | 11.3  | Mechanical Alignment                                             | 2          |

|    |       | Measurements                                                     | .3         |

|    |       | Data Sets                                                        | 4          |

|    |       | 11.5.1 July                                                      |            |

|    |       | 11.5.2 October                                                   |            |

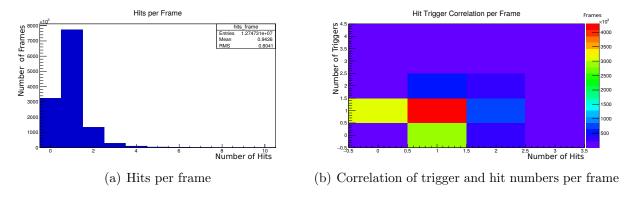

|    | 11.6  | Data Quality                                                     |            |

|    |       | Data Analysis                                                    |            |

|    |       | 11.7.1 Time Resolution Chip                                      |            |

|    |       | 11.7.2 Single Pixel Time Resolution                              |            |

|    |       | 11.7.3 Timewalk                                                  |            |

| IV | Discussion                                                                               | 123                      |

|----|------------------------------------------------------------------------------------------|--------------------------|

| 12 | Discussion & Summary         12.1 Discussion          12.2 Summary          12.3 Outlook | 125<br>125<br>126<br>126 |

| V  | Appendix                                                                                 | 127                      |

| Α  | Additional Plots                                                                         | 129                      |

| В  | Bibliography                                                                             | 137                      |

| С  | Lists C.1 List of Figures                                                                | <b>141</b><br>141<br>144 |

# Part I Introduction

#### 1 Introduction

Today's knowledge about particle physics is summed up in the Standard Model, which describes all known elementary particles and their interactions. In spite of its precise experimental predictions, it leaves many phenomena unexplained, e.g. the nature of gravity or the mass hierarchy. The lag of prediction for these open questions triggers the development of new theories giving rise to new phenomena not described by the Standard Model. Since non of these effects has been observed so far, the mass scale at which new physics comes into play is currently beyond our reach.

However, there are two approaches to search for new physics phenomena. One is the direct search for new physics in the form of new particles or processes at the high energy frontier by increasing the energy of colliders further, e.g. at the Large Hadron Collider (LHC). Although the direct observation of those new phenomena could only be performed at high energies, due to the quantum nature of particle physics their presence also manifests as small deviations from standard model predicted values for well known quantities, since they can enter in loops and enhance the branching ratios for rare standard model decays. As those measurements often require sub-parts-per-billion precision, they also necessitate large data samples.

The MU3E experiment is a proposed precision experiment searching for the lepton flavor violating decay  $\mu \to eee$  with a branching fraction sensitivity of  $1 \times 10^{-16}$  at 90% confidence level [1].

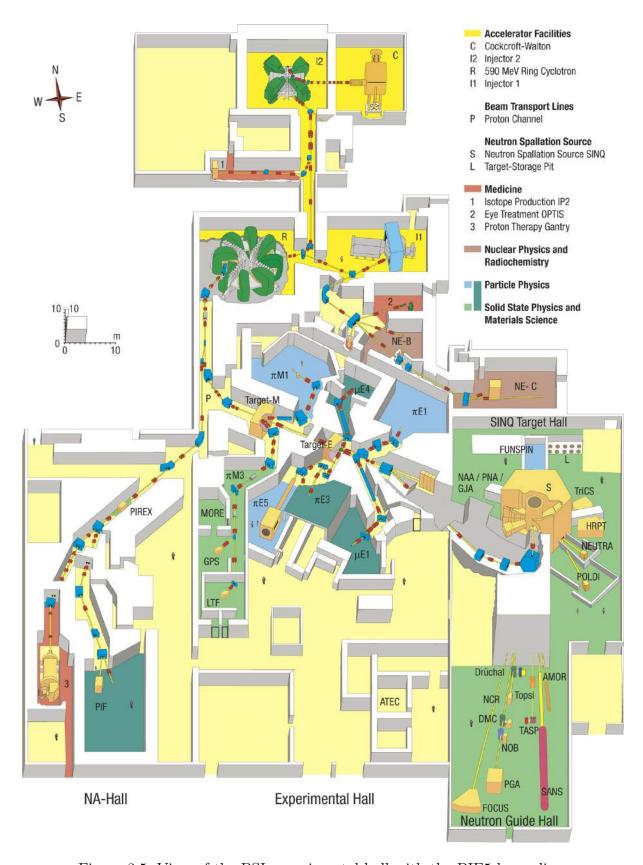

To reach this goal in a reasonable amount of time the experiment needs to observe  $2 \times 10^9$  muon decays per second, which are provided by stopping a muon beam on a target produced at the High Intensity Proton Accelerator (HIPA) at the Paul Scherrer Institut(PSI) in Switzerland. The detector is made up of cylindrical layers of pixel, fiber and tile detectors along the beam axis, which forms a spectrometer with a very good vertex, momentum and time resolution.

As the maximum momentum of the decay particles is fixed to 53 MeV, half the muon mass, multiple coulomb scattering is a very dominant effect and constrains the material budget of the detector to achieve a good momentum resolution.

To meet this constrain, very thin layers of silicon pixel detectors are necessary without impairments on their performance. The technology which was proven in the past to have a very high potential and suitability for this experiment are pixel sensors called HV-MAPS produced in commercial high voltage CMOS processes. This technology combines the advantages of producing detector and readout on the same chip (MAPS) with a depleted diode as active detector volume. As for this process the thickness of the depletion layer is around 10  $\mu$ m the bigger part of the wafers depth is unused and allows to thin the sensors down to 50  $\mu$ m thickness including metal layers.

In the following the characterization results obtained for the MuPix6 prototype as well as for the first industrially thinned MuPix4 sensors are presented. The setup and the prototypes have been tested as well in the lab as on testbeam campaigns at PSI with a 250 MeV pion beam which allows precise timing measurements and also efficiency determination with the recently developed MuPix telescope.

The MuPix6 prototype introduces a new amplification scheme consisting of two amplification stages instead of one as for previous prototypes. The pulses created by the pixel electronics are investigated with respect to their dependencies of the high voltage and the bias voltages. The power consumption of the chip is measured and an optimisation of the bias voltage settings to reduce the power consumption is performed. The signal-to-noise ratio (SNR) of the new pixel architecture is determined and scattering of pixel properties is discussed. Further the time resolution of the chip is measured from testbeam data for the chip as whole and for a single pixel.

Good SNR values and pixel behaviors have been found for the MuPix6 amplification scheme, which can be compared to the values obtained for MuPix4. This comparison reveals a amplification factor of  $\sim 3$  for the second amplification stage as expected, creating a safety margin against digital cross talk for high frequency signals.

Furthermore the first industrial thinned chips have been investigated in parallel, showing no influence of the thinning process on the chips performance.

## 2 Theory

#### 2.1 The Standard Model of Particle Physics

The Standard Model of Particle Physics (SM) is a quantum field theory describing the fundamental constituents of matter and their interactions. It consists of twelve fermionic elementary particles, their anti-particles and six bosons. Three fundamental interactions are described by the electro-magnetic, weak and strong interaction. Gravitation can not be included in the SM, but can be ignored as its effect is negligible compared to the other interactions.

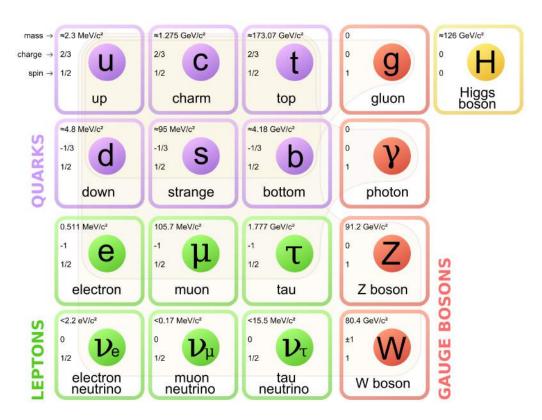

Figure 2.1: The elementary particles in the Standard Model of Particle Physics [2].

The elementary particles are described and ordered by their mass and quantum numbers: spin, electric charge, weak hyper charge, color charge and flavour quantum numbers. This splits the twelve fermions into six particles carrying color charge, the quarks and 6 leptons without color charge. Quarks and leptons are arranged in three families or generations ordered by their mass.

Each generation of quarks contains an up-type and a down-type quark in rising mass order. The up-type quarks up (u), charm (c) and top (t) carry +2/3 electrical charge (in

elementary charges e), the down-type quarks down (d), strange (s) and bottom (b) carry -1/3 e. They also interact weakly and electro-magnetic.

There are three charged leptons: the electron (e), the muon ( $\mu$ ) and the tau ( $\tau$ ). They carry charge -1 but no color charge and can interact weakly and electro-magnetic. A lepton family is build from a charged lepton and its corresponding neutral lepton, the so-called neutrino ( $\nu$ ). E.g. the first family consists of the electron, the lightest charged lepton and the electron-neutrino ( $\nu_e$ ). The neutrinos are massless in the SM and only interact weakly.

In the SM the forces are mediated by five gauge bosons. The photon  $(\gamma)$  is the mediator for the electro-magnetic interaction (EM), which couples to electric charge and is massless. The weak interaction is mediated by three massive gauge bosons, two charged  $(\pm 1)$  W-bosons with 80.4 GeV mass and the neutral Z-boson with 91.2 GeV mass. The strong interaction is described by the theory of quantum chromo dynamics (QCD), with its force carrier the massless gluon which couples to color charge and also carries color charge itself. In the SM the electro-magnetic and weak interaction can be unified and treated as a single interaction the electro-weak interaction with 4 massless gauge bosons. As the weak gauge bosons are massive there must be a process causing electro-weak symmetry breaking, which breaks this single interaction into two and gives mass to the weak gauge bosons. This process is the higgs-mechanism for the SM, which comes along with the prediction of an additional neutral scalar particle called the higgs-boson.

Whereas the range of the EM is infinite due to the zero mass of the photon, the strong force is very short ranged due to the color charge of the gluon which enables self-interaction. A further consequence is the absence of free color charged objects in nature, the so-called confinement, binding multiple quarks and gluons in color-free states (hadrons). The range of the weak force is even shorter due to the high mass of the gauge bosons and renders it the weakest force in the SM at energy scales below their masses.

Not all particle quantum numbers are good quantum numbers and conserved for all interactions. E.g. the weak force does not conserve the quark flavor, due to the fact that weak-eigenstates are superpositions of strong-eigenstates. The mixing between strong and weak quark-eigenstates is formulated in the Cabibbo-Kobayashi-Maskawa-Matrix (CKM-Matrix). In the SM a lepton flavor number is assigned to each lepton family and was assumed to be conserved, until recent observations of neutrino-oscillation showed a lepton flavor violation (LFV) in the neutrino-sector [3–5]. This required an extension of the SM including neutrino-oscillation effects, implying a none-zero mass for neutrinos. The neutrino mixing is summed in the Pontecorvo-Maki-Nakagawa-Sakata matrix (PMNS) describing the mixing of weak and mass eigenstates of the neutrinos. So far for charged leptons no flavor violation (cLFV) has been observed.

Although the SM is one of the most successful theories of modern physics and its predictions have been tested and confirmed in many measurements at last with the discovery of a higgs boson at LHC [6][7], it still leaves many open questions. Neither does it include a dark matter candidate, nor does it include a quantum theory of gravity, nor does it give an explanation for the matter-antimatter asymmetry observed in the universe. Neutrino masses as measured in neutrino-oscillation can be integrated in extended SMs, but does not explain how the neutrino masses are generated.

This triggers the development of new theories beyond the SM, predicting new particles and interactions not observed at the currently available energy regime.

#### 2.2 The Muon Decay

#### 2.2.1 In the Standard Model

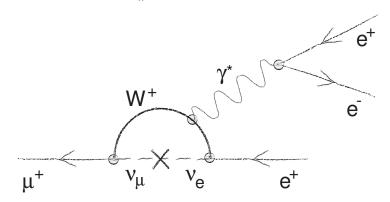

In the original SM the lepton number is a conserved quantity and lepton flavor violating decays as e.g.  $\mu \to eee$  are forbidden. Although the extended SM still does not describe charged lepton flavor violation on tree-level, lepton mixing can be induced here by neutrino oscillation in higher order loop diagrams. However, for the most dominant loop-diagram (fig. 2.2) for  $\mu \to eee$  the branching ratio (BR) is heavily suppressed to  $BR < 10^{-50}$  by the mass ratio  $(\frac{(\Delta m_{\nu}^2)^2}{m_W^4})$ .

Figure 2.2:  $\mu \to eee$  SM-neutrino oscillation diagram.

A further related decay, possible through the same loop, is the neutrinoless radiative decay  $\mu \to e\gamma$ , which only differs from  $\mu \to eee$  by the missing photo conversion and so renders a slightly less suppressed BR mainly driven by the missing EM-vertex entering with a factor  $\alpha_{em}(\mathcal{O}(10^{-2}))$ .

These extremely low BR predictions render these decays experimentally immeasurable and make them a perfect test ground for the SM, as any observed signal is a clear sign for physics beyond the SM.

#### 2.2.2 Beyond the Standard Model

Although the charged lepton flavor is practically conserved in the SM, many models of beyond the SM theories include cLFV and therefore give an enhanced BR for processes as e.g.  $\mu \to eee$ . Those models are constraint by the limits obtained experimentally  $BR < 10^{-12} \ (\mu \to eee)$  [8] and related processes, e.g.  $\mu \to e\gamma$  covering cLFV processes.

Beyond the SM theories with more dimension or an extended higgs-sector predict heavy particles which can couple to both electrons and muons, leading to LVF already at tree level as shown in figure 2.3(b). The large mass of the mediating new particle leads to a suppression of this process.

One possibility to induce enhancements on the loop-level is given by supersymmetric theories which predict loops containing supersymmetric particles as in figure 2.3(a) and create LFV via slepton mixing. As no supersymmetric particle has been observed so far they must come into play at higher mass scales. These loop diagrams are usually suppressed if the mass of the supersymmetric particles, determined by the SUSY scale parameters are large.

(a) Beyond SM  $\mu \to eee$  process with loop slepton (b) Tree diagram for heavy mediator particle. mixing (SUSY).

Figure 2.3: Beyond the SM diagrams.

# 3 The Mu3e Experiment

The Mu3e experiment searches for the lepton flavor violating decay  $\mu^+ \to e^+ e^- e^+$  with a precision of better than one in  $10^{16}$  muon decays. To achieve this goal on a suitable time scale the experiment is designed to observe  $2 \times 10^9$  muon decays per second.

In the following the challenges of the Mu3e experiment, the detector solution, as well as the current experimental situation of searches for lepton flavor violation are depicted.

# 3.1 The Experimental Situation - Searches for lepton flavor violating muon decays

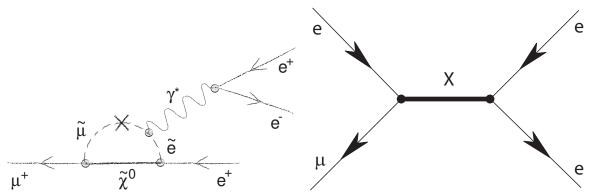

Figure 3.1: Present and aimed limits of past, present and future searches for LFV decays. Adapted from [9].

#### **3.1.1 SINDRUM**

The SINDRUM experiment searched for the decay  $\mu^+ \to e^+e^-e^+$  from 1983-1986. In the absence of a detected signal an upper limit of  $BR < 10^{-12}$  at 90% confidence level (CL) could be derived [8].

The SINDRUM experiment was operated at PSI, stopping 28 MeV/c surface muons on a double cone target, placed in a 0.33 T magnetic field. To track the decay products, the target was surrounded by 5 layers of multi wire proportional chambers and a trigger hodoscope. The main background source arose from  $\mu^+ \to e^+ e^- e^+ \bar{\nu}_\mu \nu_e$  and was estimated to  $5 \times 10^{-14}$ . That shows the results limitation due to the number of observed muon decays.

#### 3.1.2 MEG

The MEG experiment is a current experiment running at PSI since 2008 searching for the LFV process  $\mu \to e\gamma$ . The main detector components are a drift chamber for the positron reconstruction and a liquid xenon calorimeter for the photon detection [10].

In a first run with  $10^{14}$  stopped muons a limit could be set to  $BR < 2.8 \times 10^{-11}$  at 90% CL. After improvements this limit has been improved to  $BR < 5.7 \times 10^{-13}$  at 90% CL [11]. A further upgrade is ongoing, aiming to reach a BR sensitivity of  $10^{-13}$ . This challenges the search for  $\mu \to eee$  to achieve BR sensitivities better than  $10^{-15}$  to be competitive.

#### 3.1.3 Conversion Experiments

An other possibility is the search for LVF in muon conversion  $\mu \to e$  in the presence of nuclei. It has the advantage of a clear signature of monochromatic electrons, with an energy not occurring in normal muon decays.

The best limit is set by the SINDRUM II experiment for the conversion on a gold target  $\mu Au \rightarrow eAu$  ( $BR < 7 \times 10^{-13}$ ) [12]. New experiments on muon conversion are planed with Mu2e at Fermilab or DeeMe, COMET and PRISM at J-PARC they aim for BR sensitivities of  $10^{-14}$  to  $10^{-16}$ .

#### 3.2 The Signal Decay

The  $\mu^+ \to e^+e^-e^+$  decay is a prompt decay, so the decay particles originate from a common vertex. As a consequence of momentum conservation the vectorial sum of the particle momenta is vanishing for muon decays at rest:

$$|\vec{p}_{tot}| = |\sum_{i=0}^{2} \vec{p}_i| = 0$$

(3.1)

Moreover the total energy has to add up to the muon mass:

$$E_{tot} = |\sum_{i=0}^{2} E_i| = m_{\mu} \cdot c^2 \tag{3.2}$$

The maximum energy of a decay particle is therefore given by half the muon mass  $\sim 53~MeV$ .

To discriminate between signal and background kinematics can be exploited by requiring momentum and energy conservation. In addition the coincidence of the particles in space and time can be used for discrimination.

#### 3.3 The Backgrounds

The backgrounds for the signal can be divided in two categories, irreducible physics background and accidentals.

#### 3.3.1 Internal Conversion

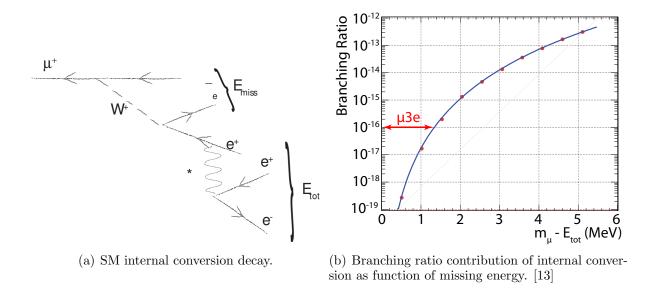

The physics background is mainly given by the SM internal conversion decay  $\mu \to eee\bar{\nu}\nu$  (fig. 3.2(a)). Here the undetected neutrinos give rise to missing energy and momentum allowing a discrimination from the signal decay. Figure 3.2(b) shows the missing energy for a range of target sensitivities. To achieve a BR sensitivity better than  $10^{-16}$  at 90% CL an energy resolution better than 1 MeV is required [1].

Figure 3.2: Internal Conversion.

#### 3.3.2 Accidental Background

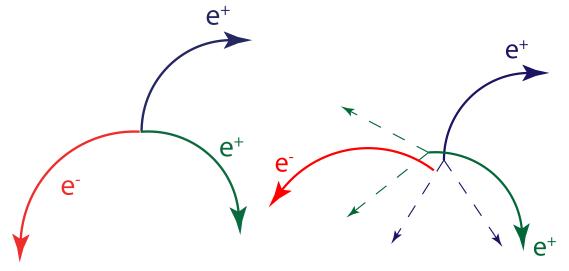

Accidental background can arise from event topologies as shown in 3.3(b), with e.g. two positrons from SM michel decays and an electron from a different process. The regular production of electrons in an anti-muon decay is already covered by the internal conversion background. Further origins of electrons are either caused by misreconstruction in a very crowded detector environment or by secondary interactions as photon conversion in the

(a) Signal topology: two positrons and one (b) Fake signal closely resembling the signal topolelectron with common vertex. ogy.

Figure 3.3: Three track topologies.

target from radiative decays  $\mu \to \gamma e \nu \bar{\nu}$  or bhabha-scattering of a michel positron with an electron.

For the Mu3e experiment requiring  $\mathcal{O}(10^9)$  muon decays per second on the target this is a serious background source and needs to be suppressed as good as possible. Here the space and time coincidence of the signal can be used for discrimination by requiring same vertex and time origin for all decay particles (fig. 3.3(a)).

#### 3.4 The Detector Requirements

As seen above the aim to achieve a BR sensitivity of  $10^{-16}$  poses a lot of requirements in terms of background suppression and rate capability, which directly translate to detector requirements.

In order to accomplish the experimental goals on a suitable timescale the detectors acceptance and efficiency has to be as high as possible. The detector has to provide excellent vertex, time and momentum resolution to suppress the emerging background to a level below  $10^{-16}$ . Further the low energy of the decay particles demands a small material budget to reduce multiple coulomb scattering which dominates the momentum resolution.

#### 3.5 The Mu3e Detector

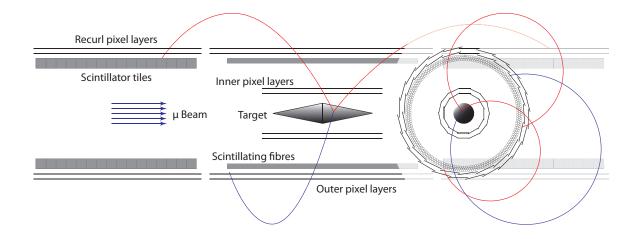

The basic idea of the Mu3e experiment is to stop more than  $10^{16}$  on a target and observe their charged decay particles with a barrel detector surrounding the target. The detector is made of layers of high granular silicon detectors for tracking and scintillating fiber, and tile detectors for precise time measurements. To measure the momentum of the

Figure 3.4: Schematic compilation of the Mu3e detector with an on-target  $\mu^+ \to e^+e^-e^+$  decay. On the right a view along the beam axis [14].

charged particles the detector is placed in a 1 Tesla homogeneous magnetic field. As multiple coulomb scattering is the most severe error source the material budget has to be minimized as much as possible. The detector is cooled with a constant flow of gaseous helium, which guarantees good heat transfer and low multiple scattering.

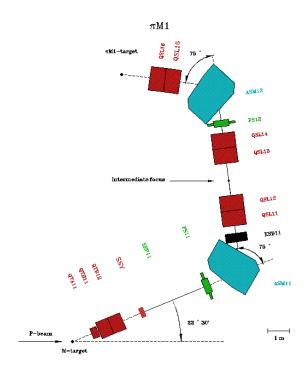

#### 3.5.1 The Muon Beam & Stopping Target

Since at the moment there is no muon beam existing which could provide  $2 \times 10^9$  muon stops per second, the experiment is planned to run in two phases. In phase I the experiment will make use of the beam line  $\pi e5$  at the High Intensity Proton Accelerator (HIPA), see figure 3.5. The HIPA cyclotron provides a 2.2 mA beam of 590 MeV protons striding two rotating targets. The  $\pi e5$  beam is extracted from the carbon target E by collecting muons which originate from pions at rest on the targets surface (surface muons), generating a 28 MeV/c muon beam. For phase II a new beam line needs to be constructed. Currently a study is ongoing determining possible solutions for a high intensity muon beam (HIMB) at PSI. The possibility of a target upgrade seems most feasible at the moment. To stop the muons the beam hits a hollow double cone target made of a thin aluminum or mylar foil  $(\mathcal{O}(50\mu m))$ .

Figure 3.5: View of the PSI experimental hall with the PIE5 beam line.

#### 3.5.2 The Tracking Detector

The tracker is subdivided in five units: the central barrel surrounding the target and two pairs of recurl stations up- and downstream respectively. In phase I at first only the central barrel will be installed (phase Ia), consisting of an inner and outer double layer of pixel sensors. The inner double layer is closest to the target and used for vertexing. The outer layers are in farther distance and allow to measure the bending of particle tracks in the magnetic field and allows for a momentum measurement. The momentum determination can be improved further by measuring the second intersection of the particles with the outer layers when recurling in the 1 Tesla magnetic field. To increase the detectors acceptance for the recurl measurement, the outer double layers are extended by adding recurl tracking layers upstream and downstream from the central station (phase Ib, II).

The detector consists of two types of sensor reticles,  $2 \times 6cm^2$  sensors for the inner layers and  $2 \times 18cm^2$  for the outer layers. The layers are build as regular polygons with side lengths of 1 or 2 cm housing several sensors. In the end the detector will have more than  $1m^2$  of active pixelated surface and consist of about 275 million pixels with a pitch of  $80 \times 80\mu m^2$ .

(a) Prototype of a self supporting inner (b) Outer layer prototype with V-folds for layer with 50  $\mu m$  glass as silicon substitute. mechanical stabilization.

Figure 3.6: Prototypes of the self-supporting capton layers.

To achieve the goal of a minimal material budget, the tracking layers are build self supporting from  $50\mu m$  silicon sensors glued to  $25\mu m$  thick Kapton® foil. Additionally the sensors are wire bonded to a flex print manufactured from a  $25/25\mu m$  Kapton®/aluminum laminate (fig. 3.6(a)&3.6(b)), which provides power, slow control steering and sensor readout via 800 MBit/s Low Voltage Differential Signals (LVDS).

#### 3.5.3 The Fiber Detector

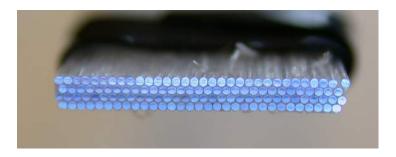

The fiber detector consists of ribbons made of 2-3 layers of stacked and glued  $250\mu m$  scintillating fibers, placed polygon just inside the outer double pixel layer. They are read out with an array of silicon photo multipliers (SiPM) matched to the fibres. This system provides  $\mathcal{O}(1ns)$  time resolution for all tracked decay particles and central barrel recurlers. This is needed to handle the high multiplicities and suppresses the accidental background.

Figure 3.7: Ribbon manufactured from 4 layers of glued round scintillating fibers [1].

#### 3.5.4 The Tile Detector

Figure 3.8: Rendering of one tile detector station consisting of many scintillating tiles [1].

To improve the matching of recurling tracks in the upstream and downstream stations and suppress background especially in phase II a very good time resolution is required. This is achieved by a tile detector consisting of a barrel of segmented scintillating tiles inside the diameter of the outer pixel layers. Each tile is connected to a SiPM and is sampled via a two threshold discriminator which allows to perform time walk corrections and through this gain  $\mathcal{O}(100ps)$  resolutions.

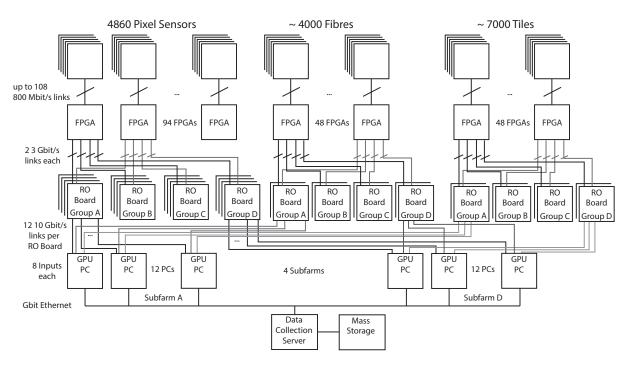

#### 3.6 The Readout Concept

All detector parts are steered and readout by field programmable gate arrays (FPGA). The FPGAs collect the data from the subdetectors and send the data to a front-end card sorting the data time ordered and assigning the time slices to a graphic processing unit (GPU). Each time slice contains the complete detector information used for online reconstruction. The detector produces more than 100 GB/s of raw data, after sorting, online reconstruction and filtering 100 MB/s of data remain which are stored on tape.

Figure 3.9: Readout concept and data flow chart of the Mu3e experiment [15].

### 3.7 The Cooling

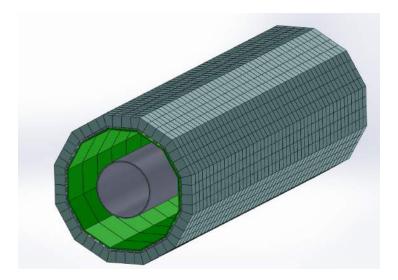

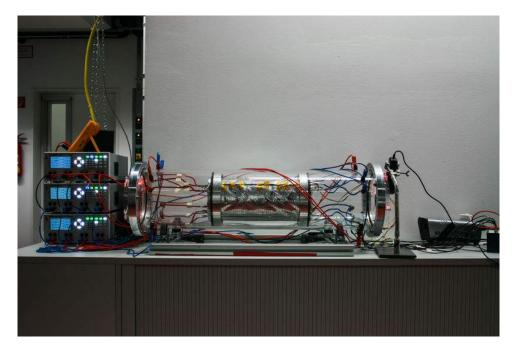

All electrical components in the detector produce heat. Most heat originates from pixel sensors. To cool the detector efficiently it is placed in a gaseous helium atmosphere with a constant flow along the beam axis, making use of the good heat transfer and low multiple scattering properties of helium. The cooling capabilities of the gaseous helium constrains the power consumption for the tracking detector. The cooling is currently simulated and tested with a mock-up of the central station and the capability seems to exceed the goal set for the experiment  $(150 \, \mathrm{m \, W})$  giving a safety margin .

Figure 3.10: The cooling mock-up used at the Physics Institute the test the cooling capability of a global flow along the beam axis [16].

# 4 Interaction with Matter and Detection of charged particles

The interaction of particles with matter allows their detection in the first place, but of course it also gives rise to scattering effects, which are pre-dominantly error sources for the Mu3e experiment. In the following the interaction of charged particles with matter are discussed with emphasis to the energy deposition used for their detection and the scattering angle distribution for a particle penetrating through a layer of matter.

#### 4.1 Interaction with Matter

The interaction of charged particles with matter depends heavily on the atomic number of the material and also on the particles charge and mass. Especially electrons and heavy particles are distinguished, as for the heavy particles bremsstrahlung only comes into play at very high energies. In the following only energy losses due to electro-magnetic interactions are considered; hadrons can also interact via the strong interaction.

#### 4.1.1 Heavy Particles

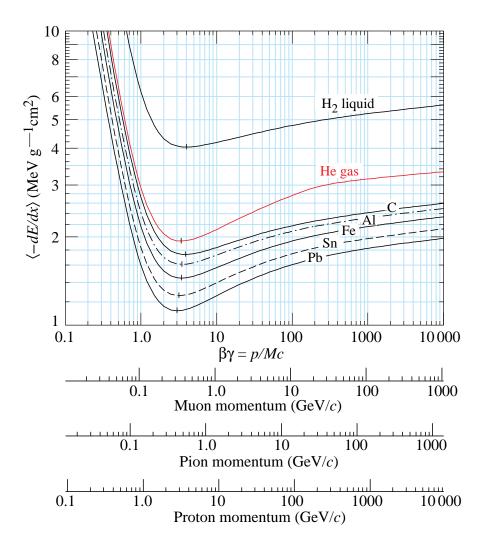

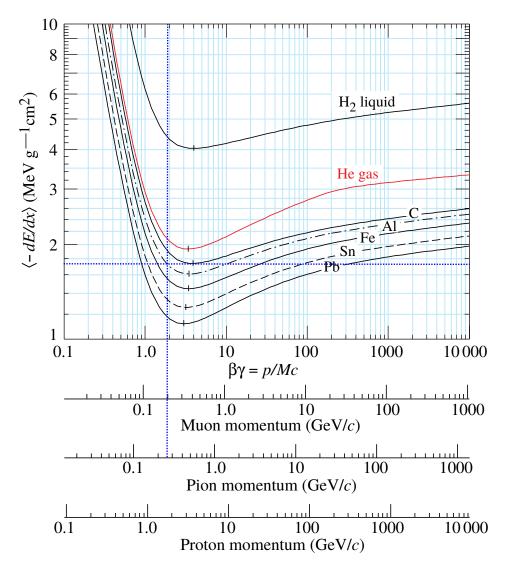

For particle physics the most important heavy particles are muons, pions and protons. For them the most important energy loss is ionization up to GeV energies. The mean energy loss per traveled material thickness  $\langle \frac{dE}{dx} \rangle$  is described by the Bethe-Bloch-formula (4.1) [17].

$$-\left\langle \frac{dE}{dx} \right\rangle = \frac{4\pi n z^2}{m_e c^2 \beta^2} \cdot \left(\frac{e^2}{4\pi \epsilon_0}\right)^2 \cdot \left[ \log\left(\frac{2m_e c^2 \beta^2}{I \cdot (1 - \beta^2)}\right) - \beta^2 \right] \tag{4.1}$$

with the particle dependent parameter: the relative velocity  $\beta = \frac{v}{c}$ , the charge number z, the material dependent mean excitation energy I and the electron density n. Further the electron mass  $m_e$ , the speed of light c and vacuum permittivity  $\epsilon_0$ .

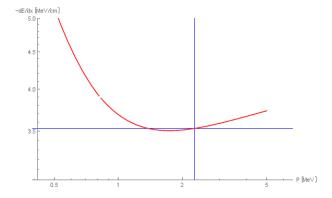

The Bethe-Bloch-formula as plotted in figure 4.1.1 shows a minimum around  $\beta\gamma=\frac{pc}{m_0c^2}\approx 3$  for all materials, indicating a minimal energy loss for particles with the corresponding momenta. Those are referred to as Minimum Ionising Particles (MIP). For lower momenta the losses rise with  $\beta^{-2}$  due to the rising interaction time, for higher momenta the energy losses increase logarithmically on account of the relativistic squeezing of the transversal fields.

Figure 4.1: Mean energy loss of heavy particles described by the Bethe-Bloch formula for different materials [17].

#### 4.1.2 Electrons and Positrons

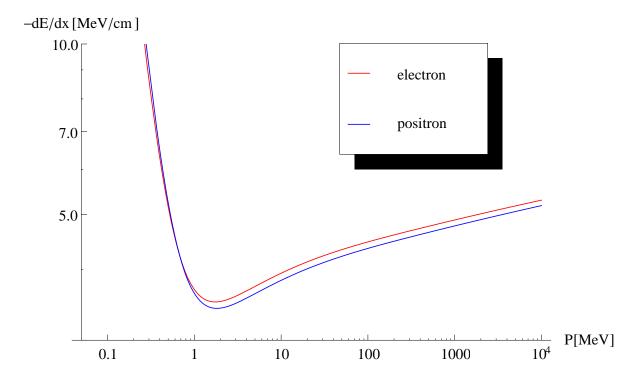

The two main sources of energy loss for positrons and electrons are ionization and contrary to heavy particles bremsstrahlung. The mean energy loss via ionization is well described by Berger and Seltzer [18], the Berger-Seltzer-formula (4.2):

$$-\left\langle \frac{dE}{dx} \right\rangle = \rho \frac{0.153536}{\beta^2} \frac{Z}{A} \cdot \left( B_0(T) - 2\log(\frac{I}{m_e c^2}) - \delta \right) \tag{4.2}$$

The energy loss depends on the material and momentum dependent stopping power  $B_0(T)$ , the material dependent mean excitation energy I, density correction  $\delta$ , atomic number Z, mass number A and material density  $\rho$ . Further it takes into account the indistinguishability of incident and scattering electrons in contrast to the positron, which leads to different energy losses. With the help of the provided data [18] one can find a description for various materials in a large energy range. The energy loss for silicon is plotted in figure 4.1.2 as function of the momentum p

Figure 4.2: Mean energy loss of electrons and positrons in silicon for from 50 keV to 10 GeV.

Additional to the ionization loss there are also bremsstrahlung effects, which can be described by equation 4.3 for relativistic particles ( $\beta^2 \approx 1$ ) [19]. The energy loss is proportional to the particle energy E and the material dependent radiation length  $X_0$ .

$$-\frac{dE}{dx} = -\frac{E}{X_0} \tag{4.3}$$

The radiation length is given by equation 4.4, which also takes into account coulomb screening effects of the core potential, with A the atomic mass number and Z the atomic charge number.

$$X_0 = \frac{716, 4 \ g/cm^2 \cdot A}{Z(Z+1) \cdot \log(287/\sqrt{Z})} \tag{4.4}$$

## 4.2 Multiple Coulomb Scattering

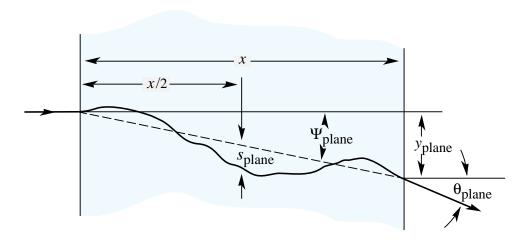

Any interaction will also cause a deflection of the penetrating particle arising from many small-angle scatters as sketched in figure 4.2. Most of those deflections are caused by coulomb scattering at the materials nuclei. For many applications it is sufficient to use a gaussian approximation which describes the rms for the central 98% of the angular distribution (Eq. 4.5) and ignores hard scatters and with this any tail contributions [17].

Figure 4.3: Illustration of multiple scattering in matter: many small scatters lead to one observable scattering angle [17].

$$\Theta_{rms} = \frac{13.6 MeV}{\beta cp} z \sqrt{\frac{x}{X_0}} \left[ 1 + 0.038 \log \left( \frac{x}{X_0} \right) \right]$$

$$(4.5)$$

The dependence on the particles properties charge z, velocity  $\beta c$  and momentum p shows already the problem for the Mu3e experiment. The multiple scattering is proportional to  $p^{-1}$ , it increases drastically for low momenta as the particles in the  $\mu \to eee$  decay. But the equations also shows the possibility to balance this effect via the reduction of the material thickness in units of the radiation length  $x/X_0$ .

#### 4.3 Particle Detectors

The above discussed effects are a potential measurement uncertainties, but the interaction of particles with matter is of course also essential for their detection.

Particle detectors allow for the measurement of particle properties e.g. the momentum, the velocity or the energy. Each of these measurements requires a different detector approach, but they can be grouped in two main detector ideas. Either the complete absorption of an incident particle with thick layers of high Z materials as for energy measurements in calorimetry or the minimal disturbance of the particle with a rather low effective thickness  $x/X_0$  as in tracking detectors.

For the Mu3e experiment we are interested in a very precise momentum measurement, which basically offers two detector solutions, either a particle tracker based on layers of solid state detectors, or the use of a Time Projection Chamber (TPC).

A TPC makes use of a large cylindrical gas volume along the beam axis with a high voltage applied between the two ends of the cylinder. Charged particles which cross the gas will ionize atoms and the ions and the electrons will drift to opposite ends of the cylinder which are instrumented for their detection. This allows for a full reconstruction of the track, as a charged particle will leave a trace of ionized gas along its path. The disadvantage of this technology is on one hand that the drift collection is quiet slow,

which limits the rate capability of such a system and causes space charge effects. On the other hand it is hard to handle the conditions of such a large volume of gas, as already minor contamination can destroy the detectors performance. However, this is technically solved, e.g. in the ALICE detector, but lifetime limitations due to aging prevail.

The main disadvantages of a solid state detector is in general its large material budget and the expensive production, but lately commercial available process are extensively used in industry and production cost are sinking. Also thinning processes for chips are routinely used, which allow to thin down the sensors and reduce the material budget immensely. A particle striding the chips semiconductor material will loose energy by creating electrons and holes, which can be detected with an electrode. A precise discussion will follow in section 5.4. In comparison to gaseous detectors they have the advantage of fast charge collection and signal handling, with almost no dead time.

# 5 Semiconductor Physics

The most common materials for the fabrication of semiconductor pixel detectors are silicon and germanium. The sensors for the Mu3e experiment will be made of silicon, their properties are discussed in the following.

#### 5.1 Silicon

Silicon atoms condense in a crystal with diamond like structure, with the four covalent electron bonds to the neighboring silicon atoms as shown in figure 5.2. The basic properties of silicon are summarized in in table 5.1.

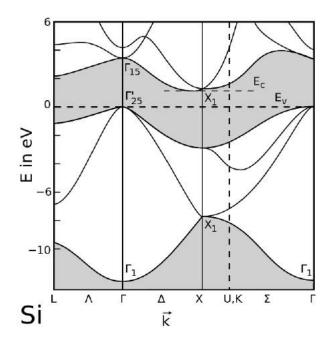

Semiconductor properties arise from the rather small energy difference between the electron states in the covalent bonds (valence band) and the free electron states not bond to an atom and moving through the crystal as free charge carriers (conduction band) as shown in the band structure diagram (fig. 5.1). At absolute zero temperature (0 K) all electrons are bond to atoms and so in the valence band. However, at room temperature (300K) some electrons can be thermally excited to the conduction band, leaving behind a "hole" in the covalent structure. This hole can be filled with an electron of an adjacent bond, creating a new hole. This gives the impression of a moving positive charge in the valence band which are referred to as holes. Excited electrons can be caught by a hole and fall down to the valence band again. This process is called recombination. Both processes excitation and recombination are governed by fermi statistics.

#### 5.2 Doping

At room temperature silicon has free charge carriers, but compared to metal this intrinsic given conductivity is very small as the number of charge carriers ( $ni = 1.5 \times 10^{10}/cm^3$ ) is negligible compared to the number of atoms ( $\sim 5 \times 10^{22}/cm^3$ ).

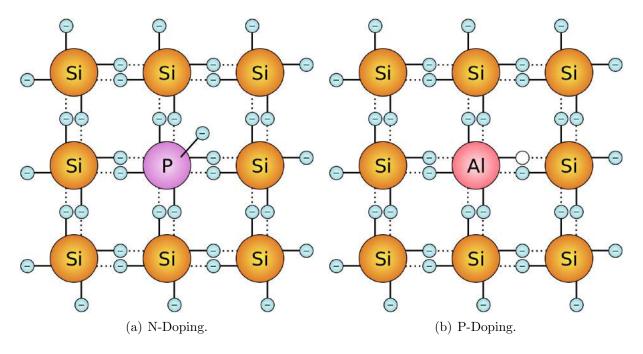

There is the possibility of artificially enhancing the conductivity by introducing impurities in the crystal, the so-called doping. By implanting atoms with five valence electrons, like arsenic or phosphorus, only four are involved in the covalent crystal structure while one is only weakly bound and located in a discrete energy level close to the conduction band (fig.5.2(a)). This allows a thermal excitation to the conduction band. These implants are called donators as they give additional electrons to the conduction band. But also the reverse process is possible as depicted in figure 5.2(b) by implanting atoms with 3 valence electrons like boron as a so-called acceptor. In this case one electron is missing to from the 4 covalent bonds. The missing bond can be filled by a thermally excited electron from the conduction band. Semiconductor material with donator implantations is referred to as n-doped as it creates additional negative charges, vice versa the implantation of acceptors is called p-doping.

| Property                  |                      | Value    | Unit          |

|---------------------------|----------------------|----------|---------------|

| Atomic number             | Z                    | 14       |               |

| Nucleon number            | 28.09                |          |               |

| Density                   | $\rho$               | 2.33     | $g/cm^3$      |

| Crystal structure         |                      | Diamond  |               |

| Atom density              |                      | 5.02     | $cm^{-3}$     |

| Intrinsic charge density  | $1.5 \times 10^{10}$ | $1/cm^3$ |               |

| Dielectric constant       | $\epsilon$           | 11.9     |               |

|                           | at $300K$            |          |               |

| Band gap                  | indirect band gap    | 1.12     | eV            |

|                           | direct band gap      | 3.4      | eV            |

| Average creation energy   | $\omega$             | 3.66     | $\mathrm{eV}$ |

| for an electron-hole pair | D                    | 0.115    |               |

| Fano Factor               | F                    | 0.115    | 0 /           |

| Mobility                  | $\mu_n$              | 1450     | $cm^2s/V$     |

|                           | $\mu_p$              | 500      | $cm^2s/V$     |

Table 5.1: Important silicon properties [20–25].

Figure 5.1: Band structure of silicon the indirect band gap of 1.12 eV is marked [26].

Figure 5.2: Crystal structure with dopand atoms. Image from [27][28]

The doping's magnitude is either described by the dopants-concentration  $N_{D/A}[1/cm^3]$  or by the resistivity  $\rho^1$

$$\rho = R \cdot \frac{A}{l} = \frac{1}{e(N_D \mu_n + N_A \mu_p)} \tag{5.1}$$

with R beeing the resistance, the length l, and cross section A of a material probe and the relation describing the resistivity for a solid state body with dopand-concentration N, the elementary charge e and the charge carrier mobility. As the mobility differs for electrons and holes they have to be distinguished, but in general the dopants concentration is dominating, which simplifies the description to  $\rho = (eN\mu)^{-1}$ .

# 5.3 PN-junction Diode

The boundary between a p-doped and n-doped volume is called pn-junction and can be used as a diode. It is the corner stone of all chip technology as it provides unique technical properties.

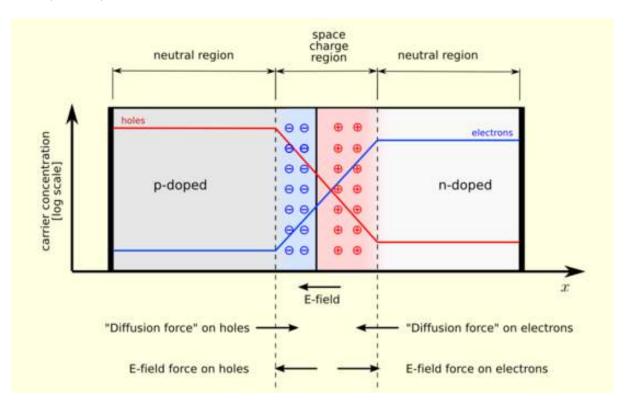

At the pn-contact there is a huge difference in the concentration of free charge carriers between both materials, which leads to diffusion of charge carriers into the bordering material, trying to balance this inequality. As electrons, diffusing into the p-doped material, are opposed to a majority of holes they will most likely recombine and vice versa. These recombining electrons and holes leave behind their corresponding acceptor and donator ions, giving rise to an electric field across the pn-junction. This field is opposing the diffusion movement and leads to an equilibrium of thermal diffusion and the drift movement

<sup>&</sup>lt;sup>1</sup>not to be mistaken for the charge density distribution

caused by the field. In this field region no mobile charge carriers are present as they are drawn away by the field created by the ions in the crystal lattice, it is called depletion zone (fig. 5.3).

Figure 5.3: PN-junction Equilibrium schematic. Image from [29]

With the assumption of diffusion and drift current in equilibrium an expression can be found for the so-called in-build potential or diffusion voltage:

$$U_D = U_T \cdot \log(\frac{N_A N_D}{n_i^2}) \tag{5.2}$$

With  $U_T$  the thermal voltage equivalent (25.9 mV at 300K),  $N_A$  and  $N_D$  the doping concentration and  $n_i$  the intrinsic charge carrier concentration [21].

The dynamic of this system is described by the Poisson equation (eq. 5.3) and allows the calculation of the potential U, the electric field  $E = \frac{dU}{dx}$  and the width w of the depletion zone from their charge density distribution  $\rho(x)$  given by the doping concentrations, the dielectric constant  $\epsilon_0$  and the relative permittivity  $\epsilon$ .

$$\frac{d^2U(x)}{dx^2} = -\frac{\rho(x)}{\epsilon_0 \epsilon} \tag{5.3}$$

The following calculations summon efforts [30], [31], based on [19] and [22], for the calculation of the depletion width w with a one dimensional model (x-direction perpendicular to pn-border). To carry out the integration of equation 5.3 several boundary conditions have to be defined. As spatial boundary we define  $x_p$  and  $x_n$  the extensions

of the depletion zone in the n- and p-doped area respectively. The pn-junction-interface is placed at x = 0 defining the depletion width as  $w = |x_p| + |x_n|$ . At the depletion zone boundaries the electric field E is assumed to be zero and the difference of the potentials on the boundaries should add up to the voltage applied between the two areas  $U_{Diode}$ .

Under these assumptions the Poisson equation can be interpreted as follows:

$$\rho(x) = \begin{cases} +eN_A & x < 0 \\ -eN_D & x >= 0 \end{cases}$$

$$(5.4)$$

describing a step-function-like doping profile.

A first integration with the predefined boundary conditions gives us the electric field E(x):

$$E(x) = \frac{dU}{dx} = \int_{x_p}^{x_n} \frac{d^2U}{dx^2} dx = \begin{cases} -\frac{eN_A}{\epsilon_0 \epsilon} (x - x_p) & x_p <= x < 0\\ +\frac{eN_D}{\epsilon_0 \epsilon} (x_n - x) & 0 <= x <= x_n \end{cases}$$

(5.5)

Further integration gives the potential U(x):

$$U(x) = \begin{cases} -\frac{eN_A}{\epsilon_0 \epsilon} (\frac{x^2}{2} - x_p x) + C_n & x_p <= x < 0\\ +\frac{eN_D}{\epsilon_0 \epsilon} (\frac{x^2}{2} - x_n x) + C_p & 0 <= x <= x_n \end{cases}$$

(5.6)

Under the logical continuity condition that the potential needs to be the same at x=0 coming from both both sides, its clear that  $C_n = C_p = C$ . With the above defined boundary conditions we set  $U(x_p) = U_0$  ( $U_0$  is negative) and  $U(x_n) = 0$  giving rise to equations 5.7 & 5.8

$$U(x_p) = U_0 = -\frac{eN_A}{2\epsilon_0 \epsilon} x_p^2 + C \tag{5.7}$$

$$U(x_n) = 0 = +\frac{eN_D}{2\epsilon_0 \epsilon} x_n^2 + C \tag{5.8}$$

The subtraction of  $U(x_p)$  and  $U(x_n)$  gives the applied voltage  $U_{Diode}$  and eliminates C:

$$U_{Diode} = U(x_p) - U(x_n) = U_0 = -\frac{e}{2\epsilon_0 \epsilon} (N_D x_n^2 + N_A x_p^2)$$

(5.9)

With the help of the additional condition of charge conservation formulated as equality of charges in the depleted areas  $N_A x_p = N_D x_n$  formulas for  $x_p$  and  $x_n$  can be deduced.

$$x_p = \sqrt{\frac{2\epsilon_0 \epsilon(-U_0)}{eN_A(1 + N_A/N_D)}}$$

(5.10)

$$x_n = \sqrt{\frac{2\epsilon_0 \epsilon(-U_0)}{eN_D(1 + N_D/N_A)}}$$

$$(5.11)$$

This gives the following expression for the depletion zone thickness/width w:

$$w = x_n + (-x_p) = \sqrt{\frac{2\epsilon_0 \epsilon U_0}{e} \frac{N_A + N_D}{N_A \cdot N_D}}$$

$$\tag{5.12}$$

The approximation with  $N_D \gg N_A$  gives  $w \propto \sqrt{U_{Diode}/N_A}$ , showing the depletion zones width dependence of the applied voltage and the lower dopant concentration.

A pn-junction also creates a dynamic capacity. In reverse biased mode it is referred to junction capacitance, created by the depletion zone which separates the mobile charge carriers like a plate capacitor. As known from electrostatics the capacitance of a plate capacitor is proportional to A/d, with A the plate area and d the plate distance. For the pn-junction the depletion zone width can be interpreted as plate distance equivalent, yielding  $C_{pn} \propto \sqrt{U}^{-1}$ .

# 5.4 Signal Generation & Charge Collection

As discussed in section 4 incident charged particles interact electromagnetically with the silicon causing ionization, which leads to the creation of electron-hole-pairs along the particles path. Soft X-ray photons will undergo photo effect in the material and produce a charge cloud. The mean creation energy for an electron-hole pair in silicon was measured in several experiments and is given in table 5.1.

The charge collection in a diode is driven by two processes: drift and diffusion, and therefore has two components. The fast component is the collection of the electron-hole pairs created within the depleted area, here they are collected rapidly by the electric field. Electron-hole pairs which have been created in the non-depleted region will diffuse undirected and most probably recombine. However, some will diffuse into the depletion zone and are collected via drift. This gives rise to a slow component, which is expected to be negligible for the MuPix sensors, as the signal will be dominated by charges collected from the depleted volume.

The collection time will depend on the average drift velocity of the electrons and holes in the electric field E. The velocity can be calculated from the mobility  $\mu$ .

$$v_{drift} = v_d = E \cdot \mu \tag{5.13}$$

. As listed in table 5.1 the mobility differs for electrons and holes. However, for the HV-MAPS sensors only the fast electron component is relevant for the signal generation and holes are not considered any further.

In silicon the electron mobility is constant up to field strengths of  $10^4 \ V/cm$ , for higher fields the electrons scattering with defects and the lattice causes a growing resistance, finally leading to a saturation drift velocity of  $\sim 3 \times 10^6 cm/s$  for fields higher than  $\approx 10^5 \ V/cm$  [22]. A further effect coming up in this field region is the production of secondary electrons, due to primary electrons which could gather enough energy between two scatters to create an electron-hole pair. This can cause an avalanche in the high field region, leading to a signal enhancement and for even higher fields the diodes breakdown, a huge reverse current, most likely thermally destroying the diode.

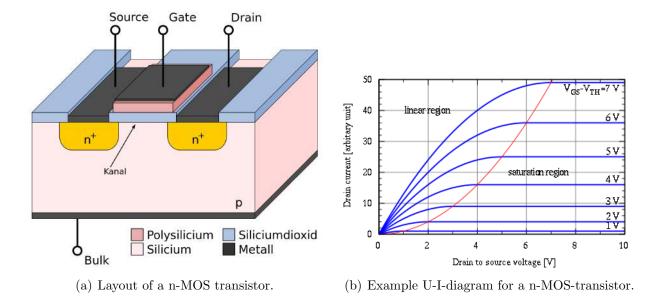

# 5.5 MOSFET Transistor

Metal-Oxide-Semiconductor Field Effect (MOSFET) transistors are the basic building blocks of all modern electronics. They can be implemented on semiconductor wafers by e.g. implanting two n-doped areas in a p-doped substrate (N-MOS) which are used as electrical contacts. On the surface between the two contacts a metal layer is placed, which is separated from the substrate through an oxide layer. This so-called gate is capacitively coupled to the substrate between the contacts, which allows a modulation of the charge carrier concentration below the gate, forming a conductive channel, allowing to steer the current flowing between the two contacts by changing the gate voltage.

The behavior of the transistor is not linear, the current flowing through the transistor depends on the gate voltage, as well as on the voltage between the two contacts (fig. 5.4(b)).

To understand the discussions in the following, two applications of transistors are important. In digital circuits the transistor can be used as a switch, with no current flowing for no gate voltage and a large current flowing for a high gate voltage. Further they can be used in analog circuits as adjustable resistors and currents sources, as the gate voltage allows to tune the current.

The inverse doping profile gives a p-MOS transistor. In general p- and n-MOS transistors are combined in circuits which is referred to as Complementary MOS (CMOS) technology.

Figure 5.4: CMOS transistors. Images from [32]&[33]

# 6 Pixeldetectors and the HV-MAPS technology

#### 6.1 Pixel detectors

Many present experiments, e.g. ATLAS, ALICE and CMS at LHC, make use semiconductor pixel detectors, as they can provide excellent 2D-spatial resolution. For semiconductor pixel sensors usually silicon or germanium wafers are used in a lithographic processes, which can introduce a pixelated doping structure on the wafer, e.g. simple detection diodes, which can be fully depleted. To readout these chips an additional readout chip is needed, which in general is bump bonded to the detection diodes, rendering these detectors a hybrid detector system. This introduces a lot of material causing multiple scattering and is therefore not compatible for the Mu3e experiment requirements.

This motivates the development of pixel detector chips with integrated readout electronics to reduce the material budget.

# 6.2 Monolithic active pixel sensors (MAPS)

A first step of this integration, made by the photo industry, was the development of Active Pixel Sensors (APS). Each pixel contains a detection sensitive area and digital part for the readout. Which renders the detection form factor rather small with only  $\sim 30\%$ . For particle detector how ever not only the semiconductor surface can be used for detection, but basically all wafer material below a pixel structure. This allows to build sensors using the full pixel size with electronics on the pixel surface and so  $\sim$ 100% fill factor. These sensor are the so-called Monolithic Active Pixel Sensors (MAPS). They are under way since the 90s and bring the benefit to be produced in commercially available Very Large Scale Integrated (VLSI) CMOS processes, which allows to make use of the industrial driven progress and keep the production cost low compared to specially developed fabrication procedures. Currently the first MAPS particle detectors have been installed in experiments, e.g. the MIMOSA chip [34] for the STAR vertex detector or for the EUDET beam telescopes [35]. The active detection volume for those sensors is the undepleted bulk material beneath the pixel electronics. A charge cloud of electrons and holes induced by a traversing charged particle will diffuse undirected in the semiconductor material and by chance meet the collection electrode. This shows a drawback of the MAPS technology compared to usage of depleted diodes as the diffusive Charge Collection (CC) is slow compared to drift collection in diodes.

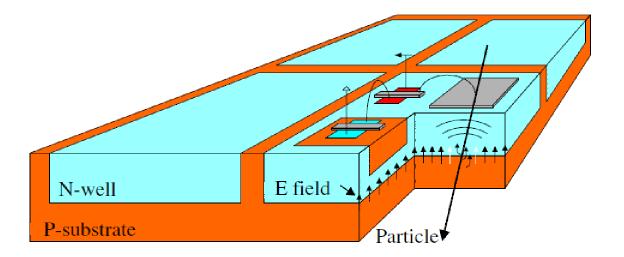

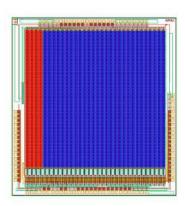

Figure 6.1: Sketch of HV-MAPS pixel diodes: p- and n-doped areas form a diode with an electric field, electrode and logic are implemented in the n-well [36].

# 6.3 High voltage monolithic active pixel sensors (HV-MAPS)

# 6.3.1 The Concept

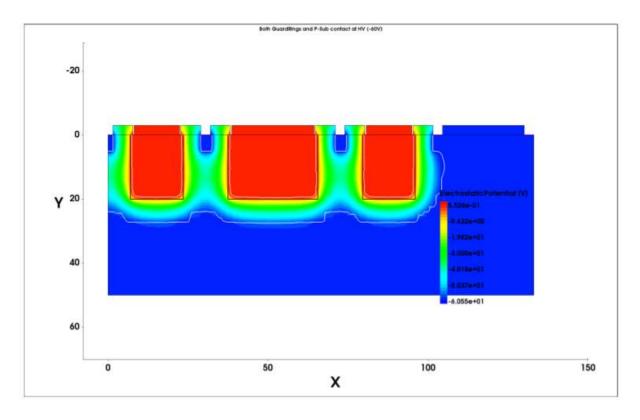

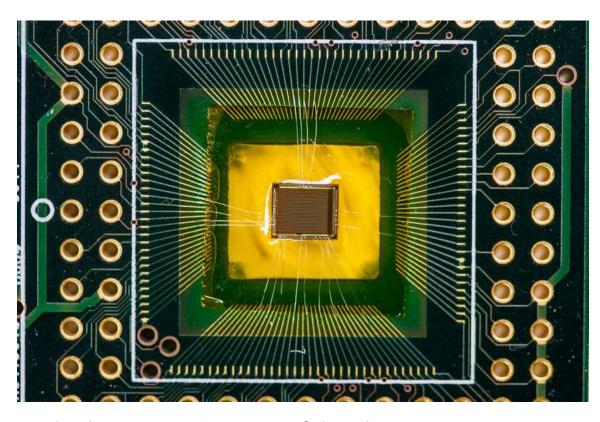

A combination of the MAPS principle with a diode as active detection element, the so-called High Voltage Monolithic Active Pixel Sensors (HV-MAPS), will merge the advantages of both technologies. Each pixel is consisting of a diode and pixel electronics. The diode is made up by the p-doped silicon substrate and a so-called deep n-well as shown in figure 6.1. This design allows to reversely bias the diode by applying a negative voltage  $\sim 60V$  at the substrate and create a depletion zone as detection volume with a very fast charge collection and at the same time implement analog and digital electronics using the deep n-well as substrate, this implementation is called floating logic. This new technology also maintains the advantage of commercially available high voltage CMOS processes used e.g. in the automotive or power industry which reduces the cost compared to customized production.

Further it will be possible to thin down the sensor to  $\sim 50 \mu m$  thickness with out cutting on his performance, as the depletion zone will only extend  $\sim 10 \mu m$  underneath the sensors surface, rendering the rest of the bulk material unused. This technology was first proposed by Ivan Perić in 2006 [36] and found to be a suitable candidate to fit the requirements for the tracker of the Mu3e experiment.

# 6.3.2 The MuPix Prototypes

To confirm the suitability of the HV-MAPS concept for the Mu3e experiment, it needs to be qualified and the performance has to characterized with the help of prototype sensors. These are produced in a High Voltage CMOS process in so-called Multi Project Wafer (MPW) runs, which allow a cost efficient prototyping of small Application Specified Inte-

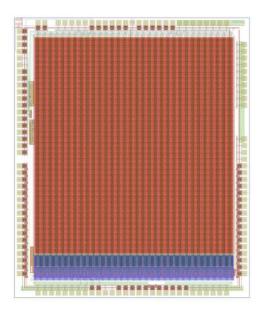

Figure 6.2: Layout of MuPix3: Red colored the pixel matrix, blue colored the peripheral digital part.

| Prototype          | Pixel Matrix                    | Pixel Pitch                                           | Novelty                               | Theses                   | Year              |

|--------------------|---------------------------------|-------------------------------------------------------|---------------------------------------|--------------------------|-------------------|

| MuPix1&2<br>MuPix3 | $42 \times 36$ $40 \times 32$   | $39 \times 30 \ \mu m^2$<br>$92 \times 80 \ \mu m^2$  | Proof-of-principle<br>digital readout | [30], [31]<br>[37], [38] | 2011,2012<br>2013 |

| MuPix4             | $40 \times 32$ $40 \times 32$   | $92 \times 80 \ \mu m$ $92 \times 80 \ \mu m^2$       | digital readout                       | [37], [38]               | 2013              |

| MuPix6<br>MuPix7   | $40 \times 32$ $(40 \times 32)$ | $102 \times 80 \ \mu m^2$ $(102 \times 80 \ \mu m^2)$ | additional amplifier full integration | this thesis              | $2014 \\ 2014$    |

Table 6.1: Overview over present and future MuPix prototypes.

grated Circuits (ASICs). All so far produced MuPix prototypes show a similar structure as they consist of a pixel matrix with an in-pixel pre-amplifier, and discrimination and digital signal handling in a peripheral strip. As shown in table 6.1 several prototypes have been characterized in multiple bachelor and master theses.

The MuPix1 and MuPix2 prototypes are the first HV-MAPS sensors ever produced and served as proof of principle test for the HV-MAPS concept with a charge sensitive amplifier implemented on the pixels diode and already showed a good eligibility for the experiment.

In the further iterations a more involved digital processing of the analog pixel signals and zero suppression mechanisms have been incorporated in the periphery.

In the MuPix6 design an additional amplification stage was added in the periphery.

The recently arrived MuPix7 prototype incorporates a readout state machine and timestamp generator in the periphery, so it will be independent of external readout signals. This means all wanted components of the final chip are already implemented on this prototype.

The characterization of the MuPix6 prototype is the topic of this thesis.

Part II

Setup

# 7 The Mupix

In the framework of this thesis two prototypes are investigated. One prototype is the MuPix4, which has already been studied extensively [37]. This prototype is now also available in an industrial thinned version, which is studied with respect to a performance impact in the lab and on a testbeam campaign. The second is the MuPix6 prototype whose characterization poses the main part of this thesis.

# **7.1** Mupix4

The MuPix4 prototype was already characterized in the previous thesis [37]. Therefore the prototypes structure is only discussed briefly, as in most parts its very parallel to the MuPix6 structure described in the following section 7.2.

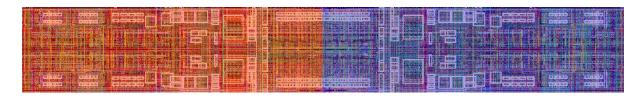

The MuPix4 consists of a  $32 \times 40$  pixel matrix with a pixel size of column-pitch= $92\mu m$  and row-pitch= $80\mu m$ , giving an active area of  $2.944 \times 3.2mm^2$ . The physical chip size covers an area of  $3.5 \times 4.16mm^2$ , giving a fill factor of 64.7% including pads. However, the important number is the ratio of digital part to active area, which is  $380\mu m/3200\mu m = 11.2\%$ . These numbers will improve further for a larger chip as the inactive area e.g. covered by pads or supply voltage lines will not scale with the chip size.

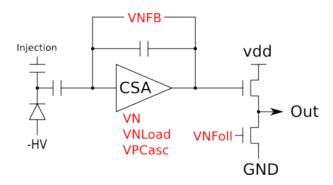

Each pixel is subdivided in a shorted  $3 \times 3$  diode structure (fig. 7.4) with the central diode's deep n-well housing a charge sensitive amplifier (CSA) and a source follower (SF) to drive the high capacity line to the periphery.

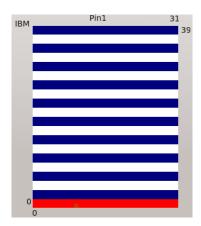

In the periphery this signal is discriminated and passed to the digital readout system. This part is not fully functional, as for half of the pixel rows the address is deleted before it could be readout. This problem caused a distinct pixel hit pattern, referred to as the "Strixel "-problem (figure 7.1).

Figure 7.1: The strixel pattern of the MuPix4 prototype observed with the online monitor of the graphical user interface.

# **7.2** Mupix6

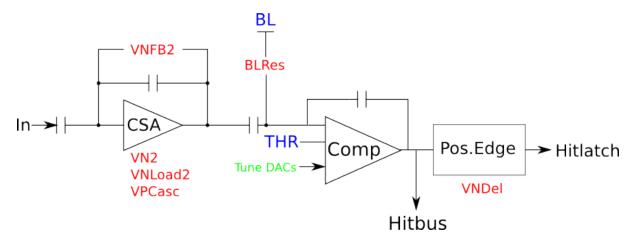

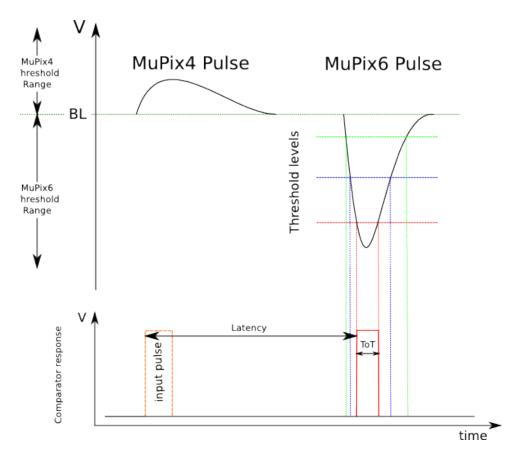

The MuPix6 (actually it is the fifth prototype) was submitted with a fix of the readout system which is supposed to solve the "Strixel"-problem. Further a new amplification scheme is tested by adding an additional amplification stage in the periphery before the discriminator with the intention of achieving a better Signal-to-Noise-Ratio (SNR). This guarantees a higher stability against possible digital cross talk caused by readout signals and timestamps. The intention is an additional amplification factor of three [39].

In the following the pixel and readout structure is discussed, from the initial diode signal to the readout data.

# **7.2.1 The Chip**

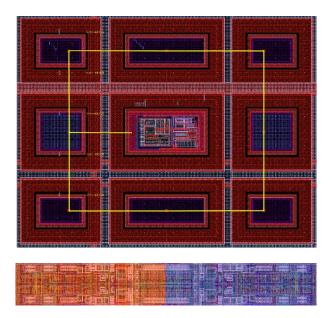

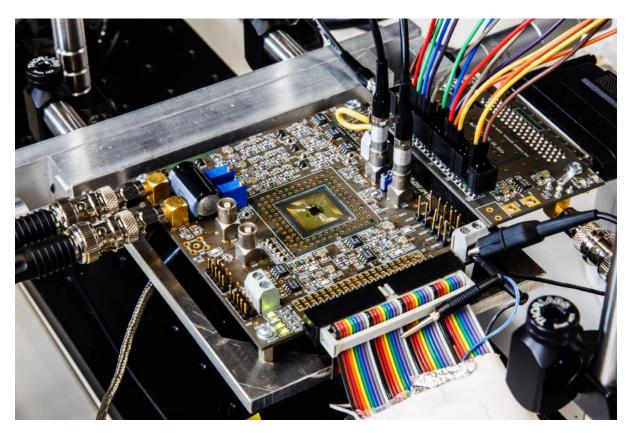

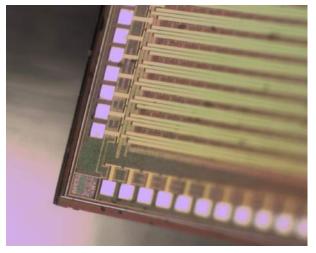

As the MuPix6 is the direct successor of the MuPix4 it inherits the general layout structure as depicted in figure 7.2, but with slightly different sizes. The change in size is caused by the additional amplification stage, due to the fact that the column-pitch of the pixel is matched to the digital part extensions. In the column-pitch of one pixel two pixel periphery units can be placed as shown in figure. 7.4. This gives a new pixel pitch of  $102 \times 80 \mu m$ , enlarging the detection area to  $3.296 \times 3.2 mm^2$ . However, due to the symmetric expansion of pixel and digital part the ratio of active and digital part is conserved. Each pixel consists of a CSA and SF in the pixel and a corresponding digital element in

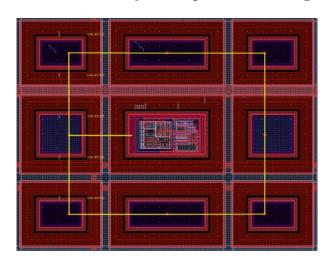

Figure 7.2: The MuPix6 Chip Layout exported from Cadence® Red: 1-staged pixel, blue: 2-staged pixel.

the periphery (fig.7.3). While the physical pixels are arranged in a  $32 \times 40$  matrix, the digital parts are organized in a  $64 \times 20$  matrix. The pixel addresses, readout in the end, are also generated in the digital part encoding the position in the digital part matrix, which makes a decoding to physical pixel addresses necessary. This mapping procedure was also described in [38] for MuPix4 and for MuPix6 in [40]. From this we can deduce a logical smallest unit cell shown in figure 7.3, which also enlightens the address scheme.

As shown in figure 7.2 in the MuPix6 prototype two types of pixels are implemented. 4 columns are manufactured in the "old "Mupix4 pixel design with only the CSA in the pixel, while the rest has an additional amplification stage in the periphery. This thesis focuses mainly on the 2-stage amplification pixels.

Figure 7.3: The MuPix6 Pixel Layout exported from Cadence®. Size matching of a pixel and 2 digital structures.

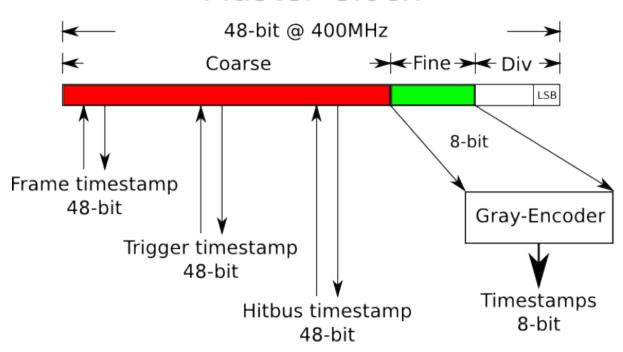

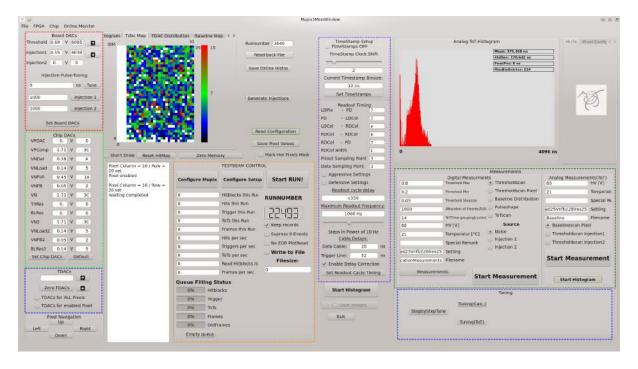

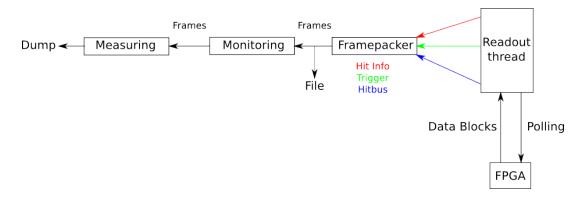

To steer the pixels performance two shift registers are placed on the chip whose values can be stored in RAM cells. One registers is controlling the so-called chip Digital-to-Analog Converters (chip DACs), which generate bias voltages for the pixels (6-bit), which will be discussed in the following. The other is used to set the so-called tune DACs and to select one pixel for a dedicated "hitbus" readout. The hitbus signal is the discriminator output of the selected pixel.

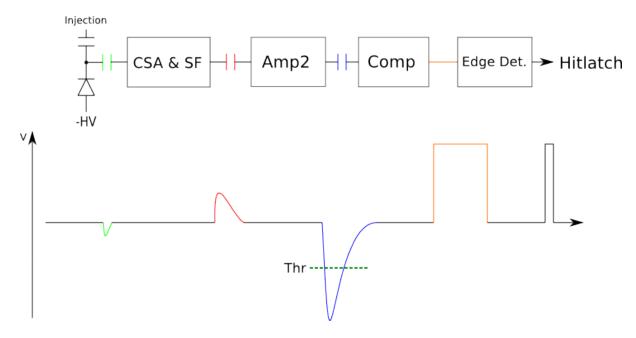

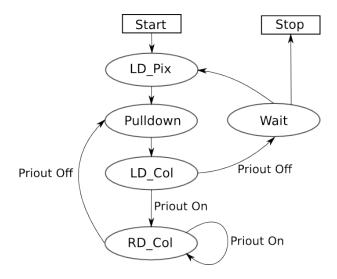

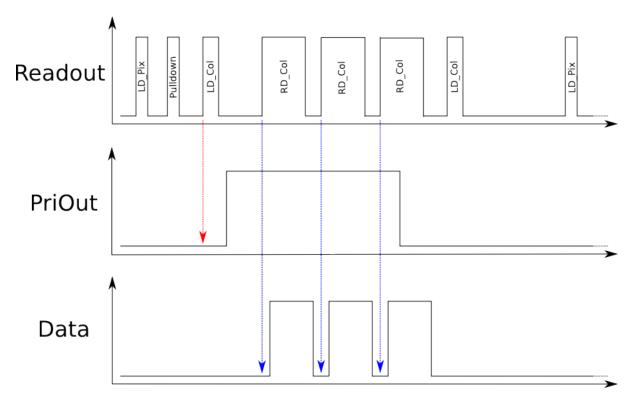

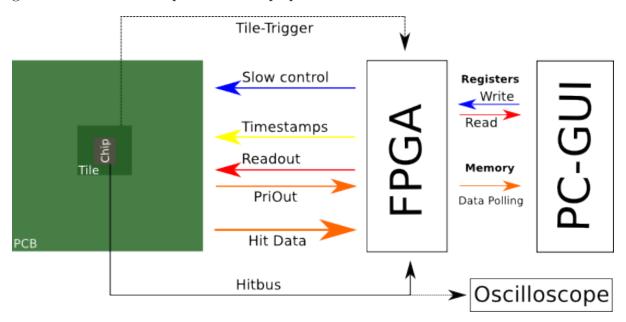

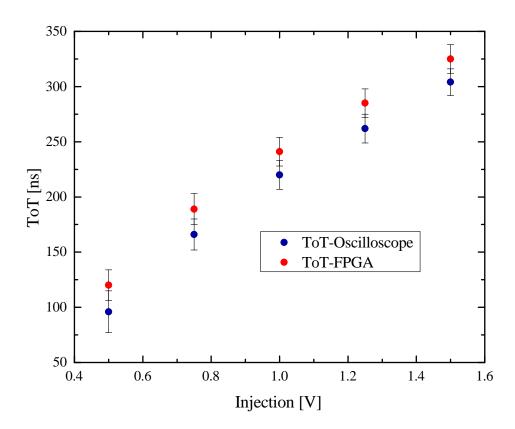

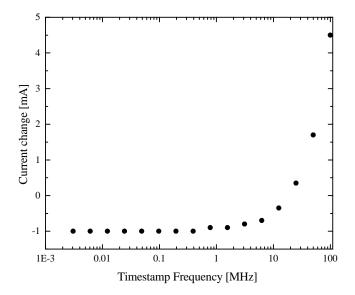

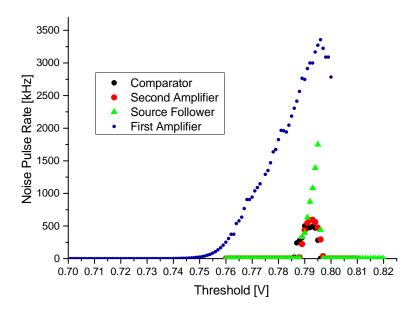

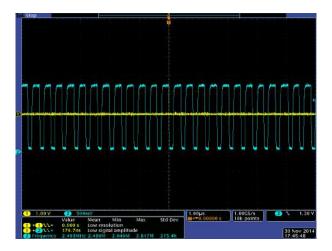

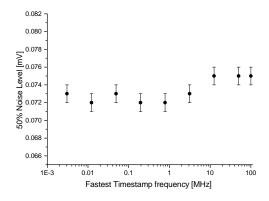

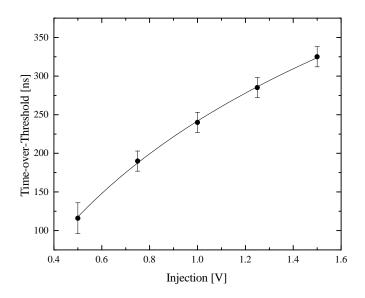

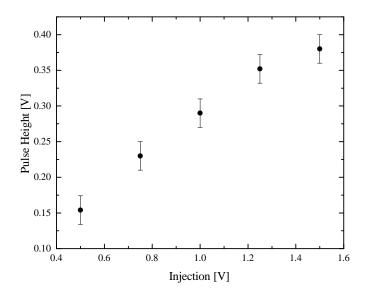

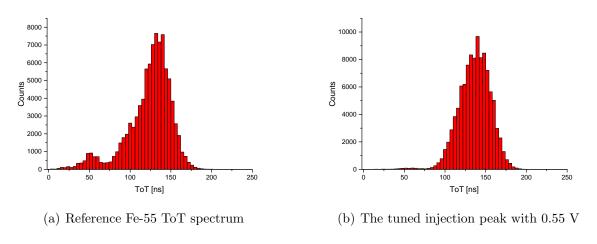

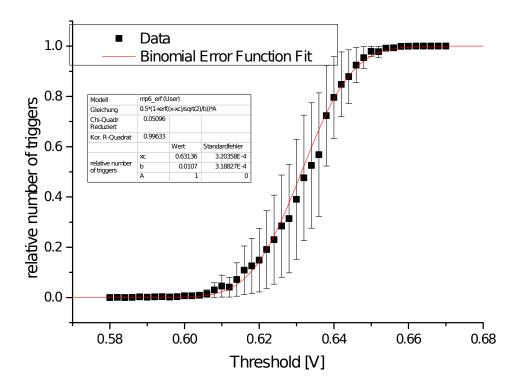

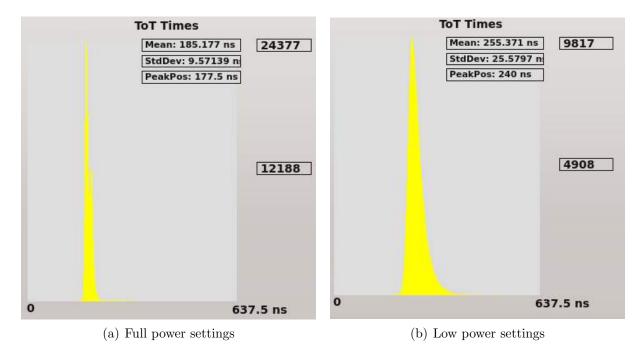

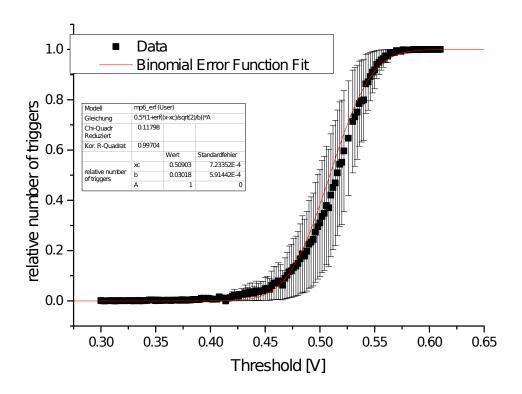

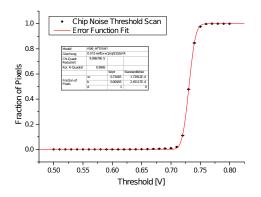

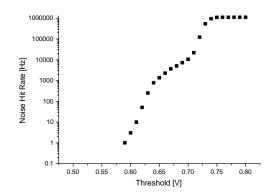

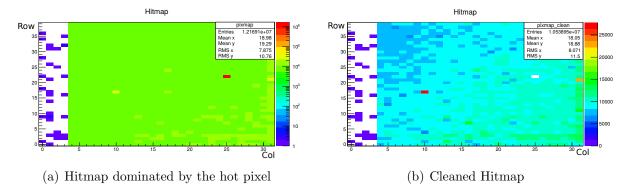

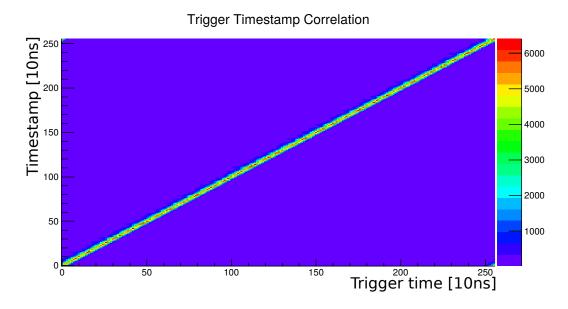

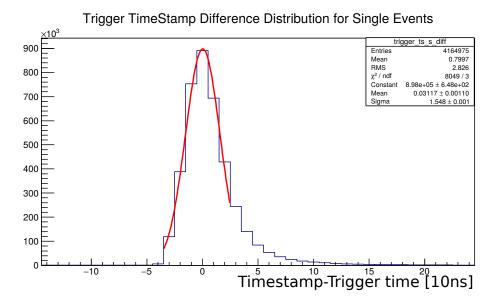

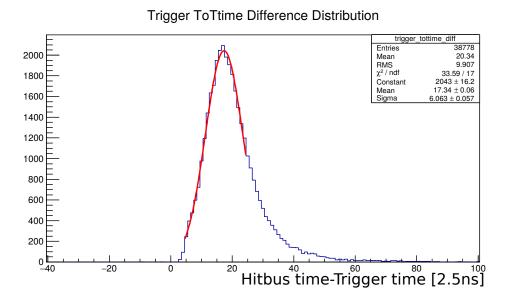

#### 7.2.2 The Pixel