## DISSERTATION

submitted to the Combined Faculties of the Natural Sciences and Mathematics

of the

Ruperto-Carola-University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

Put forward by

HEIKO AUGUSTIN born in Saarlouis Oral examination: 1<sup>st</sup> of December, 2021

# Development of a novel slow control interface and suppression of signal line crosstalk enabling HV-MAPS as sensor technology for Mu3e

Referees: Prof. Dr. André Schöning Prof. Dr. Peter Fischer

The Mu3e experiment searches for the charged lepton flavour violating decay  $\mu^+ \rightarrow e^+ e^- e^+$  with the goal to find or exclude the decay above a branching ratio of  $1 \times 10^{-16}$ . In a first phase of the experiment a reduced muon decay rate of  $1 \times 10^8$ Hz is used which allows to reach a single event sensitivity of  $2 \times 10^{-15}$ . With high particle rates and the low energy of the decay particles, the experiment imposes strong limitations on its material budget. For this reason the pixel tracker modules are designed with a thickness of 0.1% of a radiation length. The only pixel sensor technology which provides high rate capability, while allowing to thin the sensor down to 50 µm are high voltage monolithic active pixel sensors (HV-MAPS).

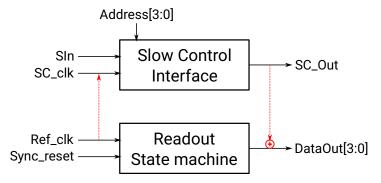

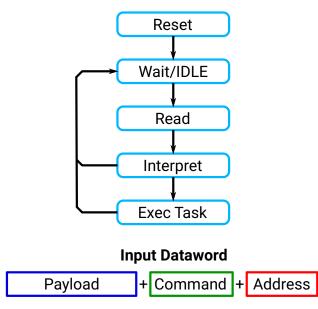

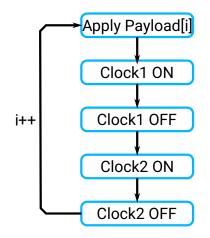

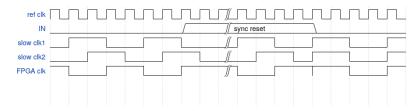

In this thesis the first full-scale pixel sensor for the Mu3e experiment, MuPix10, is described and first results from its characterisation are presented. The focus of this work is on two specific developments. The first one is a novel slow control interface is developed, tailored to the MuPix chip, with the goal of minimising the amount of required differential pairs used for the sensor configuration. The resulting interface requires no additional differential lines as it incorporates the syncronous reset signal and takes its place. The new interface allows to configure a 9-chip pixel tracker module with chip-individual configuration in less then 400 ms.

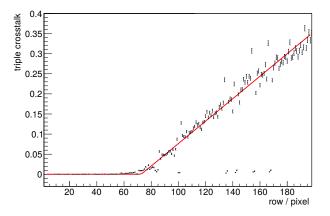

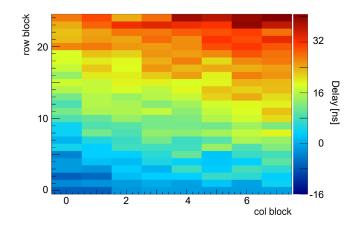

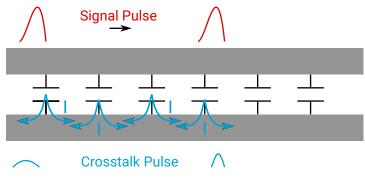

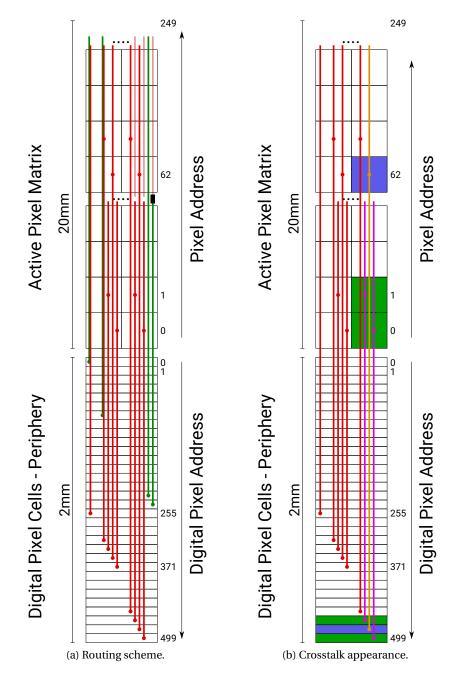

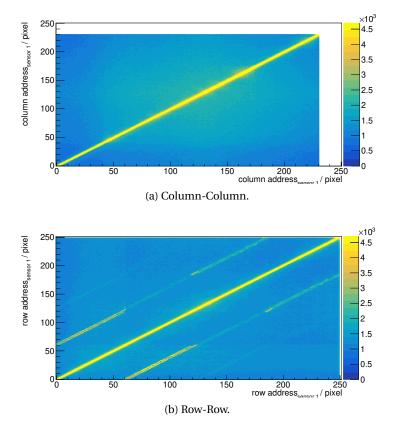

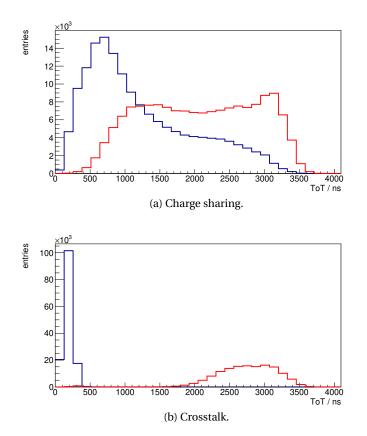

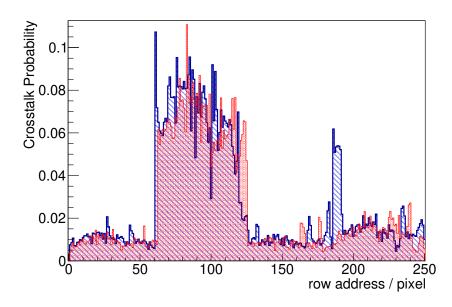

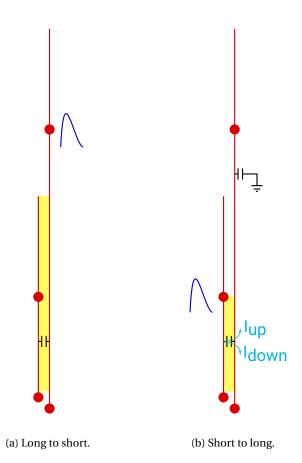

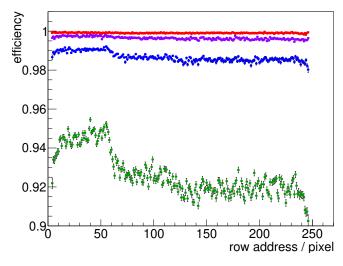

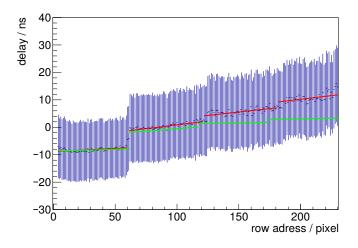

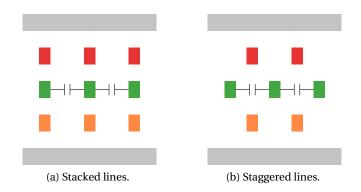

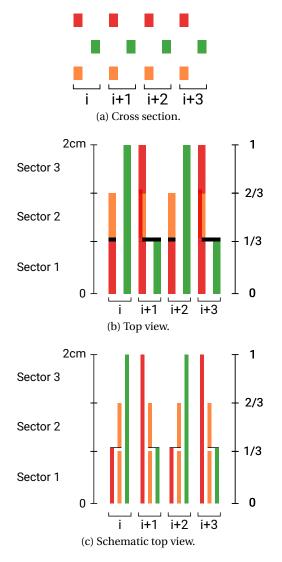

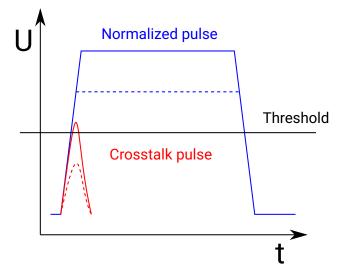

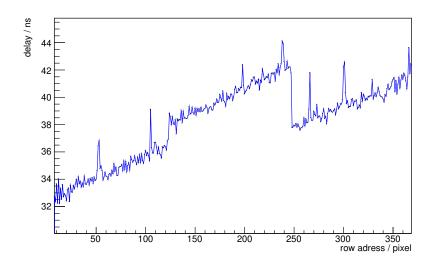

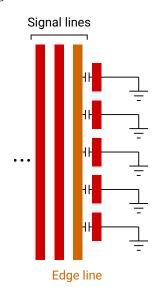

The second topic is the optimisation of the signal line routing scheme of the sensor with the goal to suppress crosstalk effects and reduce the row address dependent time delays, that have been observed in MuPix8. Subsequently, models are developed to gain a deeper understanding of the effects. The new routing scheme reduces the crosstalk probability from an expected average value of 18% to 2.5%. Furthermore, the time spread of the row dependent pixel delay is halved from 40 ns to 20 ns.

v

Das Mu3e Experiment sucht nach dem geladenen leptonfamilienzahlverletzenden Zerfall  $\mu^+ \rightarrow e^+e^-e^+$  mit dem Ziel den Zerfall nachzuweisen oder für Verzweigungsverhälnisse größer als  $1 \times 10^{-16}$  auszuschließen. In einer ersten Phase wird das Experiment mit einer reduzierten Muon-Zerfallsrate betrieben, wo durch die einzel-Ereignis Sensitivität auf  $2 \times 10^{-15}$  beschränkt ist. Auf Grund der hohe Teilchenraten und der geringen Energie der Zerfallsteilchen muss das Materialbudget des Detektors streng reduziert werden, mit dem Ziel Spurdetektorlagen mit einer Dicke von 0.1% einer Strahlungslänge bereitzustellen. Die einzige Pixelsensortechnology die Hochraten fähig ist wenn sie auf 50 µm gedünnt wurde, sind Hochspannungsgetriebene monolitisch aktive Pixelsensoren (HV-MAPS).

In dieser Arbeit wird MuPix10, der erste Pixelsensor mit der in der finalen Größe für das Mu3e experiment, vorgestellt und erste Ergebnisse werden präsentiert. Der Fokus dieser Arbeit liegt auf zwei spezifischen Entwicklungen. Ein Schwerpunkt ist die Entwicklung eine neuartige, maßgeschneiderten Konfigurationsschnittstelle für den MuPix-Sensor, mit dem Ziel die Menge der zur Konfiguration benötigten differentiellen Signalpaaren zu reduzieren. Die resultierende Schnittstelle benötig keine zusätzlichen differentiellen Paare, da das Signal für das synchrone Reset in die Schnittstelle integriert wird. Sie erlaubt die vollständige individuelle Konfiguration eines 9-Sensor Spurdetektormoduls in unter 400 ms. Das zweite Thema befasst sich mit der Optimierung der Führung der Pixelsignalleitungen mit dem Ziel Übersprechen und die Reihen-Addressen abhängige Latenz, die für den MuPix8 Sensor beobachtet wurden, zu reduzieren. Es wurde Modelle entwickelt, die ein tieferes Verständnis dieser Effekte ermöglichen. Mit Hilfe des neuen Schemas zur Führung der Pixelsignalleitungen, wurde die Übersprechwahrscheinlichkeit von erwarteten 18% auf 2.5% reduziert. Desweiteren wurde der Zeitunterschied der Pixellatenzen von 40 ns auf 20 ns halbiert.

| Ι   | INTRODUCTION 1                               |                                                         |    |  |  |  |

|-----|----------------------------------------------|---------------------------------------------------------|----|--|--|--|

| 1   | INTRODUCTION 3                               |                                                         |    |  |  |  |

| 2   | ТНЕ                                          | E MU3E EXPERIMENT 7                                     |    |  |  |  |

|     | 2.1                                          | The $\mu^+ \rightarrow e^+ e^- e^+$ signal decay        |    |  |  |  |

|     | 2.2                                          | Backgrounds                                             |    |  |  |  |

|     | 2.3                                          | The experimental concept                                |    |  |  |  |

|     | 2.4                                          | The Mu3e pixel tracker module                           | 11 |  |  |  |

| II  | ΗV                                           | 7-MAPS                                                  | 13 |  |  |  |

| 3   | AN I                                         | HV-MAPS FOR THE MU3E TRACKING DETECTOR 15               |    |  |  |  |

|     | 3.1                                          | Particle detection with silicon pixel sensors 1         |    |  |  |  |

|     |                                              | 3.1.1 Energy deposition                                 | 16 |  |  |  |

|     |                                              | 3.1.2 Charge collecting diode                           | 17 |  |  |  |

|     |                                              | 3.1.3 Charge sharing                                    | 20 |  |  |  |

|     |                                              | 3.1.4 Transistors                                       | 21 |  |  |  |

|     | 3.2                                          | Pixel sensor technologies                               | 22 |  |  |  |

|     |                                              | 3.2.1 Hybrid pixel detectors                            | 23 |  |  |  |

|     |                                              | 3.2.2 Monolithic active pixel sensors (MAPS)            | 23 |  |  |  |

|     |                                              | 3.2.3 High voltage monolithic active pixel sensors (HV- |    |  |  |  |

|     |                                              | MAPS)                                                   | 24 |  |  |  |

|     | 3.3                                          | MuPix10                                                 | 25 |  |  |  |

|     |                                              | 3.3.1 The HV-CMOS process                               | 25 |  |  |  |

|     |                                              | 3.3.2 Requirements                                      | 26 |  |  |  |

|     |                                              | 3.3.3 The MuPix10 chip                                  | 26 |  |  |  |

|     |                                              | 3.3.4 Towards MuPix11                                   | 41 |  |  |  |

|     | 3.4                                          | HV-MAPS beyond Mu3e                                     | 42 |  |  |  |

| III | III SLOW CONTROL & CROSSTALK OPTIMISATION 45 |                                                         |    |  |  |  |

| 4   | MUI                                          | PIX SLOW CONTROL                                        | 47 |  |  |  |

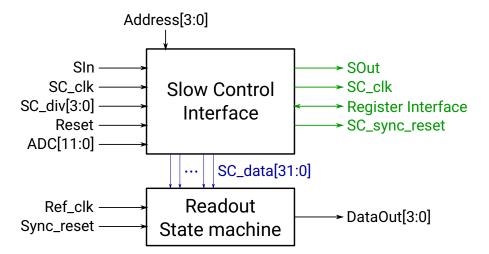

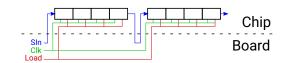

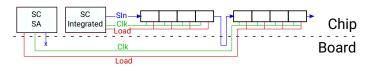

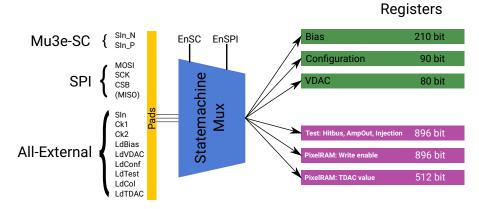

|     | 4.1                                          | The chip configuration infrastructure                   | 47 |  |  |  |

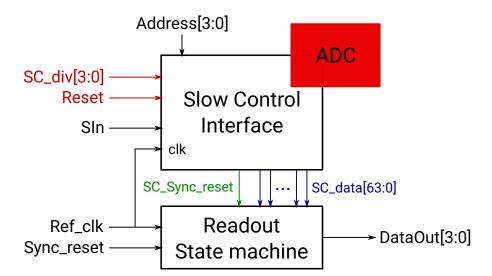

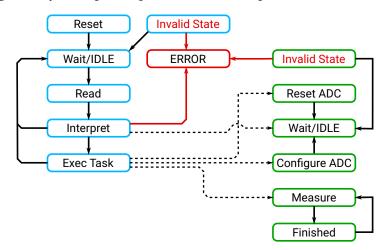

|     | 4.2                                          | Development of the Mu3e Protocol                        | 52 |  |  |  |

|     |                                              | 4.2.1 Logic implementation & Verification               | 56 |  |  |  |

|     | 4.3                                          | MuPix9                                                  | 57 |  |  |  |

|     |                                              | 4.3.1 Implementation                                    | 57 |  |  |  |

|     |                                              | 4.3.2 Commissioning                                     | 58 |  |  |  |

|     |                                              | 4.3.3 Conclusion                                        | 60 |  |  |  |

|     | 4.4                                          | MuPix10                                                 | 61 |  |  |  |

|     |                                              | 4.4.1 MuPix10 Configuration Infrastructure              | 61 |  |  |  |

|     |                                              | 4.4.2 Implementation                                    | 62 |  |  |  |

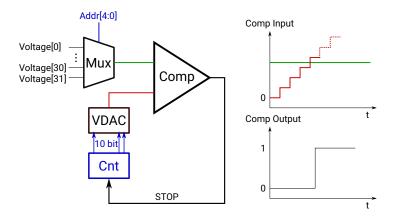

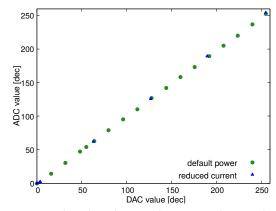

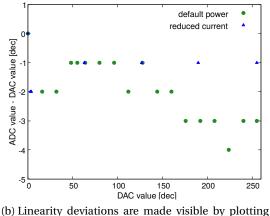

|     |                                              | 4.4.3 The ADC                                           | 64 |  |  |  |

|     |                                              | 4.4.4 First Commissioning                               | 65 |  |  |  |

|    |                                                                                                     | 4.4.5  | Module Configuration Strategies & Performance |            |  |  |

|----|-----------------------------------------------------------------------------------------------------|--------|-----------------------------------------------|------------|--|--|

|    |                                                                                                     |        | Projection                                    | 69         |  |  |

|    |                                                                                                     | 4.4.6  | Conclusion                                    | 73         |  |  |

| 5  | ANALOGUE SIGNAL TRANSMISSION IN LARGE SCALE MONO-                                                   |        |                                               |            |  |  |

|    | LITHIC CHIPS                                                                                        |        |                                               |            |  |  |

|    | <ul><li>5.1 Introduction</li></ul>                                                                  |        |                                               |            |  |  |

|    |                                                                                                     |        |                                               |            |  |  |

|    |                                                                                                     | 5.2.1  | Source Follower                               | 80         |  |  |

|    |                                                                                                     | 5.2.2  | RC-line                                       | 82         |  |  |

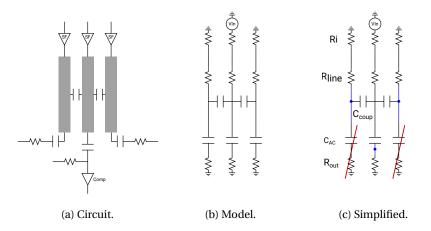

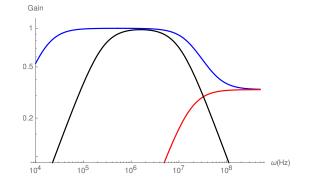

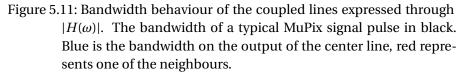

|    |                                                                                                     | 5.2.3  | Crosstalk                                     | 83         |  |  |

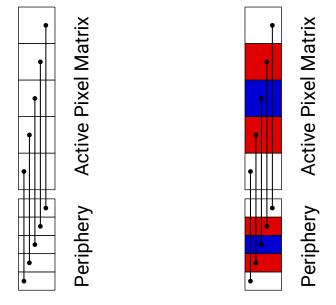

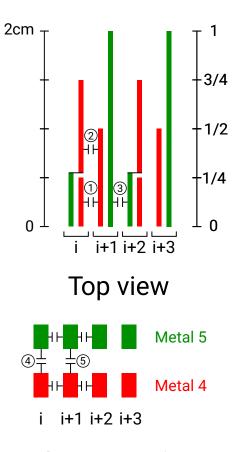

|    | 5.3 Routing optimisation for MuPix10                                                                |        |                                               |            |  |  |

|    | 5.4 MuPix10 results                                                                                 |        |                                               |            |  |  |

|    |                                                                                                     | 5.4.1  | Data & Analysis                               | 92         |  |  |

|    |                                                                                                     | 5.4.2  | Crosstalk                                     | 96         |  |  |

|    |                                                                                                     | 5.4.3  | Delay                                         | 109<br>111 |  |  |

|    | <ul><li>5.5 Optimisation considerations towards MuPix11</li><li>5.6 ATLASPix-like sensors</li></ul> |        |                                               |            |  |  |

|    |                                                                                                     |        |                                               |            |  |  |

|    | 5.7                                                                                                 | Conclu | sion                                          | 116        |  |  |

| IV | SIIN                                                                                                | AMARV  | AND OUTLOOK                                   | 119        |  |  |

| 6  | SUMMARY AND OUTLOOK<br>SUMMARY AND OUTLOOK                                                          |        |                                               |            |  |  |

| 0  | 3 U M                                                                                               | MANIA  | IND OUTLOOK                                   | 121        |  |  |

| V  | APP                                                                                                 | PENDIX |                                               | 125        |  |  |

| А  | PUBLICATIONS 12                                                                                     |        |                                               |            |  |  |

| В  | BIBLIOGRAPHY 13                                                                                     |        |                                               |            |  |  |

| С  | DANKSAGUNG 13                                                                                       |        |                                               |            |  |  |

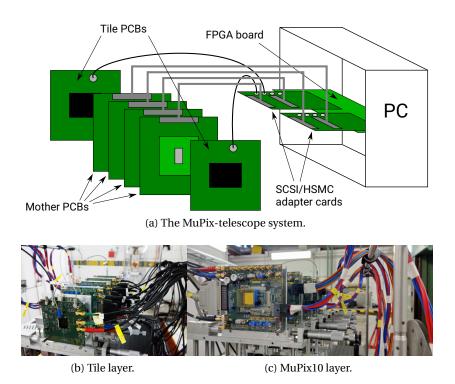

In this work the development of a high voltage monolithic active pixel sensor (HV-MAPS) for the use in the Mu3e pixel tracker is described with the focus on two specific developments. After an introduction of the Mu3e experiment and the explanation of its need for an ultra-thin and fast pixel tracker, an overview of silicon pixel detector basics and the available pixel detector types is given. Subsequently the MuPix10, the latest in a series of HV-MAPS prototypes for Mu3e, is introduced and first results are presented. In chapter 4 the development of a new configuration interface for MuPix chip discussed. In the last part of the thesis (chapter 5) the issue of signal line crosstalk and more general, the influence of the signal line on the sensor performance is discussed and the results for a novel routing scheme are presented and explained. Finally the work summarized and a conclusion for the Mu3e experiment and the future of the MuPix development is drawn. The complex data acquisition(DAQ) system was developed in collaboration with many colleagues. The author's focus and main solo-development was the chip configuration interface. The developed software allows for a fast implementation of any new arriving prototypes with a similar configuration architecture. Like this 16 different sensor prototypes have been implemented, typically reducing the commissioning time below one week. The DAQ is supporting single pixel investigations as well as the MuPix-Telescope.

An important application of the configuration is the tuning of the sensor. After the author initially implemented a fast tuning procedure which utilized FPGA functionality for MuPix8, which could not make use of it, the procedure was finally successful adapted by a student for the use with MuPix10.

Since MuPix7 the author got acquainted with the chip design side of sensor development with the goal to provide a fast feedback loop for the laboratory investigation of the devices and enabling a precise targeting of issues, as well as specification of problems and wishes with the designers. Since then the author has provided mayor input for all PCB designs which house a HV-MAPS pixel sensor in Heidelberg as well as all subsequent MuPix submissions.

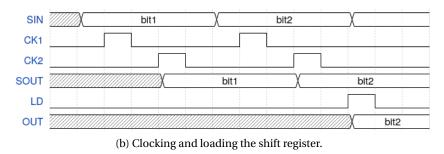

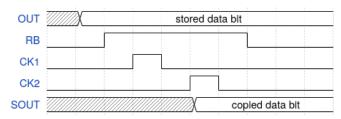

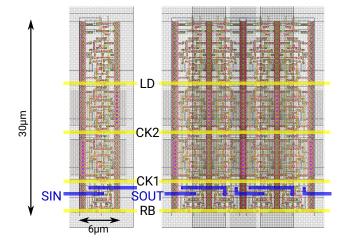

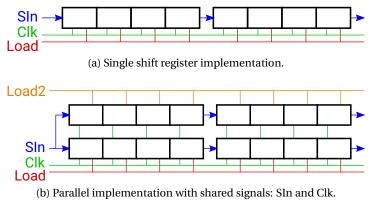

Starting with MuPix8, the author also performed design work with the colleagues at KIT. In MuPix8 he designed a new type of shift register which subsequently the baseline for all further HV-MAPS chips. Besides this a temperature stable current reference was ported from an other project.

In MuPix9 the first version of a new slow control concept for the Mu3e pixel sensors was implemented by the author. The project was finalised in MuPix10 and is presented in this thesis. Additionally MuPix10 features a novel routing scheme for pixel-to-pixel connections which is developed on the basis of experimental data with the goal to reduce the couplings in between these connection which lead to additional fake hits on the sensor. This development and its impact is also presented in the following, worked out by the author. The author makes use of the MuPix-Telescope and its analysis framework which was in large parts developed by a colleague, but the author is maintaining and debugging the frame work since the beginning as also a strong overlap with the DAQ for individual sensor investigation is present.

Beside these activities the author participated in or contributed to countless testbeam campaigns and guided decisively the laboratory efforts of the HV-MAPS characterisation in Heidelberg resulting in numerous Bachelor and Master theses ranging from basic studies of the analogue circuits to convoluted studies of sensor efficiency and time resolution at with testbeam data. Part I

### INTRODUCTION

With the discovery of the higgs particle at the large hadron collider (LHC) [1, 2], all particles that have been predicted by the Standard Model of particle physics (SM) have been found. The SM is describing the elementary particles and their interaction and it is performing splendidly, as so far all of the SM predictions of the particle interactions and their generation hold up.

However, it is the common understanding that the SM can not be entirely correct, as it fails to integrate gravity as an additional force into its frame work. Further the observation of the rotation and collisions of galaxies [3] and many more galactic structure formations can not be explained by the amount of matter that is visible, luminous, for us. The existence of a dark matter particle, which does not or only weakly interact with luminous matter, can explain all these observations. But the SM does not offer a particle which fits this description. Finally the SM also can not explain the large abundance of matter compared to anti-matter, the matter-antimatter asymmetry. The asymmetry present in the SM through CP-violation is not large enough, suggesting that the nature of particle physics is different in the hotter, early universe and allows for this large asymmetry.

Many beyond the SM theories naturally offer candidate particles and mechanisms to account for the effects mentioned above and always predict new particles at higher energy scales. This motivates the precision testing of SM predictions and the search for New Physics. Two different strategies are applied in these searches.

Either the search for new particles at high energies with increasing interaction rates with the High Luminosity upgrade of the LHC [4] or the contruction of an even more power full ring accelerator to access center of mass energies up to 100 TeV with the future circular collider (FCC) [5].

Or the precision investigation of SM parameters and rare processes which can be enhanced by these heavy particles e.g. entering on loop-level. An effect not predicted in the standard model is neutrino oscillation which is lepton flavour violating (LFV) and was confirmed in many different experiments by now [6–8]. The existence of neutrino oscillation proves that they are massive particles. These masses are added ad-hoc in the extended SM without providing a generation mechanism.

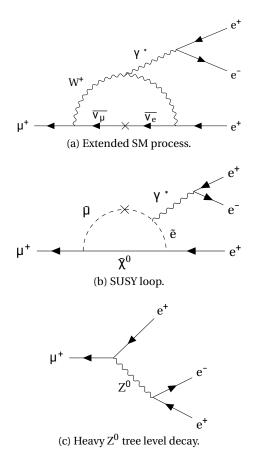

There is a large abundance of beyond the SM theories which predict LFV not only in the neutrino sector, but also for the charged leptons. E.g. super-symmetric models (SUSY) or models with new heavy gauge bosons [9]. In particular in the muon sector a large experimental effort is present, searching for charged lepton flavour violation (cLFV). The three investigated processes are  $\mu \rightarrow eee$ ,  $\mu \rightarrow e\gamma$  and  $\mu N \rightarrow eN$ , the latter describing the muon to electron conversion in the vicinity of a nucleus. Figure 1.1 shows possi-

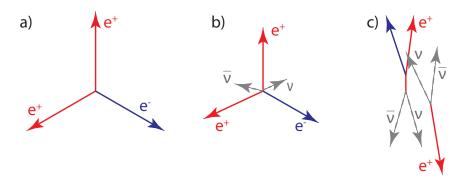

Figure 1.1: Charged lepton flavour violating  $\mu \rightarrow$  eee decays.

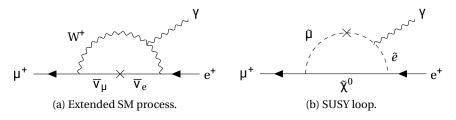

ble Feynman diagrams to generate the cLFV decay  $\mu \rightarrow eee$ . A comparison with the diagrams plotted in figure 1.2 shows that both the  $\mu \rightarrow eee$  as well as the  $\mu \rightarrow e\gamma$  process can be enhanced by the same loop contributions, which favours the  $\mu \rightarrow e\gamma$  channel for a search for cLFV as the branching ratio of the  $\mu \rightarrow eee$  decay will be suppressed by an additional factor  $\alpha$  due to the photo conversion process. However, the  $\mu \rightarrow eee$  channel gives an additional sensitivity to tree level processes as depicted in figure 1.1c which is not present in the  $\mu \rightarrow e\gamma$  channel.

Figure 1.2: Charged lepton flavour violating  $\mu \rightarrow e\gamma$  decays.

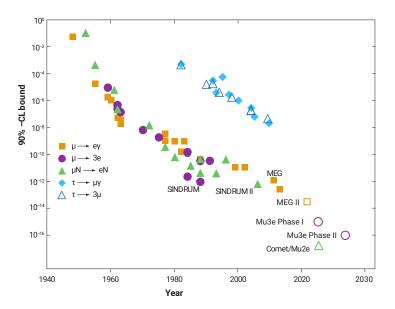

Table 1.1 shows the current experimental limits on the muon decay channels and figure 1.3 a time table of the investigation of the channels past, present and future.

| Channel                      | Experiment      | Branching ratio limit   |

|------------------------------|-----------------|-------------------------|

| $\mu^+ \to e^+ e^- e^+$      | SINDRUM [10]    | $< 1 \times 10^{-12}$   |

| $\mu^+ \to e^+ \gamma$       | MEG [11]        | $< 4.2 \times 10^{-13}$ |

| $\mu$ -Au $\rightarrow$ e-Au | SINDRUM II [12] | $< 7 \times 10^{-13}$   |

Table 1.1: Experimental limits for the three muon decay channels with 90% confidence level (CL). SINDRUM II used a gold target.

Figure 1.3: History of searches for lepton flavour violating decays. Taken from [13] and modified with [14].

The SINDRUM experiment performed the last measurement of the  $\mu \rightarrow$  eee channel in the 1980s. Thirty years later the Mu3e experiment is aiming to improve the current branching ratio limit ultimately by four orders of magnitude. This is achieved by using silicon instead of gaseous detectors which allows to access higher rates of muon decays. However, also in 2010 no pixel sensor technology was ready to use for the employment in a low-energy high rate experiment. This triggers the investigation of a new proposed technology which promises to fulfil all experimental requirements. In this thesis essential work is presented that is performed on the first full-scale prototype of the pixel sensor for the Mu3e experiment.

The Mu3e experiment [15–17] is searching for the charged lepton flavour violating decay  $\mu^+ \rightarrow e^+e^-e^+$  with the ultimate goal to either observe the decay or provide a new exclusion limit of a branching fraction > 10<sup>-16</sup> at 90% confidence level. To achieve this goal in reasonable amount of time (1 year measurement time), continuous muon stopping rates of  $2 \times 10^9$ Hz need to provided which currently no facility is capable to deliver. Therefore the experiment is conducted in a two phase approach. In Mu3e phase 1 the  $\pi E5$  beam line at the Paul Scherrer Institute (PSI) provides muon rates up to  $1 \times 10^8$ Hz which enables to achieve a single event sensitivity of  $2 \times 10^{-15}$  within a year of run time. The beam line that can provide the final rate required for Mu3e experiment (phase 2) is currently under development at PSI, the high intensity muon beam (HIMB) project [18].

2.1 The  $\mu^+ \rightarrow e^+ e^- e^+$  signal decay

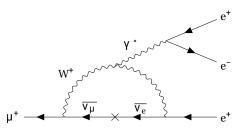

In the extended SM, with massive neutrinos, the decay  $\mu \rightarrow \text{eee}$  is possible via loop processes with a neutrino oscillation as depicted in figure 2.1. The branching ratio of this decay channel is however suppressed to levels  $< 10^{-54}$  [19, 20], which makes it practically unmeasurable and therefore leaves the channel with no irreducible physics background. Any detected  $\mu \rightarrow \text{eee}$  event is therefore a clear sign for cLFV and physics beyond the SM.

Figure 2.1: The SM  $\mu \rightarrow$  eee decay via a loop with neutrino oscillation.

The decay kinematics of this three body decay are used to identify  $\mu \rightarrow$  eee candidates and discriminate signal from background. The muons decay at rest and give the unique signature three charged particles, two positron and one electron, emerging from a common point, at the same time. The sum of the decay particles momenta  $\vec{p}_i$  should therefore vanish, while the invariant mass is equal to the muon mass.

$$\left|\vec{p}_{tot}\right| = \left|\sum \vec{p}_i\right| = 0 \tag{2.1}$$

Figure 2.2: Signal topologies for a) the  $\mu \rightarrow$  eee decay, b) the internal conversion decay and c) combinatorial background from two Michel decays with a Bhabha scattering event which generates the electron.

$$m_{inv} = \left|\sum p_i\right| = \sum E_i = m_\mu = 105.66 \,\mathrm{MeV}$$

(2.2)

The energy of the decay particles can maximally reach 53 MeV in a backto-back topology.

The mechanism which may create the lepton flavour violation is unknown, therefore the description through a generalised Lagrangian [21] is used which allows to study the influence of the interaction type on the decay kinematics.

#### 2.2 BACKGROUNDS

Although there is no irreducible physics background, two processes can generate fake signatures closely resembling the  $\mu \rightarrow$  eee kinematics. Figure 2.2 highlights the three different scenarios.

Combinatorial background is fuelled by high rates. The higher the rates, the more likely are accidental overlaps of different Michel-decays, pictured in figure 2.3a, with additional electrons from photon conversions or Bhabha scattering. To suppress this background an excellent vertex and time resolution is required, as the overlapping processes will not share a common vertex and decay time. For the phase 2 experiment a time resolution below 100 ps is required to disentangle the decay times of the individual decays.

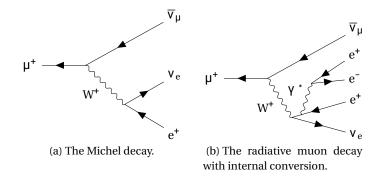

The internal conversion decay  $\mu^+ \rightarrow e^+ e^- e^+ vv$ , figure 2.3b gives the same signature of three charged particles with a common vertex, but an energy fraction is carried away by the undetected neutrinos. A measurement of the invariant mass of the decay particles will therefore result in a value smaller the muon mass.

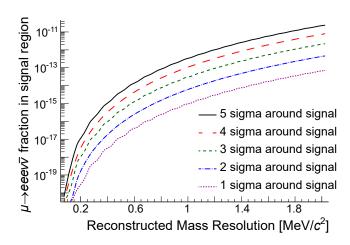

To achieve the goal of the  $2 \times 10^{-15}$  sensitivity with  $2\sigma$  cut on the signal region, a mass resolution better than 1 MeV is required as read of figure 2.4.

Figure 2.3: The SM muon decays relevant for the largest background contributions.

Figure 2.4: The reconstructed mass resolution which is required to suppress the amount of interconversion decays to certain fractions.

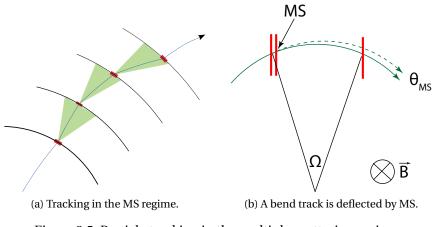

Both vertex and momentum resolution depend heavily on the material budget of the pixel tracker layers and in case of the vertex resolution also the stopping target. Due to the low momenta of the decay particles they are subject to strong multiple coulomb scattering (MS) effects as described by the Highland-formula [22] with p the particle momentum, x the material thickness and  $X_0$  the radiation length of the material.

$$\Theta_{rms} = \frac{13.6MeV}{\beta cp} z \sqrt{\frac{x}{X_0}} \left[ 1 + 0.038 \log\left(\frac{x}{X_0}\right) \right]$$

(2.3)

Figure 2.5 highlights the deflection of the trajectories of low energy particles, beeing the main uncertainty in their reconstruction. To reduce MS effects, only the minimisation of the material budget remains as an option to achieve the required background suppressions. The material budget goal is one permille of a radiation length.

Figure 2.5: Particle tracking in the multiple scattering regime.

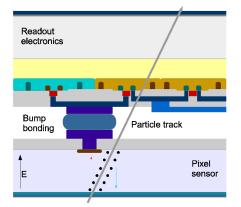

#### 2.3 THE EXPERIMENTAL CONCEPT

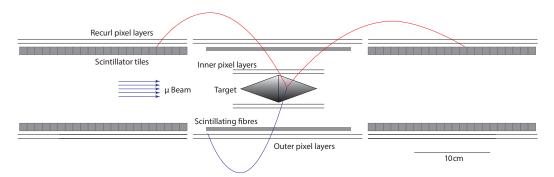

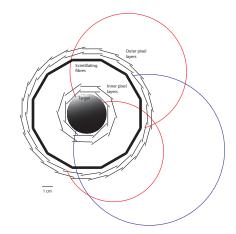

Figure 2.6 sketches the experimental concept of the Mu3e experiment [17]. A surface-muon beam strides a hollow, double cone target fabricated from Mylar, which stops the muons. The target is surrounded by four radial layers of HV-MAPS pixel sensors which form the pixel tracker, observing the muons decay at rest in a 1 T solenoidal field which is aligned along the beam axis. The two layers close to the target act as vertex detector, the outer layers enable the determination of the bending radius of charged decay particles and thereby their momentum. The momentum resolution improves for particles which "recurl" in the magnetic field and intersect again with the outer layers. To increase the number of the observed recurlers the pixel tracker layers are extended up- and down-stream. The pixel detector is cooled by flows of helium gas.

The Mu3e detector is complemented by two timing detector systems utilising scintillating fibres and scintillating tiles respectively, which provide an excellent time resolution to guarantee the suppression of combinatorial background and cope with the high particle rates.

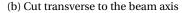

The data generated by the detectors is streamed out to their respective front-end boards where the data is time sorted and merged. In the next step the so-called switching boards distribute time slices of sorted data to a farm of graphics processing units(GPU) which subsequently run highly parallel tracking and triple vertex finding algorithms on the data. Only data that corresponds to a triple vertex originating from the target region will be keeped for further analysis [23]. The data flow is depicted in figure 2.7 from the detectors, producing approximately 100 Gbit/s, to the filter farm which reduces the data to (50-100) MB/s which is send to permanent storage. These estimates do not include any noise contributions, but represent the pure decay particle induced data in Mu3e phase I. The sensors closest to the target need to handle hit rates of 5 MHits/s.

(a) Cut along the beam axis.

Figure 2.6: Schematic view of the Mu3e detector concept.

#### 2.4 THE MU3E PIXEL TRACKER MODULE

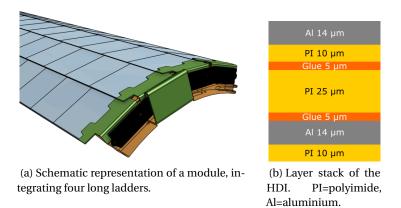

The most stringent requirement to the pixel tracker is the allowed material budget which directly limits the physics performance of the Mu3e experiment. A ladder consists of up to 18 sensors glued and bonded to a 2 layer aluminium high density interconnect (HDI), multiple ladders form a module as depicted in figure 2.8a. The HDIs cross section is sketched in figure 2.8b which account for a thickness of 0.05% radiation lengths. With the 50  $\mu$ m thick sensors glued to it the thickess increases to 0.115% of radiation length which suffices the Mu3e requirements.

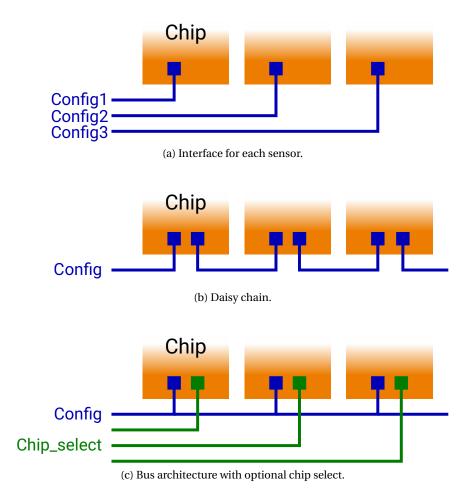

The HDI needs to provide power for up to 9 chips which in a worst case scenario amounts to 30 W of electrical power. More than 15 A which need to be distributed among the chips without large ohmic losses on the HDI itself. To guarantee a power routing design with minimal ohmic losses, the largest part of the aluminium routing space is needed for the power lines, requiring a rigorous reduction the remaining signal lines to the bare minimum. This comprises 9 differential data output lines and a two signal differential bus system for clocking and configuration. A configuration interface with a single differential input line is not a standard solution. It was

Figure 2.7: The MuPix readout system.

Figure 2.8: CAD drawing of an Mu3e tracker module and the material stack of the HDI.

specifically developed and tailored to the needs of the MuPix sensors and tracker modules. The development of this interface is described in chapter 4.

Part II

HV-MAPS

#### AN HV-MAPS FOR THE MU3E TRACKING DETECTOR

The requirements to vertex tracking detectors in particle physics are constantly increasing to higher vertex resolutions. but more importantly higher particle rates. In the 1980s this lead to emergence of the first silicon strip detector used for vertex detection [24], as commonly used gaseous detectors could no longer handle the particle rates. Since then silicon detectors form the heart piece of many high energy particle physics experiments, so also for the current experiments at the highest particle energies ATLAS and CMS [25, 26] and many more.

With the Mu3e experiment a new challenge arises for silicon tracking detectors. The detector system need to handle the high particle rates emitting from 10<sup>8</sup> muon decays per second, while maintaining an ultra low material budget to minimize tracking degradations through multiple-coulombscattering. At the time of the proposal [15] no common silicon pixel detector technology can suffice the experimental requirements and leads to the pursue and advance of a new proposed pixel detector concept, the high voltage monolithic active pixel sensors (HV-MAPS) [27].

In a series of pixel sensor prototypes [28–32] the technology was investigated and developed, culminating in the first large scale sensor design. Starting from this the goal is to mould a full scale pixel sensor which fulfils all experimental requirements concerning operation, performance and form factor to build the Mu3e tracking detector.

The objective of this thesis is to create a pixel sensor that eases the achievement of the material budget requirement for the pixel modules (section 4) by optimizing its configuration interface and to optimize the chip internal routing of the individual pixels to combat the "signal line crosstalk" which was observed for the predecessor MuPix8 (section 5).

#### 3.1 PARTICLE DETECTION WITH SILICON PIXEL SENSORS

A charged particle which traverses a larger volume of matter will inevitably interact with the electrons and nuclei. On one hand this leads to a deflection of the particle from its original path through multiple-coulomb scattering, on the other hand the interactions will deposit energy in the material. In silicon this deposited energy is creating electron-hole pairs which can be collected and measured, e.g. to pinpoint the particles crossing location. In the following only the interaction of electron and positrons with are discussed in detail. A comprehensive summary of all interaction types can be found in [22]

#### 3.1.1 Energy deposition

The interaction of a charged particle with matter is a stochastic process. The number as well as the strength of the interactions can vary widely, but the evolution of the mean energy loss of the particle is well understood and described by the "Bethe formula" [33]. For the use case of electrons and positrons, this formula has to be further modified to account for the small mass of the traversing particle as well as the indistinguishability of incident and scattering electrons in contrast to the positron which leads to different energy losses for the two species, the Berger-Seltzer formula [34].

$$-\left\langle \frac{dE}{dx}\right\rangle = \rho \frac{0.153536}{\beta^2} \frac{Z}{A} \cdot \left(B_0(T) - 2\log(\frac{I}{m_e c^2}) - \delta\right)$$

(3.1)

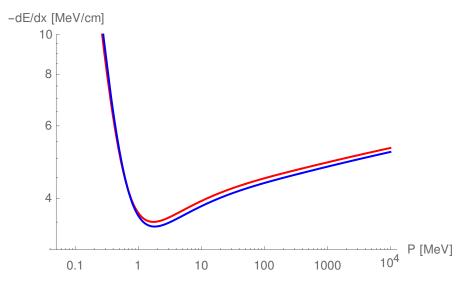

The energy loss depends on the material and momentum dependent stopping power  $B_0(T)$ , the material dependent mean excitation energy *I*, density correction  $\delta$ , atomic number *Z*, mass number A and material density  $\rho$ . The energy loss for silicon is plotted in Fig.3.1 as function of the momentum p. In the case of thin detector layers this formula is overestimating the

Figure 3.1: Mean energy loss of electrons and positrons in silicon for from 50 keV to 10 GeV with values from [34]. Electrons in red, positrons in blue.

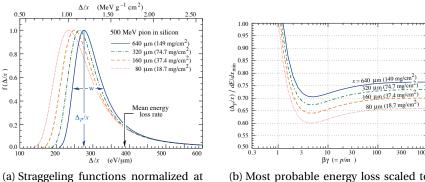

amount of deposited charge, as especially single interactions with a large energy transfer are possibly not contained in the small detector volume. It describes the mean energy loss of the particle, but not the amount of deposited energy inside the detector volume. This is discussed in [22] advocating the most probable values as better suited parameter as depicted in figure 3.2.

Additional to the ionization loss there are also bremsstrahlung effects, which can be described by equation 3.2 for relativistic particles ( $\beta^2 \approx 1$ ) ([35]). The energy loss is proportional to the particle energy *E* and the ma-

(a) Straggeling functions normalized at the most probable value.

(b) Most probable energy loss scaled to the mean energy loss.

Figure 3.2: Energy loss of a 500 MeV pion on thin silicon layers.

terial dependent radiation length  $X_0$ . As in this work deliberately only very thin material layers are used, bremsstrahlung is not a relevant effect.

$$-\frac{dE}{dx} = -\frac{E}{X_0} \tag{3.2}$$

The radiation length is given by the approximation in equation 3.3, which also takes into account coulomb screening effects of the core potential, with A the atomic mass number and Z the atomic charge number.

$$X_0 = \frac{716.4 \text{ g/} \text{cm}^2 \cdot A}{Z(Z+1) \cdot \log(287/\sqrt{Z})}$$

(3.3)

#### 3.1.2 Charge collecting diode

Silicon(Si) is a semiconductor if diamond like crystal structure each Siatom (4 valence electrons) forming 4 covalent bonds with 4 neighbouring atoms. At a temperature of 300 K 10<sup>10</sup>/cm<sup>3</sup> these bonds are broken due to thermal excitation, which releases the electrons into the crystal lattice and leaves a "hole" in the covalent bond structure. Both the electron and hole can move freely, however, with different mobility values  $\mu_e = 1400 \text{ cm}^2/(\text{Vs})$ and  $\mu_h = 450 \text{ cm}^2/(\text{Vs})$  which leads to different drift velocities in an electric field  $v = E * \mu$ . If a free electron encounters a hole in the lattice they can combine to reinstitute the covalent bond, the so-called recombination.

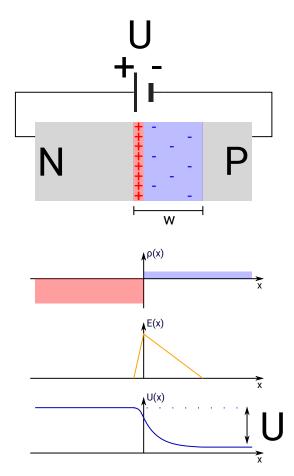

With  $10^{10}$ /cm<sup>3</sup> free electrons available as charge carriers, silicon is not a good conductor. To enhance its conduction capability, atoms with a different number of valence electrons can be added into the lattice structure (doping). By adding Boron, 3 valence electrons, the existence of a missing covalent is forced (p-doping). An additional hole is created. With the help of phosphorus, 5 valence electrons, the additional electron will not be bound in the crystal bond structure and is thermally exited into the crystal lattice, adding an free electron (n-doping). With typical doping concentrations add  $10^{15}$ /cm<sup>3</sup> "impurities" to the lattice and thereby the same amount of free charge carriers. The doped silicon is a better conductor but the prominent usage of this is the combination of P- and N-doped silicon, forming a PN-junction also called diode. Brought into contact electrons from the N-doped silicon will diffuse into the P-doped material, leaving behind a positively charged impurity in the lattice. Vice versa the holes leaving a negative charge. Due to this charge-up an electric field will develop at the junction between the materials which opposes the diffusion movement of the free charges. Charges caught in the electric field region are drifting in direction of the field, effectively keeping the region clear of free charge carriers. The region is therefore referred to as depletion region. The potential which is created by the electric field is called in-build potential.

If an external voltage, potential, is applied to the diode which opposes the build-in potential (forward-bias), a notable current will start to flow once the potential is surpassing the value of the in-build potential which is 0.7 V for silicon. An external potential which aligns with the in-build potential will lead to an increased depletion zone and a stronger electric field. Only a small current is flowing, generated from stochastically created electron-hole (e-h) pairs from thermal excitation. The charges will be separated by the field. Electrons drift to the N-doped area and positrons vice versa. The current-voltage behaviour of the diode is described by the Shockley-diode equation [36]. For large electric field strengths of ( $\approx 3 \times 10^5$ V/cm) the drifting charge carriers can generate new e-h pairs in collision with the lattice. A self-sustained avalanche of charge carriers will be generated causing a large current. The externally applied voltage level is referred to as breakdown voltage.

The depletion zone of a reverse-biased diode can be used for particle detection. A particle which passes through the depletion zone will deposit energy along its path as described before. The deposited energy is transformed into e-h pairs with an average generation energy of 3.6 eV per pair. These pairs are separated by the electric field which causes a current flow which is measured. The wider the depletion zone, the larger the amount of generated electron hole pairs.

Figure 3.3 shows a typical scenario for the use of a diode a particle physics detector. The diode is created by a strongly doped implant inside the weakly doped bulk material which results in an asymmetric formation of the depletion zone. The development of the potential and electric field based on the doping concentration and external potential is described by the Poisson-equation.

$$\frac{d^2 U(x)}{dx^2} = -\frac{\rho(x)}{\epsilon_0 \epsilon}$$

(3.4)

In the case of an strongly asymmetric doping strength the width of the depletion zone *w* is approximated by

$$w = \sqrt{\frac{2\epsilon_0\epsilon_r}{e} * \frac{1}{N_A} * U}$$

(3.5)

Figure 3.3: A reverse biased diode. The depletion zone width scales with the applied voltage.

and the maximum field strength is

$$E_{max} = \sqrt{\frac{2eN_A}{\epsilon_0\epsilon_r} * U}$$

(3.6)

with  $\epsilon_r$  the relative permittivity of silicon, *e* the electric charge,  $N_A$  the donator (p-)doping concentration and *U* the applied reverse bias voltage. The doping of silicon wafers is typically given in form of the resistivity value  $\rho[\Omega \text{ cm}]$ , which is connected to the doping concentration via the mobility  $\mu$ ,

$$\rho = \frac{1}{eN\mu} \tag{3.7}$$

which allows to reformulate w.

$$w = \sqrt{2\epsilon_0 \epsilon_r \mu_p U} \tag{3.8}$$

The diode forms a capacitance with the depletion zone as dielectric which represents the detector capacitance  $C_d$  for simple case shown above it can be calculated as

$$C_d = \epsilon_0 \epsilon_r \frac{A}{w} \tag{3.9}$$

with a the surface of the junction.

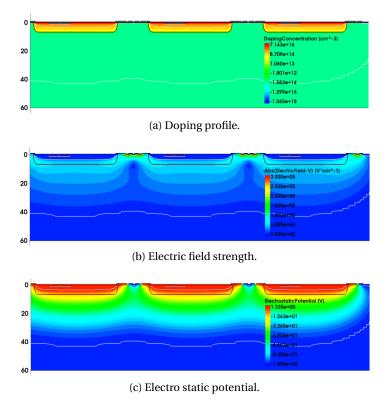

These are good approximations for many simple considerations, however, in reality the structures are much more complex and need a computer aided approach to get the full picture as shown in figure 3.4 to e.g. investigate the exact depletion behaviour, determine the expected breakdown voltage or simulate the passing of a charged particle. The charge collection is described by the Shockley-Ramo theorem, describing the induction of a current on the electrode as soon as the e-h pairs are starting to separate due to the electric field. The charges generated in the depletion zone of a MuPix chip  $w \approx 30 \mu$ m are typically collecting within 500 ps.

Figure 3.4: The simulation of three pixel diodes (MuPix10) with a substrate resistivity of  $200 \Omega$  cm at a reverse bias of 100 V [37].

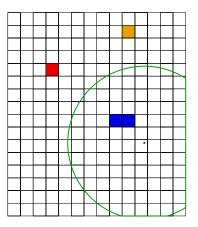

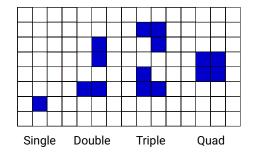

#### 3.1.3 Charge sharing

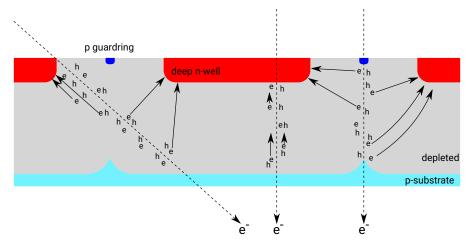

The surface of silicon wafer can be pixelated by creating a grid of shallow, strongly doped implants. Each of them forming a diode with the substrate. In figure 3.5 a cross section of three neighbouring diode is shown, with three cases of particles crossing the depletion zone which is the active detector volume. Each particle creates e-h pairs along its path. If it crosses perpendicular and central inside the pixel the charges will be collected by a single diode. In case it traverses at the border of two pixel, charges can be created in both. The generated charges will be transported by the electric field of diode in which they are generated. A the charge is split between multiple pixels this is referred to as charge sharing. In case of an inclined particle trajectory it can penetrate multiple pixels and created e-h pairs in all of them.

Figure 3.5: A typical case of a diode structure of HV-MAPS with the corresponding depletion zone. From left to right particles cross the detector volume inclined, centered and at the border between two pixel. For some electron the drift path is approximated for their way to the n-implant.

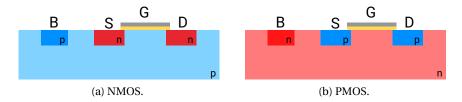

#### 3.1.4 Transistors

To make use of the signal that is generated by the charge collection of the diode, it needs to be further processed. For this purpose circuitry needs to be provided that amplifies, digitizes and reads out the signal, typical frontend electronics. They are implemented as integrated circuits utilizing the same micro processing technologies as the diode itself. The transistor technology used in this work is metal-oxide-semiconductor field-effect transistors (MOSFET), which are available in two flavours, NMOS and PMOS transistors. Figure 3.6 sketches the two types. Each transistor has four terminal: Source(S), Gate(G), Drain(D) and Bulk(B). The NMOS transistor is comprised of n-doped implants on a p-substrate and PMOS vice versa. The current that is flowing between source and drain contact is steered via the gate-source voltage difference ( $U_{GS}$ ) and the drain-source voltage difference  $(U_{DS})$ . A MOS transistor is characterised by its characteristic threshold voltage  $U_{th}$ , which enables a current flow between source and drain. Besides that the form factor of transistor characterised by its gate length L, the distance between gate and source, and the gate width which impact its performance. The current that is flowing through the transistor is proportional to  $\frac{W}{T}$ . Typical design choices are long transistors used current sources, wide transistors as input transistors and cascodes.

Depending on the applied voltages, the transistor can be operated in different states:

Figure 3.6: MOSFET transistors.

CUT-OFF/WEAK INVERSION In the case  $U_{GS} < U_{th}$  the transistor can be considered as "switched-off", only a very small current can flow, often perceived as leakage current.

LINEAR REGION  $U_{GS} < U_{thr}$  but  $U_{DS} < U_{GS} - U_{th}$ . Here the gate voltage is large enough, that a conducting channel is formed below the gate an connects source and drain contact.  $V_{GS}$  control the charge density in the channel and thereby its "resistance". The transistor behaves like an adjustable resistor.

SATURATION  $U_{GS} < U_{thr}$  and  $U_{DS} >= U_{GS} - U_{th}$ . The channel is "pinched-off" which leaves only a little dependence of th current on  $U_{DS}$ due to channel length modulation which is minimal for long transistors. The transistor has a very large output resistance  $R_{DS} = U_{DS}/I_{DS}$  and the transistor behaves as a voltage controlled current source  $I_{DS} = g_m * U_{GS}$ . Almost all transistors in analogue circuitry are operated in the state.

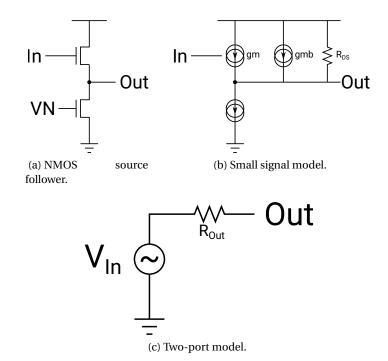

SUBSTRATE/BODY EFFECT Typically the source and bulk contact are shorted ( $U_{SB} = 0$ ). In some cases, e.g. for a source follower circuit as relevant later, this is not the case. As the conducting channel in the transistor is formed between bulk and gate. An increase of  $U_{SB}$ , will lead to an increase of  $U_{th} \propto \sqrt{U_{SB}}$ , referred as the bulk-effect. For a source follower this leads to a reduction of the amplification (< 1) which makes a non-ideal buffer element.

#### 3.2 PIXEL SENSOR TECHNOLOGIES

In today's world, pixel sensors are everywhere. Almost everyone carries around camera sensors in his pocket either a charge-coupled device (CCD) or active-pixel sensor(APS/CMOS sensor). The world's demand for integrated circuits greatly drives the advancement of micro electronics technology in the commercial sector which in turn feeds back into science, offering new, smaller technologies and chip handling techniques e.g. bump bonding and thinning processes down to  $10 \,\mu$ m [38]. In particle physics mostly two types of silicon devices are used: single-photon avalanche diodes (SPAD) which allow to build extremely small form-factor photo-multipliers and as discussed before sensors that just collect charge with a diode structure. In the following only the latter is relevant which forms the baseline for the most common tracking detector technologies.

#### 3.2.1 Hybrid pixel detectors

The charge collection diode structure and the front-end readout are produced as separate chips and hybridised in an additional production step, for pixel tracking detectors commonly flip-chip bump bonding of the two chips. While the front-end chip can be produced in commercially available processes, the diode structures need to be specifically developed and together with the hybridization step lead to high production costs. The possibility to combine one type of readout chip with different charge collection structures e.g. planar or 3D diode, but also electrodes in diamond, gives this detector a very high level of versatility. Figure 3.7 shows a typical cross section of a hybrid stack. The material budged of pixel modules with hybrid designs typically is larger then  $2\% X_0$  [39] (300 µm thick sensor). hybrid detectors are an established technology used to construct the largest tracking detectors in high energy physics and also form the baseline for the upgrade of the ATLAS and CMS pixel trackers. Their new front-end chip is developed in a joint venture of ATLAS and CMS in the RD53 collaboration [40].

Figure 3.7: A typical cross section of a hybrid sensor design. The diode is bump bonded to the front-end chip which processes the incoming current signal from the diode. Taken from [41]

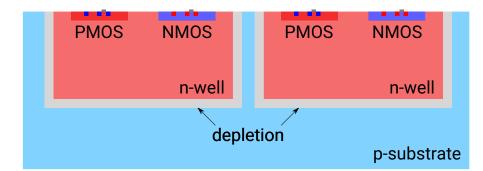

#### 3.2.2 Monolithic active pixel sensors (MAPS)

In contrast to the hybrid approach, monolithic designs combine detection and front-end electronics on the same chip. The use of commercially available CMOS processes and the avoidance of a hybridisation step reduce the production cost greatly and allows to equip large detector surfaces at much lower cost. Active pixels describe the combination of detection diode and pixel electronics inside the pixel structure. The detection diode of typical MAPS chips is only creating a small depletion zone and makes use of a process with an epitaxial layer (8 k $\Omega$  cm) to confine charges of crossing particles to a 20 µm thick layer . The charge collection via diffusion and the employment of low power front-end electronics limit the time resolution to the order of µs. At the same time the small charge collection region allows to thin away large portions of the initial wafers thickness and reduce the sensor thickness down to 50 µm which reduces the sensor material budget below 0.1% of radiation length.

The chips of the Mimosa series have pioneered this detector approach with the Mimosa26 sensor equipping the EUDET tracking telescopes [42] and the Ultimate-2 (Mimosa28) sensor used in the first large scale application as vertex detector in the STAR experiment [43]. Based on this development the ALPIDE chip was developed in the 180 n*m*-Towerjazz(TJ) process. The ALPIDE sensor [44] is used for the upgrade of the inner tracking system (ITS) of the ALICE experiment at CERN with a total detector surface of about  $10 \text{ m}^2$ .

Figure 3.8: Cross section view of the well structure of the ALPIDE MAPS chip [44]. The circuitry is implemented around the tiny n-well electrode in a deep-well separating it from the epitaxial layer.

#### 3.2.3 High voltage monolithic active pixel sensors (HV-MAPS)

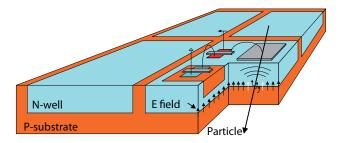

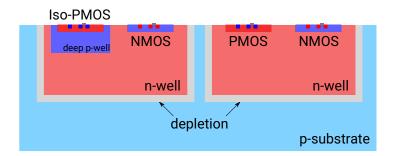

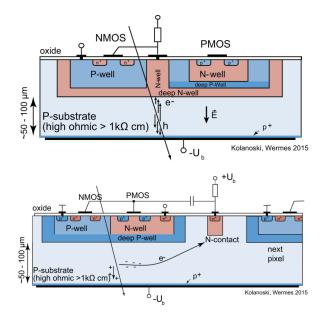

The usage of a depleted diode as detection element enables charge collection via drift, which allows the HV-MAPS principle [27] to combine the advantages of the monolithic approach with a fast charge collection, giving time resolutions in the order of ns. To produce the sensors commercially available HVCMOS processes are used, which are commonly used in automotive industry and guarantees low production costs. The employment of a deep n-well implant allows to apply a negative bias to the p-substrate which depletes the n-well p-substrate junction, representing the active detector volume, while at the same time implementing CMOS circuitry inside the n-well. A further advantage of the n-well pixelation is that a complete de-coupling of analogue circuitry and clocked logic is possible when they are placed in different n-wells, reducing the probability of crosstalk of the clocked domain into analogue electronics. HV-MAPS typically use substrate resistivities between (10-1000)  $\Omega$  cm and a reverse biases of (60-120) V. Like this the depletion zone thickness can be controlled and the remaining non-depleted silicon can be removed, conserving the material budget advantage of MAPS.

The combination of fast readout, good time resolution and controllable material budget this technology is a perfect fit for the Mu3e experiment and consequently chosen and further developed to enable the construction of the Mu3e pixel tracker.

Figure 3.9: Sketch of the HV-MAPS principle [27]. The pixel electronics is implemented inside the n-well electrode.

# 3.3 MUPIX10

Previous MuPix prototypes solved critical challenges in the maturing of the HV-MAPS technology, the high integration level of the readout [32] and the technology scaling to produce 2 cm long sensors while maintaining the excellent sensor performance [45]. For MuPix10 the design goal is to provide a full-scale HV-MAPS chip, which fulfils all requirements in his dimensions and connection interface to enable the production of Mu3e pixel tracker modules.

## 3.3.1 The HV-CMOS process

The MuPix10 is produced in a 180 nm HV-CMOS process, provided by TSI semiconductors <sup>1</sup>. Previous prototypes had been produced in the same process node by ams <sup>2</sup> which was discontinued. Both processes root on the original IBM 180 nm process which allowed a smooth transition. The TSI process was validated by resubmitting the MuPix7 design which showed no notable differences [46].

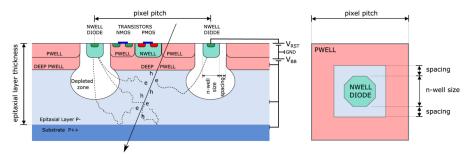

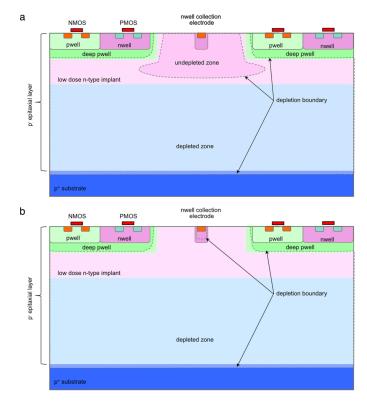

A cross section of the process is shown in figure 3.10. CMOS electronics is implemented in a deep n-well which are decoupled from each other as they form a depletion zone with the p-doped substrate. On one hand this allows to separate analogue and clocked digital electronics from each other and prevent crosstalk between them. On the other hand the depletion can also be used for particle detection.

Although the foundry typically uses standard substrate( $20 \Omega$  cm) for the chip manufacturing, they have been convinced to use higher-ohmic sub-

<sup>1</sup> TSI Semiconductors, USA, http://www.tsisemi.com

<sup>2</sup> ams AG, Austria, http://www.ams.com

Figure 3.10: The well structure of the used HV-CMOS process. The deep nwell forms a depleted diode with the substrate which can be used as active detector and allows to decouple electronics in different wells.

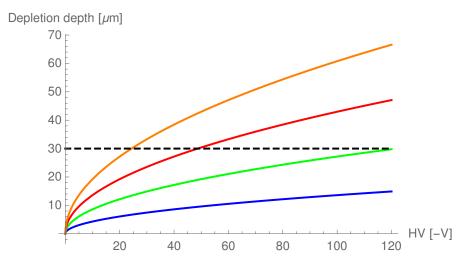

strates in the HV-MAPS engineering productions runs, as it allows to achieve larger depletion widths at the same high voltages  $w \propto \sqrt{\rho U}$ . The commonly used substrates are highlighted in table 3.1. For the production of MuPix10 the 200  $\Omega$  cm substrate was chosen to allow for a full depletion of the sensor after it was thinned down to 50 µm in case the breakdown voltage is similar to MuPix8 (-60 V). Figure 3.11 illustrates the depletion depth development for different resistivities.

| Name     | standard            | $80\Omega\mathrm{cm}$ | $200\Omega\mathrm{cm}$        |

|----------|---------------------|-----------------------|-------------------------------|

| Range    | (10-20) $\Omega$ cm | (50-100) $\Omega$ cm  | $(200-400) \Omega\mathrm{cm}$ |

| Measured | -                   | -                     | $369 \pm \Omega \mathrm{cm}$  |

Table 3.1: Substrate resistivity ranges used in HV-MAPS production.

# 3.3.2 Requirements

Table 3.2 lists the specification that the MuPix10 design needs to fulfil to enable the construction of sensor modules for the Mu3e pixel tracker. Aside the performance and overall dimensioning, the sensor is required to offer a connection interface, which allows to operate and readout the chip via a two layer aluminium high density interconnect(HDI) [47] which provides power, high voltage, configuration and readout. The interconnection with the chip is achieved by SpTa-bonding [48] of the aluminium traces to the chip, which requires large  $200 \times 100 \mu m^2$  bond pads.

# 3.3.3 The MuPix10 chip

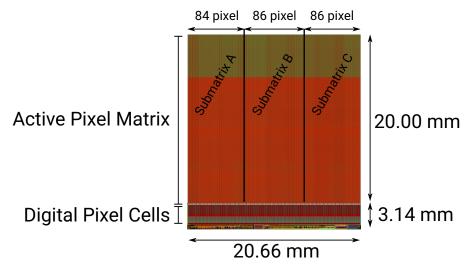

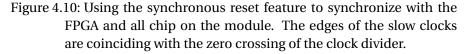

The chip layout is shown in figure 3.12 which show the typical separation of the chip into the active detection pixel matrix and the periphery housing the clocked circuitry to digitize and readout the pixel hits. Additionally the

Figure 3.11: The depletion depth depending on the applied reverse bias for different substrate resitivities. In rising order  $20 \Omega$  cm,  $80 \Omega$  cm,  $200 \Omega$  cm and  $400 \Omega$  cm resistivity.

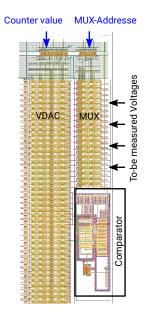

periphery contains digital-to-analogue converters (DAC) to steer the analogue circuitry as well as the bond pads. The periphery makes up 13% of the total chip surface of which 2.2% is the bond layout by itself.

Table 3.3 summarises the design dimensions which follow the Mu3e specifications. The total sensor size is here equivalent to the dicing size which leaves an  $11 \,\mu m$  silicon seal ring around the chips guard ring which allows to minimise the non active material in between two sensors on a module.

|                                         | Requirements    |

|-----------------------------------------|-----------------|

| pixel size [µm <sup>2</sup> ]           | $80 \times 80$  |

| sensor size [mm <sup>2</sup> ]          | $20 \times 23$  |

| active area [mm <sup>2</sup> ]          | $20 \times 20$  |

| active area [mm <sup>2</sup> ]          | 400             |

| sensor thinned to thickness [µm]        | 50              |

| LVDS links                              | 3 + 1           |

| maximum bandwidth [Gbit/s]              | $3 \times 1.25$ |

| RMS of spatial resolution [µm]          | ≤ 30            |

| power consumption [mW/cm <sup>2</sup> ] | ≤ 350           |

| time resolution per pixel [ns]          | ≤ 20            |

| efficiency at 20 Hz/pix noise [%]       | ≥ 99            |

| noise rate at 99% efficiency [Hz/pix]   | ≤ 20            |

Table 3.2: The Mu3e pixel sensor specifications [17].

The sensors are available in various thickness and two resistivities which allow for detailed studies of possible influences by the thinning process in the future. In this work only a  $100 \,\mu\text{m}$ ,  $200 \,\Omega$  cm sensor will be investigated.

## 3.3.3.1 The Chip Design

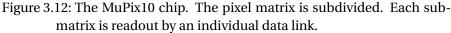

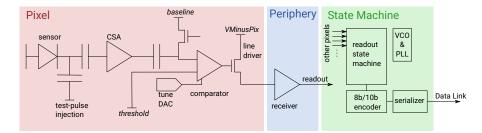

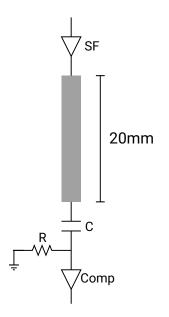

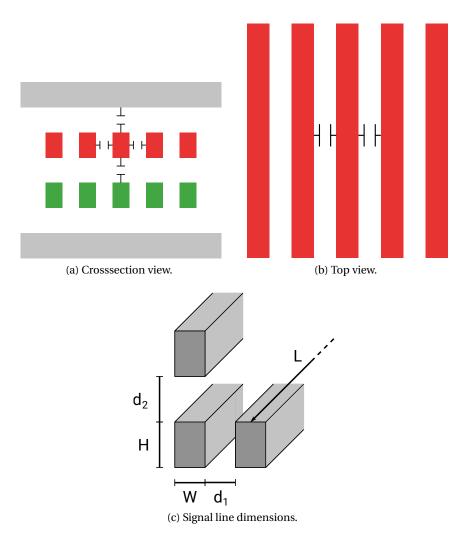

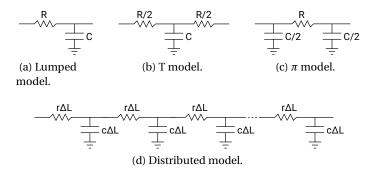

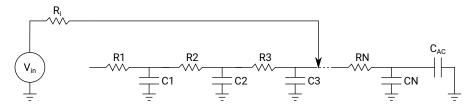

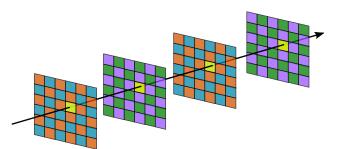

The sensor architecture follows the same principle as previous prototypes, sketched in figure 3.13. The active pixel consists of a deep n-well which forms a detection diode with the substrate material and is housing a charge sensitive amplifier (CSA) for signal amplification and a source follower (SF) as buffering driver element which loads the long metal line forming the point-to-point connection of the active pixel to the corresponding digital cell in the periphery. Here the arriving analogue pulse of the active pixel is digitised and the data is subsequently readout in a column-drain fashion. The data is serialised by the on-chip state machine and send out via 1.25 Gbit/s links. Each pixel sub-matrix is readout individually with its own

|                                  | MuPix10                  |

|----------------------------------|--------------------------|

| pixel size [µm <sup>2</sup> ]    | $80 \times 80$           |

| sensor size [mm <sup>2</sup> ]   | $20.66 \times 23.18$     |

| columns × rows                   | $256 \times 250$         |

| active area [mm <sup>2</sup> ]   | $20.48 \times 20$        |

| active area [mm <sup>2</sup> ]   | 400                      |

| sensor thinned to thickness [µm] | 50, 60, 70, 80, 100, 625 |

| resistivity [ $\Omega$ cm]       | 20, 200                  |

Table 3.3: The MuPix10 sensor dimensions.

1.25 Gbit/s link. A fourth additional link is provided which offers a data stream merged from the three sub-matrices.

Figure 3.13: The MuPix electronic structure.

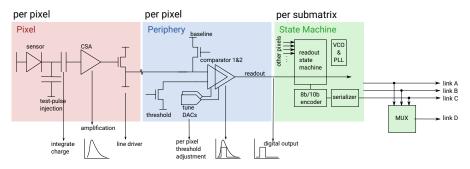

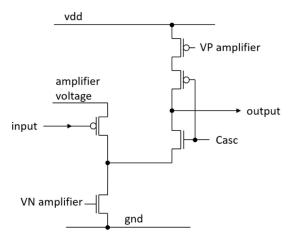

THE PIXEL ELECTRONICS The in-pixel electronics is sketched in figure 3.14. The charge sensitive amplifier is build from a folded-cascode gain stage with a PMOS input transistor, pictured in figure 3.15, with a feedback circuit providing a constant current creating a linear falling edge, which leads to a linearised connection between pulse height and pulse duration. The drain contact of the PMOS cascode transistor forms a parasitic capacity with the deep n-well, which is used as the feedback capacity of the CSA  $(C_f = 1.6 \text{ fF})$ . As a result the pulse height is proportional to the deposited charge  $(Q_{dep})$ . To mimic a charge deposition the input of the amplifier also allows to inject charges via a capacitance.

$$U_{pulse} \approx \frac{Q_{dep}}{C_f} \tag{3.10}$$

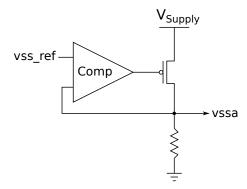

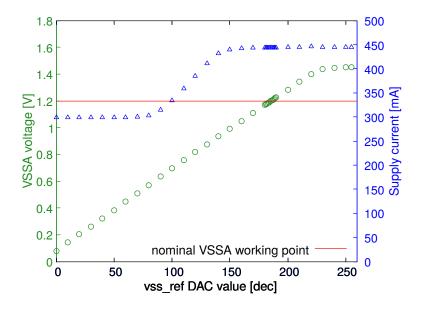

A detailed discussion of the amplifier can be found in [49]. The amplifier is not meant to drive a large output capacitance, therefore it is connected to a NMOS source follower which drives the long point-to-point connection into the periphery. As shown in figure 3.15 the gain stage requires an additional "amplifier voltage" which is called VSSA ((1.0-1.2) V). As for the Mu3e pixel tracker modules only one supply voltage is available, this voltage needs to be generated on chip.

The architecture of the regulator is sketched in figure 3.16. It is a linear series regulator which uses a differential amplifier to adjust the VSSA voltage level to a configurable reference value (vss\_ref). As the regulator acts as a self adjusting voltage divider the current drawn by the (1.0-1.2) V network will dissipate additional heat in the regulating transistor leading to a power penalty.

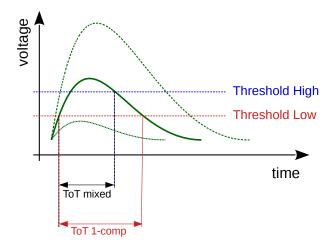

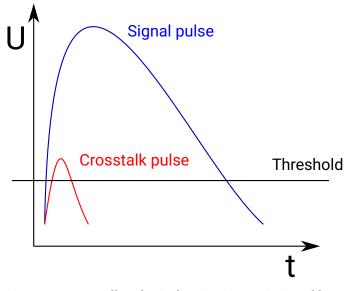

THE DIGITAL CELL The analogue pulse arriving on the signal line is AC coupled to a system of two comparators with individual thresholds. As depicted in figure 3.17 two modes are selectable, either only one of the comparators is used to sample the pulse or both with shared tasks. In the case of 1-comparator mode additionally to a hit flag, a time of arrival (ToA)

Figure 3.14: The in-pixel electronics. vss=VSSA

Figure 3.15: Folded cascode amplifier with a PMOS input transistor. vdd=vdda

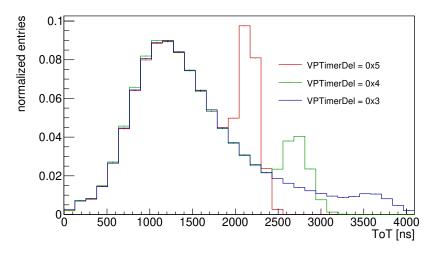

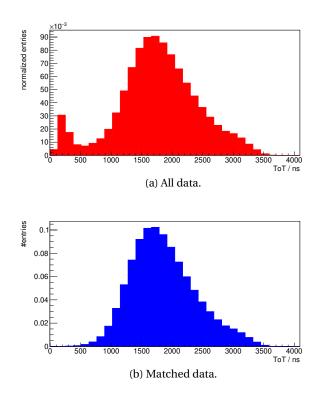

timestamp will be stored when the pulse surpasses the comparator threshold. The timestamp is 11 bit wide with a 8 ns binning. When the pulse drops again below the threshold a second 5 bit timestamp (TS2) is stored typically with 128 ns binning to cover a pulse duration range of 4  $\mu$ s. The subtraction of the time of arrival allows to calculate a time-over-threshold (ToT) which is a measure of the deposited energy.

$$ToT = TS2 - ToA \tag{3.11}$$

As also highlighted in figure 3.17 the time of arrival that is stored will dependent on the pulse height. Larger pulses will cross the threshold earlier which is referred to as timewalk. The effect can be reduced either by lowering the threshold, which reduces the timewalk spread, or by measuring the ToT and correcting for effect later. A lowering of the threshold is leading to an increase of noise induced hits. To overcome this the two-threshold

Figure 3.16: Functional sketch of the linear regulator.

Figure 3.17: The digitisation of the analogue pulse by the comparators.

method was implemented which allows to sample a less timewalk affected ToA on the lower threshold and the hit flag and second timestamp on a noise free, higher threshold.

Due to variations of process parameters during the production of the chip. All comparators will behave slightly different, an effect commonly referred to as threshold-dispersion, as individual comparators require different threshold voltage levels to exhibit the same performance. To reduce this effect the comparators are equipped with a 3 bit trimming circuit which allows for an individual adjustment of the comparators, also referred to as tuning.

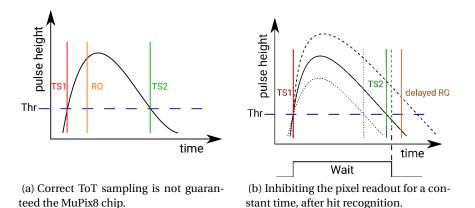

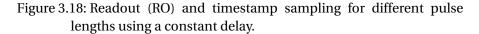

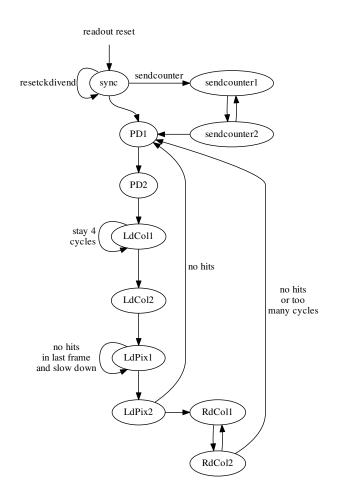

In MuPix8 it was discovered that the sampling of the second timestamp is jeopardized [50]. As depicted in figure 3.18a the hit is possibly readout before TS2 is sampled, therefore invalidating the ToT information. To guarantee a correct ToT measurement and subsequently enabling the possibility of timewalk correction, the scheme pictured in figure 3.18b is implemented in MuPix10. When the hit flag is set by the comparator a delay period start which is the same for all pixels inhibiting the readout until the TS2 was sampled. As the delay is the same for all pixels, the time ordering of the readout hits remains unchanged. A desired effect, as it simplifies the time sorting process which is part the Mu3e readout chain.

Figure 3.19 shows a sketch of the new analogue delay circuit. The registered hit enables a current source which charges up a capacitor. The increasing voltage of the capacitor is measured by a discriminating element which switches when its threshold is crossed. This output enables the readout of the pixel cell. The strength of the current source is adjustable and thus the time delay. A detailed description of the digital cell and the circuitry is presented in [51].

Figure 3.19: The delay circuit logic. (The reset circuit is not shown.)

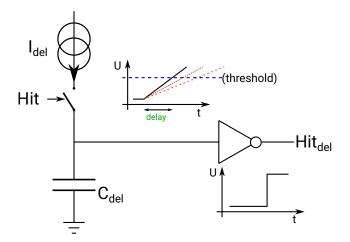

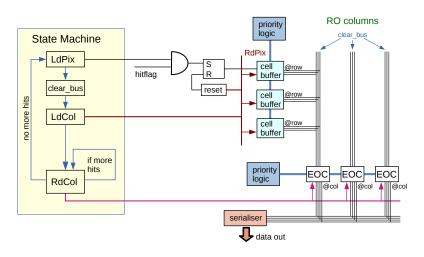

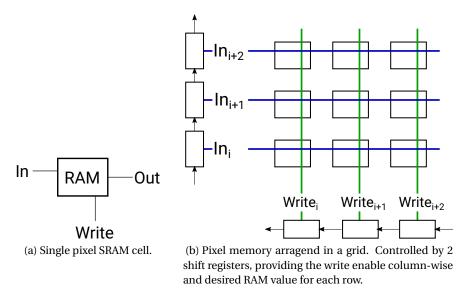

THE READOUT The registered hits are readout in a column-drain approach, with each column forming an OR-chain of the hit flags, the priority signal, indicating if a hit is to be readout in the respective column. If the OR-chain signals a hit, the information of the hit lowest in the column is copied to the end-of-column(EoC) buffer and from there further to the data serialiser, as depicted in figure 3.20. The signals required to copy data, clear buses and reset hit flags are orchestrated by a synthesised finite-state

machine, shown in figure 3.21. A full description of the readout procedure can be found in [52].

Figure 3.20: The column-drain readout scheme.

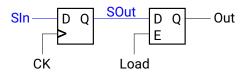

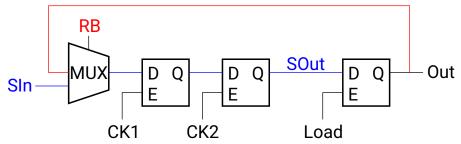

The readout state machine transitions the states nominally with a frequency of 62.5 MHz. On every second state a data word is sampled and serialised for readout as illustrated in table 3.4. With the priority logic acting as zero-suppression and the state machine running independent of any external signals, e.g. trigger signals, it constantly sends out data over a 1.25 Gbit/s link, referred to as streaming readout. A sub-matrix of MuPix10 has a theoretical maximum readout capacity of 30 MHits/s. With three sub-matrices readout individually 90 MHits/s. For MuPix8 the readout was tested for hit rates larger then 10 MHits/s [52]. As the data format contains a sizeable amount of fill words. These free data slot can be used for a different purpose (chapter 4).

FURTHER OPTIMISATIONS Aside from the already mentioned changes, namely the regulator and the readout delay, two more mayor adaptations have been implemented and are the main subject of this work. In section 4 the development and implementation of the Mu3e configuration interface is described, aiming for a reduction of signals required for the sensor configuration, which is driven by the very limited routing space available on the HDI. Section 5 describes the optimisation of the routing scheme of the pixel point-to-point connections to reduce crosstalk between signal lines and the position dependent delay. Both have been prominently observed in MuPix8.

# 3.3.3.2 Results

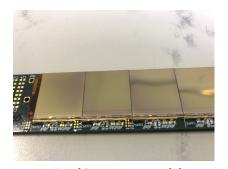

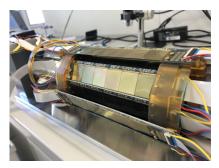

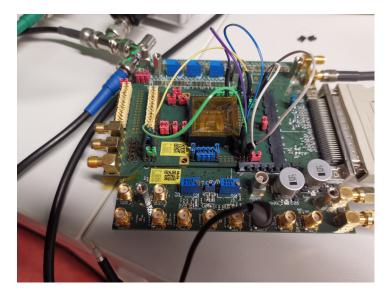

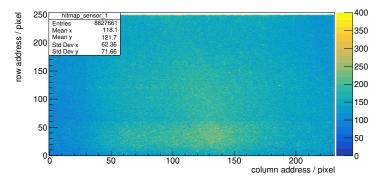

The MuPix10 chip was successfully commissioned and is currently being routinely operated and intensively tested in laboratory measurements and testbeam campaigns. For the testing of single chips, the sensor is mounted onto a specifically designed PCB-card as depicted in figure 3.22a and is con-

Figure 3.21: State diagram of the readout state machine. Taken from [52].

figured and readout via the DAQ system presented in [53]. In the following the main findings are highlighted as they are guiding final polishing process for a resubmission of MuPix10 with minimal changes as the chip for the Mu3e pixel tracker, MuPix11.

BREAKDOWN VOLTAGE It was found that the breakdown voltage improved drastically in comparison to MuPix8 which was approximately at -60 V. For MuPix10 the breakdown was found to occur at -115 V and by default operated at -100 V which corresponds to a depletion depth of around  $60 \mu$ m. With the improved breakdown voltage a reduction of the resistivity is possible as also at  $80 \Omega$  cm a depletion depth of  $30 \mu$ m is achievable.

THE VSSA REGULATOR & POWER CONSUMPTION So far in depth study of the regulator has been performed, however, the ad-hoc usage of the regulated voltage as VSSA supply was successful and is the default mode of operation. Figure 3.23 shows a scan of the regulator reference volt-

| readout state | data                   | data type      |  |

|---------------|------------------------|----------------|--|

| PD1           |                        |                |  |

| PD2           | bc bc bc bc            | komma          |  |

| LdCol1<1>     |                        |                |  |

| LdCol1<2>     | bc bc bc bc            | komma          |  |

| LdCol1<3>     |                        |                |  |

| LdCol1<4>     | bc bc bc bc            | komma          |  |

| LdCol1<5>     |                        |                |  |

| LdCol1<6>     | bc bc bc bc            | komma          |  |

| LdCol1<7>     |                        |                |  |

| LdCol2        | lc aa lc aa            | hit identifier |  |

| LdPix1        |                        |                |  |

| LdPix2        | chip time              | chip timestamp |  |

| RdCol1        |                        |                |  |

| RdCol2        | address and timestamps | hit data       |  |

Table 3.4: The data structure of the MuPix readout state machine. Every second state samples an serialises a data word. Some states sending the Komma word K28.5 (0xbc) as filler. The identifier 0xaa for sub-matrix A with Komma flag 0x1c (K28.0).

age. The VSSA level shows a linear behaviour with a range from (0-1.4) V with the nominal working point of 1.2 V well covered. Further, the corresponding changes in the supply current are plotted. As the amplifier is the only circuit using the VSSA voltage; the change in current represents the turn-on of the amplifier. Only for voltage levels above 1 V the amplifier can be considered fully working.

As the VSSA-regulator is working, the default sensor operation is using only a single supply voltage, shorting analogue and digital domains, while providing VSSA via the regulator. With the help of test point inside the chips power grid it was found, that there is considerable voltage drop from the supply voltage connection pads and the power grid, which was confirmed by the layout as narrow wires. To compensate for these voltage drops a larger supply voltage needs to be applied, 2.25 V. Only with this over-voltage the analogue domain (VDDA), which suffers the largest drop, reaches its nominal working voltage of 1.8 V. The digital domain (VDD) is operated at an over voltage. This is easily fixed in MuPix11.

Table 3.5 shows the resulting voltages and currents in the individual domains if a single supply voltage of 2.25 V is applied. Assuming the currents remain almost unchanged if their nominal working points of 1.8 V are reached, the contribution of the voltage drop can be calculated out. Leaving only the bare power consumption of the sensor.

$$P_{MuPix10} = V_{Supply} * I_{Supply}$$

(3.12)

(a) A MuPix10 chip mounted on a test PCB.

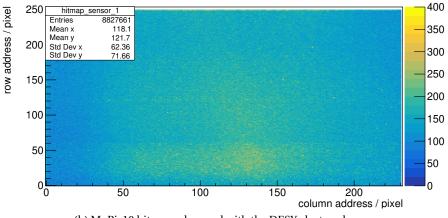

(b) MuPix10 hit map observed with the DESY electron beam.

Figure 3.22: The MuPix10 is routinely operated, glued and wire bonded to a specifically designed test PCB.

| Domain              | V <sub>Supply</sub> | VSSA | VDDA | VDD  |

|---------------------|---------------------|------|------|------|

| In-chip voltage [V] | 2.25                | 1.0  | 1.8  | 2.1  |

| Current [A]         | 0.58                | 0.22 | 0.23 | 0.13 |

Table 3.5: Substrate resistivity ranges used in HV-MAPS production.

The total power consumption in the mode of a single supply voltage amounts to  $P_{MuPix10} = 1.305$  W. Normalised to the total chip surface of  $2 \times 2.3$  cm<sup>2</sup> this gives 280 mW/cm<sup>2</sup>. Corrected for the power dissipation in the undesired wire resistances  $P_{corrected} = 0.858$  W or 186 mW/cm<sup>2</sup>. This number misses the power penalty of the VSSA regulator which is  $P_{Penalty} =$  $(1.8V - 1V) * I_{VSSA} = 0.168$  W which gives a total power consumption estimation for a MuPix10 with no voltage drops connected to a single supply

Figure 3.23: VSSA voltage and vdda current plotted for a scan of the regulator reference voltage.

voltage of 222 mW/cm<sup>2</sup>. Both values with and without voltage drop suffice the Mu3e requirement, but the voltage drop increases the power consumption by 25%.

Figure 3.24: ToT spectra obtained for 3 different delay times controlled by the VPTimerDel DAC value.

THE DELAY CIRCUIT Figure 3.24 shows three measured ToT distributions with different chosen delays. The peak in the end of the spectrum corresponds to the delay time. If the delay time lapsed, but the ToT of the pulse would be even longer, the expiring time of the delay is sampled instead. All pulses longer than the delay are contained in this peak. The dispersion of the peak is caused by variations of the delay time over the chip and is on an acceptable level for the usage in Mu3e. As long pulses correspond to a large signal amplitude, there is no need for a timewalk correction. Hence, the delay time can be reduced below the duration of the longest pulses without loosing precision in the correction process.

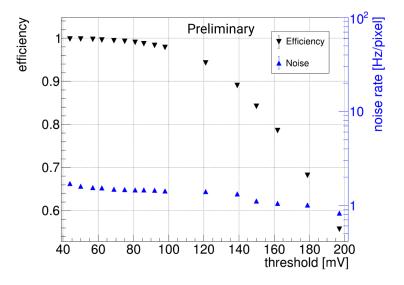

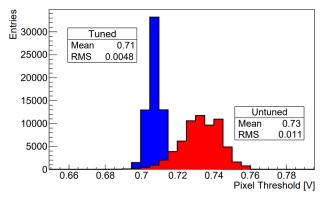

EFFICIENCY & NOISE Figure 3.25 shows an exemplary result of a scan of the discriminator threshold voltage determining crosstalk and noise for each point with the help of the MuPix-telescope [53].

For low thresholds the efficiency reaches a larger plateau with efficiencies well above 99.9% while maintaining an average noise-per-pixel rate below 2 Hz.

An in-depth study of the HV-dependence [54] and the influence thinning of the sensor on the efficiency is currently ongoing.

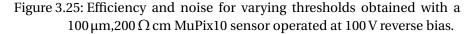

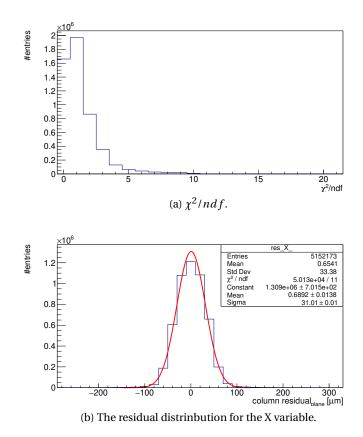

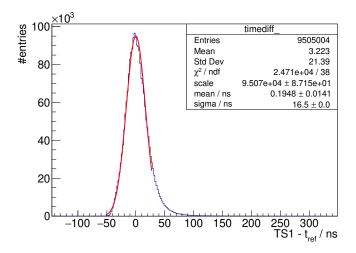

TIME RESOLUTION The degrading effect of pixel position dependent delays and the timewalk on the sensor time resolution is well understood [50] and was immediately investigated for MuPix10 [55] with the result highlighted in figure 3.26.

(b) Exemplary MuPix10 time resolution for raw and corrected data.

# Figure 3.26: The MuPix10 time resolution with the compensation of the onchip voltage drops and further optimised settings.

With the help of the analytical delay and time walk compensations developed [55] time resolution of 7 ns are achievable. The investigation of the time resolution on a pixel to pixel base revealed an intrinsic pixel time resolution of  $(6 \pm 1 \text{ ns})$ . The time resolution goal of the Mu3e specifications is very well met with and without correction.

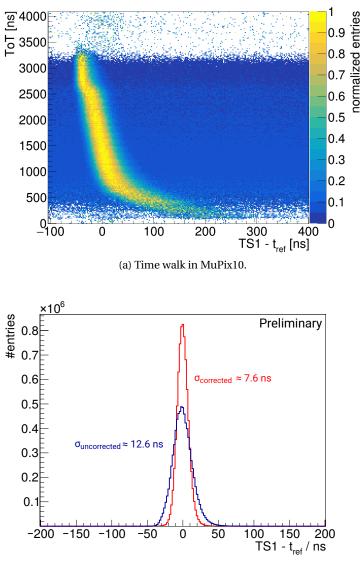

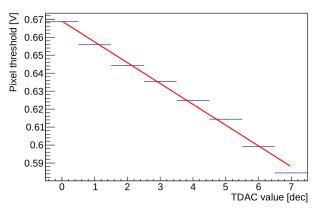

SENSOR TUNING All pixels are connected to two comparators with globally applied thresholds. In the MuPix10, both comparators are equipped with a 3 bit DAC which allows to set individual threshold to compensate the variations, the so-called trimming or tuning. Additionally, the pixels have a switch bit, which allows to mute pixels if they are uncontrollably noisy. This feature was tested and a tuning was performed successfully [56].

In this study all pixels have been stimulated with charge pulses corresponding to  $3000 \,\mathrm{e^-}$ , using the injection infrastructure, see figure 3.13. A scan of the global threshold is performed and the amount of recognised injection pulses is measured. The resulting distribution is fitted with an s-curve function. The mean value extracted from this fit varies for different pixels. The RMS of the mean-distribution plotted in figure 3.27b is a measure of the threshold dispersion. With the application of individual threshold shifts, shown in figure 3.27a, the differences of the mean values can be minimised, reducing the dispersion over all pixels.

(a) Commissioning measurement to check the linearity of the 3 bit tuning DAC. Linear fit in red.

(b) The threshold dispersion before (red) and after (blue) tuning for the full MuPix10 matrix with an equivalent signal of  $3000 \, e^-$ .

Figure 3.27: Results obtained with the threshold tuning method [56].

With this method the threshold dispersion was reduced from 11 mV to 4.8 mV or in electron equivalent from  $240 \text{ e}^-$  to  $75 \text{ e}^-$ , see figure 3.27b. The

effect of the tuning on the efficiency still needs to be investigated in testbeam campaigns.

ISSUES As its predecessor MuPix8, also MuPix10 can not be reliably operated with the readout state machine at full speed which halves the maximum readout speed to 45 MHits/s, still enough to handle the high rates of Mu3e phase 1. The origin of this problem is under investigation to possibly find a fix of the issue for the MuPix11 chip.

Further a reset issue was discovered in one of the chips registers which leads to an immediate loss of the chips configuration after the configuration written(loaded). Although a work-around was possible which allows to fully use the sensor, this bug affects the testability of Mu3e configuration interface. A fix of this issue for the MuPix11 submission is already prepared.

# 3.3.4 Towards MuPix11

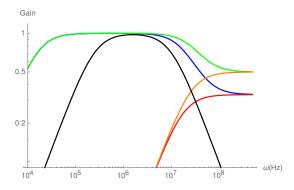

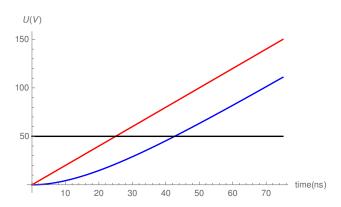

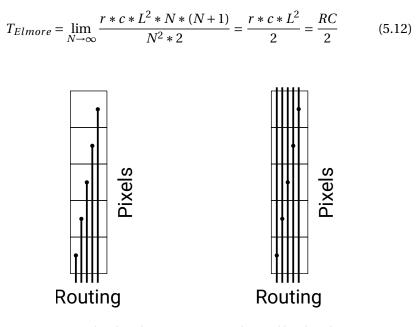

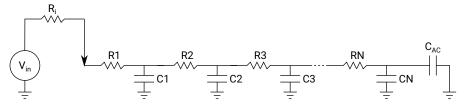

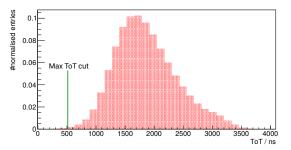

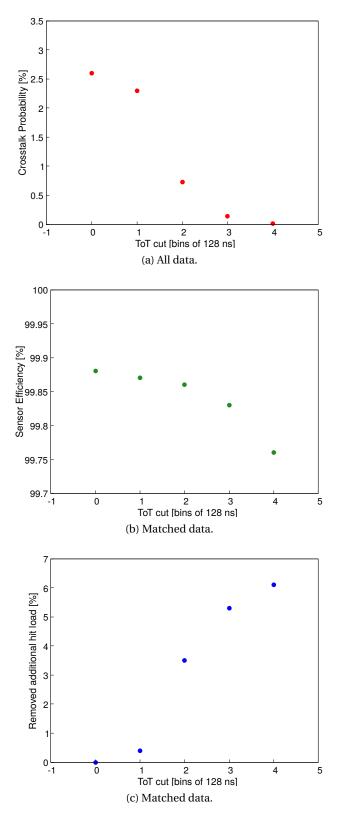

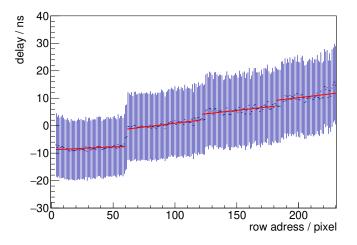

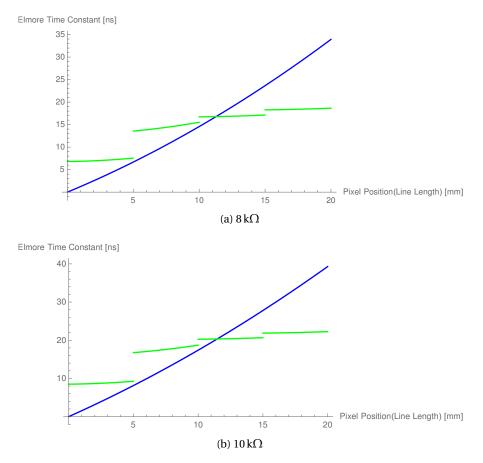

Table 3.6 summarises the MuPix10 properties given by design or measured as presented above. A comparison with the Mu3e specifications shows that all requirements are met. However, these results represent a  $100 \,\mu\text{m}$  thick sensor. They need to be confirmed for a MuPix10 with 50  $\mu\text{m}$  thickness.