ruprecht-karls-UNIVERSITÄT HEIDELBERG

PHYSIKALISCHES I N S T I T U T

Development of the control system of the ALICE Transition Radiation Detector and of a test environment for quality-assurance of its front-end electronics

# Dissertation

Jorge Mercado Pérez

Supervisor:

Prof. Dr. Johanna Stachel

Physikalisches Institut, Universität Heidelberg

Heidelberg, September 2008

# Dissertation

submitted to the

Combined Faculties for the Natural Sciences and for Mathematics of the Ruperto-Carola University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

> Put forward by M. Sc. Jorge Mercado Pérez Born in: Mexico City, Mexico

Oral examination: November 10, 2008

Development of the control system of the ALICE Transition Radiation Detector and of a test environment for quality-assurance of its front-end electronics

Referees:Prof. Dr. Johanna StachelProf. Dr. Hans-Christian Schultz-Coulon

# Entwicklung des Kontrollsystems für den ALICE Übergangsstrahlungsdetektor und eines Test-setups zur Qualitätssicherung der front-end Elektronik

Im Rahmen dieser Arbeit wurde das Detektor-Kontroll-System (DCS) für den Übergangsstrahlungsdetektor (TRD) des ALICE Experiments am Large Hadron Collider entwickelt. Das TRD Kontrollsystem ist vollständig implementiert als eine detektororientierte Hierarchie von Objekten, welche sich wie End-Zustandsautomaten verhalten. Es kontrolliert und überwacht über 65 tausend front-end Elektronik (FEE) Einheiten, einige hundert low-voltage und eintausend high-voltage Kanäle, sowie weitere Subsysteme wie Kühlung und Gasversorgung. Die Inbetriebnahme des TRD Kontrollsystems fand während mehrerer Datennahmen mit ALICE unter Verwendung von Ereignissen aus der kosmischen Strahlung statt.

In einem weiteren Teil dieser Arbeit wurde ein Test-setup zur Qualitätssicherung der Massenproduktion von über viertausend FEE Readout-boards mit insgesamt 1.2 Millionen elektronischen Auslesekanälen des TRD entwickelt. Die Hardware- und Softwarekomponenten werden im Detail beschrieben. Zusätzlich wurde vorher eine Reihe von Leistungsuntersuchungen durchgeführt, welche die Strahlungstoleranz des TRAP-chips überprüft, der den Hauptbestandteil der TRD-FEE darstellt.

## Development of the control system of the ALICE Transition Radiation Detector and of a test environment for quality-assurance of its front-end electronics

Within this thesis, the detector control system (DCS) for the Transition Radiation Detector (TRD) of the ALICE experiment at the Large Hadron Collider has been developed. The TRD DCS is fully implemented as a detector oriented hierarchy of objects behaving as finite state machines. It controls and monitors over 65 thousand front-end electronics (FEE) units, a few hundred low voltage and one thousand high voltage channels, and other sub-systems such as cooling and gas. Commissioning of the TRD DCS took place during several runs with ALICE using cosmic events.

Another part of this thesis describes the development of a test environment for large-scale production quality-assurance of over 4 thousand FEE read-out boards containing in total about 1.2 million read-out channels. The hardware and software components are described in detail. Additionally, a series of performance studies were carried out earlier including radiation tolerance tests of the TRAP chip which is the core component of the TRD FEE.

# Contents

Abstract

| De |            | Interes  | Justen Meterial          | 1  |

|----|------------|----------|--------------------------|----|

| Pa | rt I -     | - Introd | ductory Material         | 1  |

| 1  | Intr       | oducti   | on                       | 3  |

| 2  | The        | LHC      | and experiments          | 11 |

|    | 2.1        | The ac   | celerator                | 11 |

|    |            | 2.1.1    | Luminosity               | 12 |

|    |            | 2.1.2    | The LHC layout           | 13 |

|    |            | 2.1.3    | The accelerator complex  | 15 |

|    | 2.2        | Experin  | ments at the LHC         | 16 |

|    |            | 2.2.1    | ATLAS                    | 17 |

|    |            | 2.2.2    | CMS                      | 17 |

|    |            | 2.2.3    | LHCb                     | 18 |

|    |            | 2.2.4    | ALICE                    | 19 |

|    |            | 2.2.5    | ΤΟΤΕΜ                    | 19 |

|    |            | 2.2.6    | LHCf                     | 19 |

| 3  | <b>6</b> 1 | 4.7.70   |                          |    |

| J  | The        | ALIC     | CE experiment            | 21 |

|    | 3.1        | Purpos   | e and physics motivation | 21 |

|    | 3.2        | The Al   | LICE detector            | 22 |

|    |            | 3.2.1    | Central barrel detectors | 22 |

|    |            | 3.2.2    | Forward detectors        | 27 |

|    |            | 3.2.3    | Muon spectrometer        | 28 |

|    | 3.3        | Trigger  | r and data acquisition   | 28 |

vii

68

70

75

|    |       | 3.3.1   | Pre-trigger system                 | 29         |

|----|-------|---------|------------------------------------|------------|

|    |       | 3.3.2   | L0, L1, L2 trigger levels          | 29         |

|    |       | 3.3.3   | High-Level Trigger                 | 30         |

|    |       | 3.3.4   | Data acquisition                   | 30         |

| 4  | The   | ALIC    | CE TRD                             | 31         |

|    | 4.1   | Transit | ion radiation                      | 31         |

|    | 4.2   | Detect  | or requirements and design         | 32         |

|    |       | 4.2.1   | Physics requirements               | 32         |

|    |       | 4.2.2   | Detector design                    | 33         |

|    | 4.3   | Reado   | ut and basic infrastructure        | 37         |

|    |       | 4.3.1   | Readout electronics chain          | 37         |

|    |       | 4.3.2   | Low voltage                        | 38         |

|    |       | 4.3.3   | High voltage                       | 38         |

| Pa | rt II | – TRD   | FEE quality assurance              | 41         |

| 5  | TR    | D fron  | t-end electronics                  | 43         |

|    | 5.1   |         |                                    | <b>4</b> 5 |

|    | 0.1   | 5.1.1   | Preamplifier and shaping amplifier | 46         |

|    |       | 0.1.1   |                                    | .0         |

|   |     | 5.1.2   | The Tracklet Processing chip                           | 48 |

|---|-----|---------|--------------------------------------------------------|----|

|   | 5.2 |         | It Board                                               |    |

|   | 5.3 | Additic | nal components                                         | 53 |

| 6 | Rad | iation  | and performance studies                                | 57 |

|   | 6.1 | Radiati | on tests of the TRAP chip                              | 57 |

|   |     | 6.1.1   | Radiation in the TRD $-$ quantities and units $\ldots$ | 58 |

|   |     | 6.1.2   | Radiation effects in electronic devices                | 60 |

|   |     | 6.1.3   | Experimental setup                                     | 63 |

|   |     | 6.1.4   | Test procedure                                         | 64 |

|   |     |         |                                                        |    |

6.1.5

6.1.6

Total dose calculation

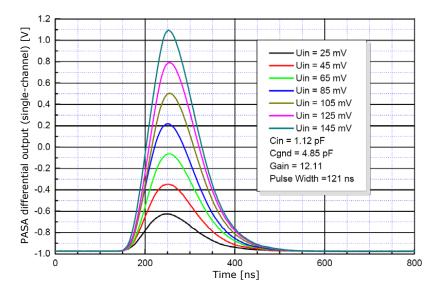

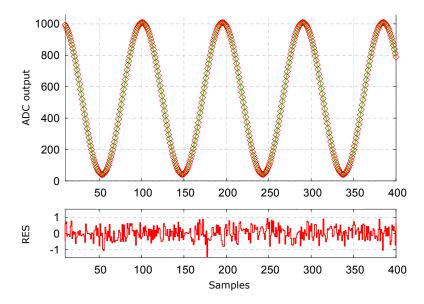

6.2 PASA characterization

|   | v |   |  |

|---|---|---|--|

| 1 | ~ |   |  |

| 4 |   | • |  |

| 6.3   | MCM    | testing                              | I |

|-------|--------|--------------------------------------|---|

|       | 6.3.1  | Digital tests                        |   |

|       | 6.3.2  | Test equipment    82                 |   |

|       | 6.3.3  | Analog tests                         |   |

|       | 6.3.4  | Outlook                              |   |

| 7 Der | velopm | ent of the ROB test system 85        | , |

| 7.1   |        | FEE quality assurance considerations | , |

| 7.2   | Systen | n requirements                       | , |

| 7.3   | Systen | n description                        | , |

|       | 7.3.1  | The slow control serial network      |   |

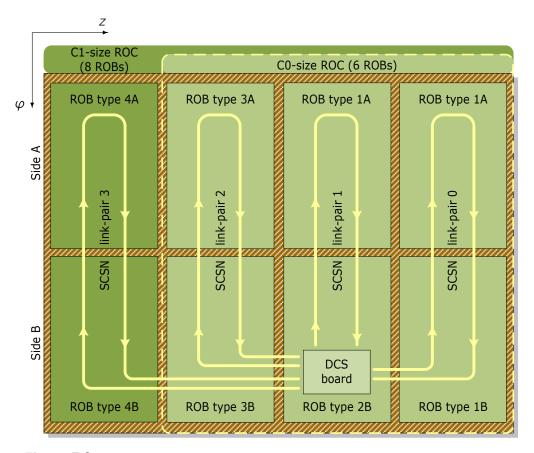

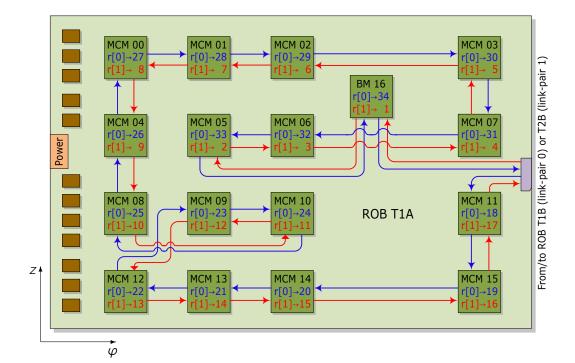

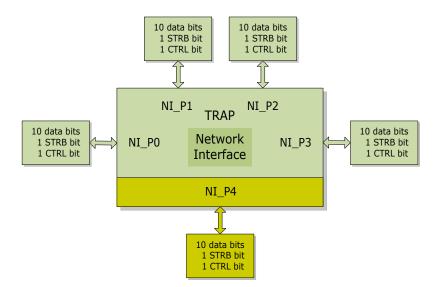

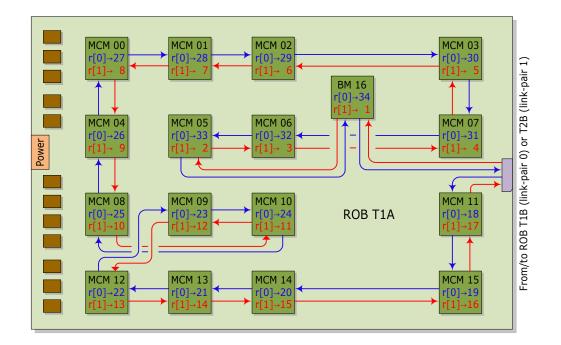

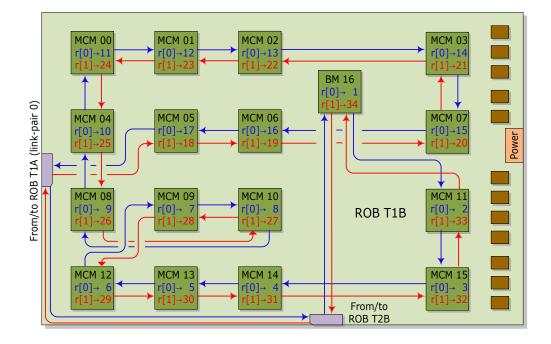

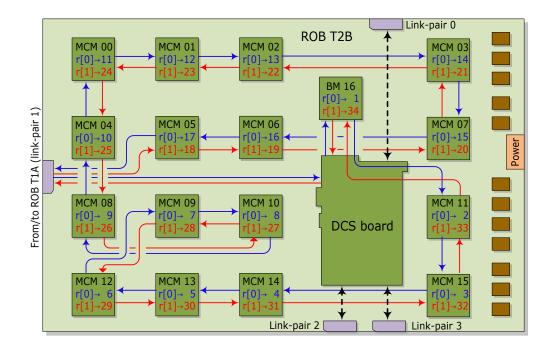

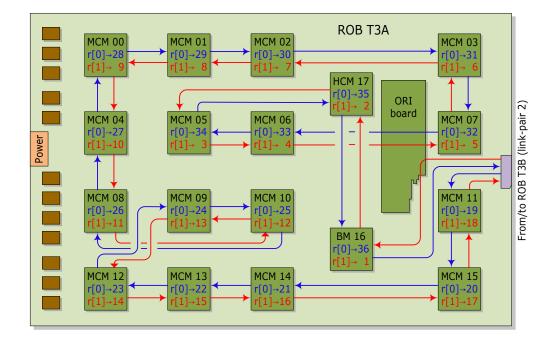

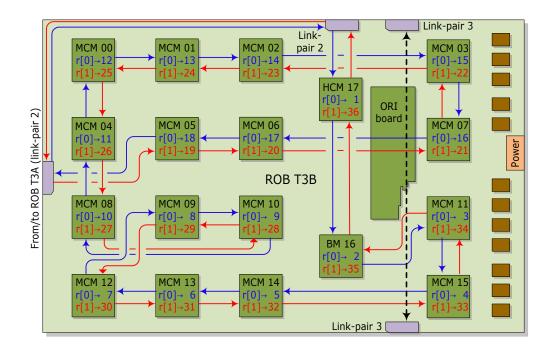

|       | 7.3.2  | SCSN architecture on the ROC         | 5 |

|       | 7.3.3  | SCSN architecture on the ROB         | J |

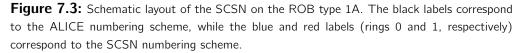

|       | 7.3.4  | The readout network interface        |   |

|       | 7.3.5  | The readout scheme on the ROC        |   |

|       | 7.3.6  | The readout scheme on the ROB        | , |

| 7.4   | ROB t  | test system hardware                 | j |

|       | 7.4.1  | ACEX board                           | 1 |

|       | 7.4.2  | ORI board                            |   |

|       | 7.4.3  | Single-MCM board                     |   |

| 7.5   | Hardw  | vare implementation                  | I |

|       | 7.5.1  | ROB test system Class I              | I |

|       | 7.5.2  | ROB test system Class II             | I |

|       | 7.5.3  | Hardware constraints                 |   |

| 7.6   | ROB t  | test system software                 | 1 |

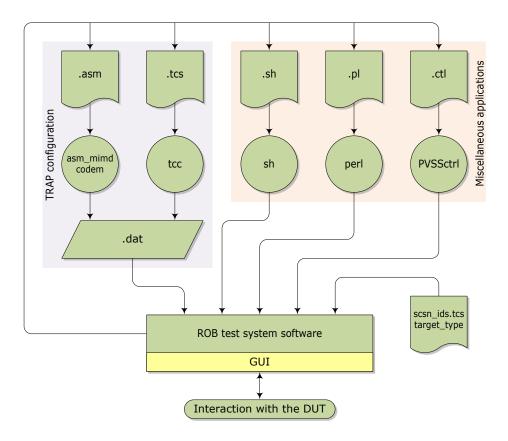

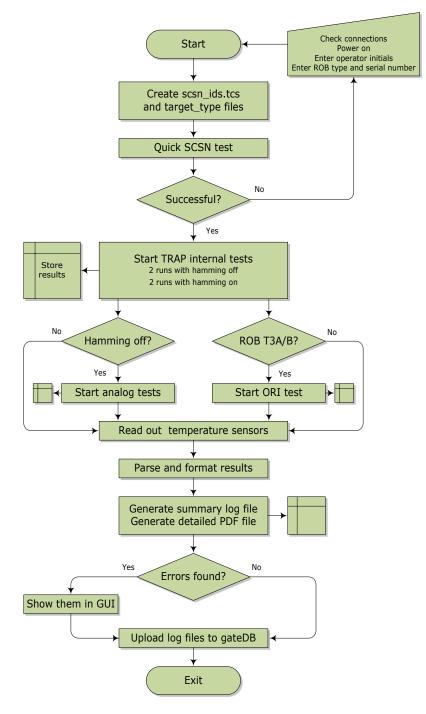

|       | 7.6.1  | Software architecture                |   |

|       | 7.6.2  | Software design                      | 1 |

| 7.7   | Softwa | are implementation                   |   |

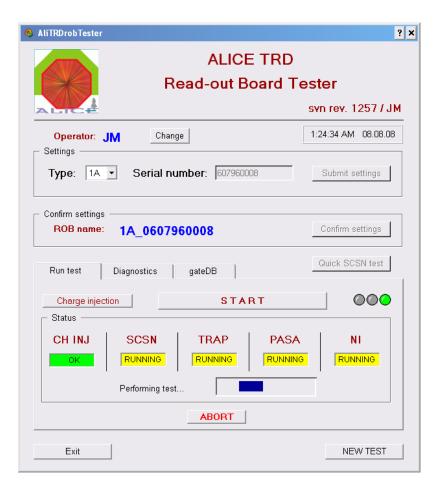

|       | 7.7.1  | The graphical user interface         | I |

|       | 7.7.2  | Miscellaneous applications           |   |

|       | 7.7.3  | The TRAP internal tests              |   |

| 7.8   | Result | s                                    |   |

| Part II     | I – The         | e TRD control system                         | 127   | , |

|-------------|-----------------|----------------------------------------------|-------|---|

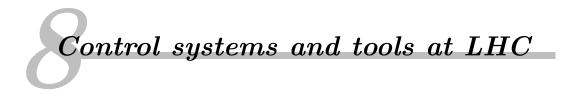

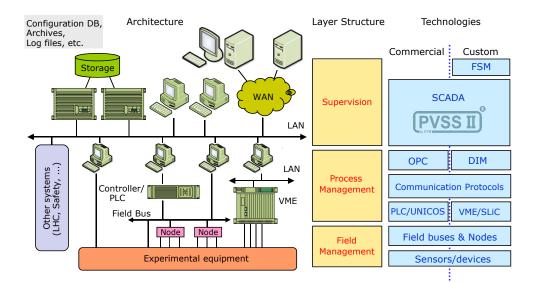

| 8 Con       | $ntrol \ s_{2}$ | ystems and tools at LHC                      | 129   | J |

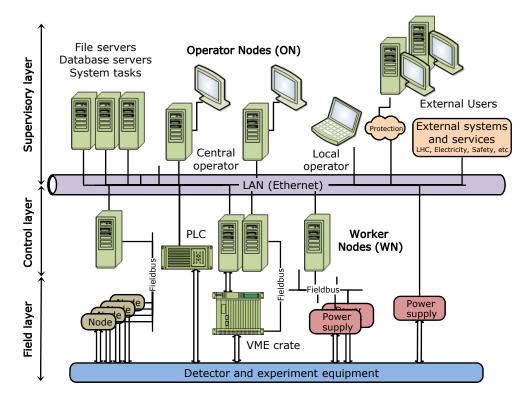

| 8.1         | Contro          | ols technologies in the LHC era              | . 129 | ) |

|             | 8.1.1           | Introduction to DCS – a brief story          | . 129 | ) |

| 8.2         | Front-          | end communications used in TRD DCS           | . 133 | } |

|             | 8.2.1           | Fieldbuses                                   | . 134 | ŀ |

|             | 8.2.2           | OLE for Process Control (OPC)                | . 136 | ; |

|             | 8.2.3           | Distributed Information Management (DIM)     | . 137 | 7 |

|             | 8.2.4           | Data Interchange Protocol (DIP)              | . 139 | ) |

| 8.3         | Back-e          | end systems used in TRD DCS                  | . 139 | ) |

|             | 8.3.1           | The PVSS system                              | . 139 | ) |

|             | 8.3.2           | JCOP Framework                               | . 142 | ) |

| 9 Inf       | rastruc         | cture requirements                           | 145   | ; |

| 9.1         | Low vo          | oltage infrastructure                        | . 145 | ) |

|             | 9.1.1           | LV distribution for FEE                      | . 145 | 5 |

|             | 9.1.2           | LV power for PCU, GTU and PT systems         | . 147 | 7 |

| 9.2         | High v          | oltage infrastructure                        | . 148 | 3 |

|             | 9.2.1           | High voltage distribution system             | . 148 | 3 |

| 9.3         | Locati          | on of the TRD infrastructure                 | . 150 | ) |

| 10 <b>1</b> | TRD D           | OCS development                              | 153   | } |

| 10.1        | . The T         | RD detector control system                   | . 153 | } |

| 10.2        | 2 TRD o         | control system design                        | . 154 | ŀ |

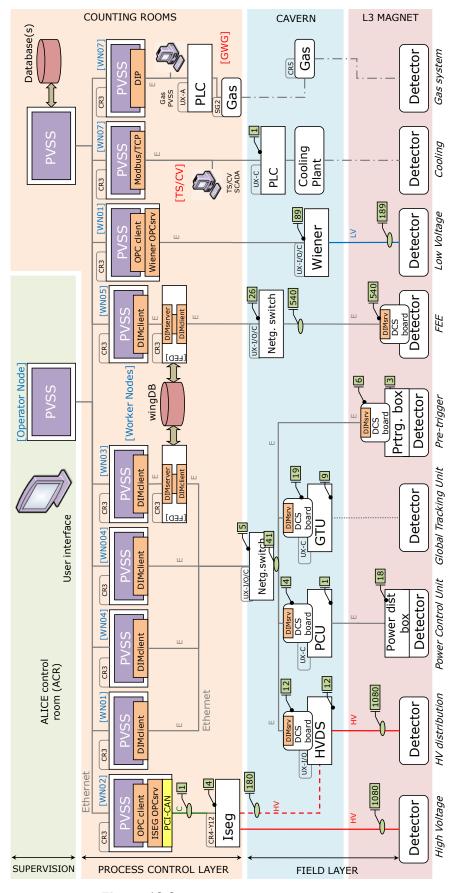

|             | 10.2.1          | Hardware architecture                        | . 154 | ŀ |

|             | 10.2.2          | Software architecture                        | . 158 | } |

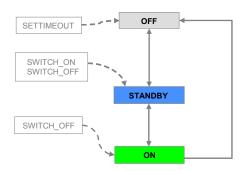

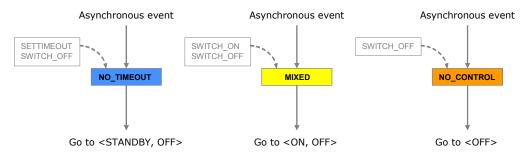

|             | 10.2.3          | The Finite State Machine concept             | . 159 | ) |

|             | 10.2.4          | State Management Interface (SMI++)           | . 162 | ) |

|             | 10.2.5          | JCOP FSM: result of PVSS - SMI++ integration | . 165 | ) |

|             | 10.2.6          | JCOP FSM object types (CUs, LUs and DUs)     | . 166 | ; |

|             | 10.2.7          | Partitioning                                 | . 167 | 7 |

| 10.3        | BTRD            | control system implementation                | . 168 | 3 |

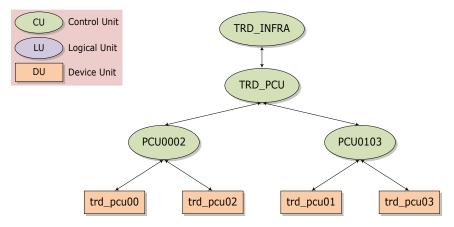

|         | 10.3.1 The control hierarchy                  | 168 |

|---------|-----------------------------------------------|-----|

|         | 10.3.2 Implementation strategy                | 168 |

|         | 10.3.3 The top level FSM node                 | 169 |

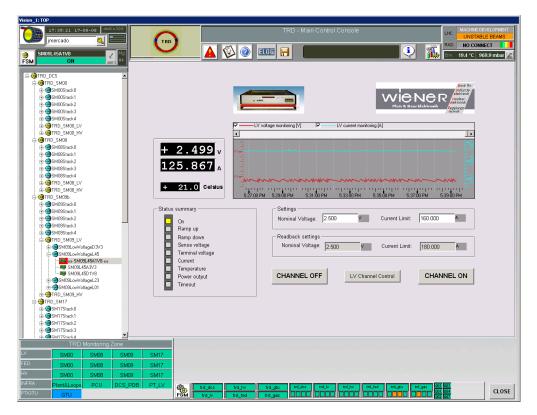

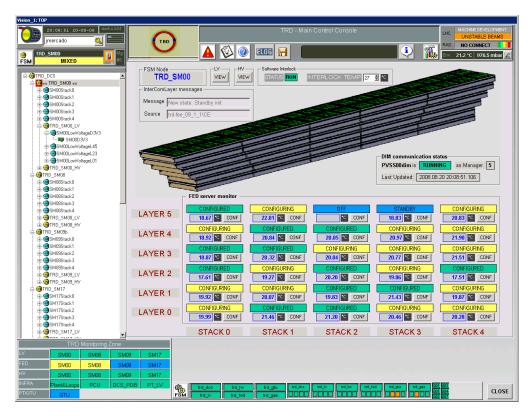

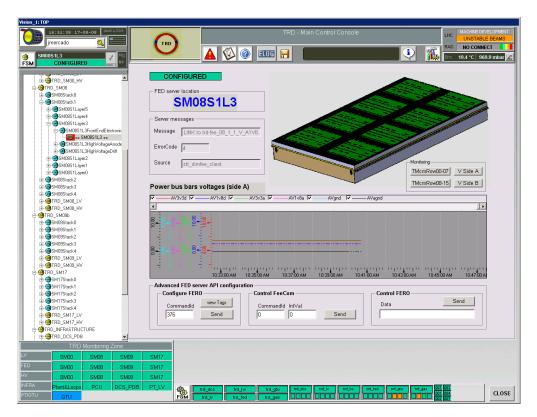

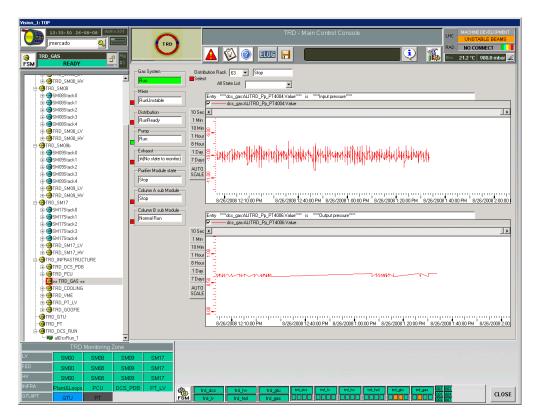

|         | 10.3.4 DCS user interface                     | 172 |

| 10.4    | Low voltage control system                    | 174 |

| 10.5    | Power control and distribution systems        | 180 |

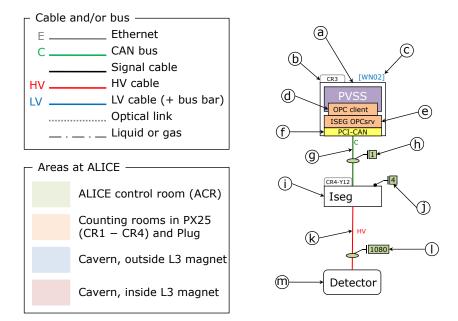

| 10.6    | High voltage control system                   | 187 |

|         | 10.6.1 High voltage distribution system       | 192 |

| 10.7    | Front-end electronics control system          | 193 |

|         | 10.7.1 FEE control software architecture      | 193 |

|         | 10.7.2 Linux on DCS boards                    | 195 |

|         | 10.7.3 FeeServer and Control Engine           | 197 |

|         | 10.7.4 InterComLayer                          | 199 |

|         | 10.7.5 FSM based control system               | 203 |

| 10.8    | Pre-trigger and GTU control systems           | 210 |

| 10.9    | Cooling and gas control systems               | 211 |

| 10.1    | 0 TRD control system integration              | 213 |

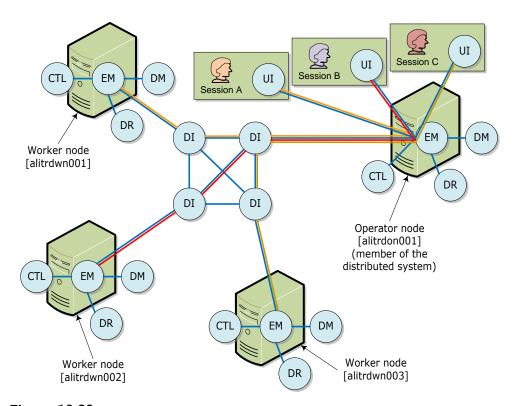

|         | 10.10.1 TRD DCS: a distributed system         | 213 |

|         | 10.10.2 Remote access                         | 214 |

|         | 10.10.3 Access control                        | 215 |

|         | 10.10.4 TRD DCS distributed system components | 216 |

|         | 10.10.5 TRD DCS archiving                     | 217 |

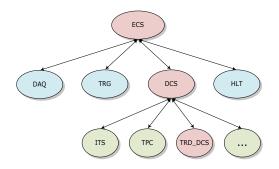

|         | 10.10.6 Integration with ALICE DCS and ECS    | 217 |

| 10.1    | 1 Conclusions                                 | 218 |

| Conclu  | usions                                        | 219 |

| Λ       |                                               |     |

| A sc    | CSN layout for all ROB types                  | 223 |

| List of | f Figures                                     | 227 |

| List of | f Tables                                      | 229 |

| Bibliog | graphy                                        | 231 |

\_\_\_\_

Part I

**Introductory Material**

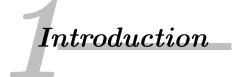

The question about the origin of our universe is as old as humankind. The Standard Model of cosmology describes the universe having its origin in the *Big-Bang*, a singularity which occurred about 13.7 billion years ago with high energy density and a temperature set by the Planck scale,  $T \approx M_{\text{Planck}} = 1.22 \times 10^{19}$  GeV. The universe has been expanding and thus cooling ever since. A schematic representation of the history of our universe is shown in Fig. 1.1.

**Figure 1.1:** Schematic representation of the history of the universe. Figure adapted from Ref. [1].

During this expansion, the universe underwent a series of phase transitions. Some 10  $\mu$ s after the Big Bang, it is believed that all matter visible today existed in a plasma state made of quarks and gluons, a *Quark-Gluon Plasma* (QGP). Around this time, a phase transition occurred and colored states of quarks and gluons were converted into color-singlet hadrons.

In the Standard Model of particle physics, quarks and gluons are the fundamental particles of strong interactions. *Quantum Chromodynamics* (QCD) is the theory of strong interactions. In QCD, the coupling between the colored quarks is mediated by the eight gluon bosons. Gluons themselves carry color. This implies that gluons interact among themselves. This property of QCD makes it radically different from other gauge theories describing e.g. electromagnetic or weak interactions [2]. In particular, the interaction of gluons gives rise to what is known as *asymptotic freedom*. Asymptotic freedom [3, 4] is a remarkable feature of QCD which implies that the interaction between quarks weakens as they get closer to one another.

Shortly after the idea of asymptotic freedom was introduced, it was realized that this has a fascinating consequence. Above a critical temperature and density, quarks and gluons are freed from their hadronic boundary forming a deconfined phase of matter [5, 6], i.e. a QGP.

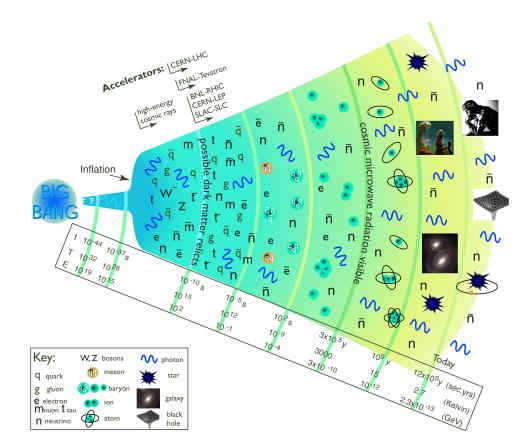

Due to the large coupling constant of QCD in the limit of low energy and large distances, it is not possible to perturbatively calculate physics quantities in QCD. The only known way to solve the equations of QCD in the region of strong coupling from first principles is to discretize Euclidean space-time on a lattice. This method is called *Lattice QCD* (LQCD). Solving QCD in lattice calculations, at vanishing or finite net-baryon density, predicts a cross-over transition from the deconfined thermalized partonic matter to hadronic matter at a critical temperature  $T_c \approx 150$  – 180 MeV [7]. A similar value has been derived in the 1960s by R. Hagedorn as the limiting temperature for hadrons when experimentally investigating hadronic matter [8].

The only way to create and study a QGP in the laboratory, is the collision of heavy nuclei at highest center-of-mass energies. A crucial question in these colli-

4

sions is to what extent matter is created, i.e. whether local equilibrium is achieved. If the system reaches equilibrium at least approximately, then temperature, pressure, energy, and entropy density can be defined. The analysis of particle production at the *Alternating Gradient Synchrotron* (AGS) at Brookhaven National Laboratory (BNL), *Super Proton Synchrotron* (SPS) at CERN, and the *Relativistic Heavy Ion Collider* (RHIC) at BNL has demonstrated that particle production can be understood by a statistical approach, in which all hadrons are produced from a thermally and chemically equilibrated state.

In Fig. 1.2 experimental data points for chemical freeze-out are compared with the phase boundary from lattice QCD. At least in the region of small chemical potential, temperatures extracted experimentally are close to the critical temperature from lattice QCD.

**Figure 1.2:** The phase diagram of nuclear matter. Lattice QCD calculations of the baryon chemical potential  $\mu_B$  and temperature T at the phase transition are shown. The triangle indicates the end point for the first order phase transition. Figure adapted from Ref. [9].

The Large Hadron Collider (LHC) at CERN near Geneva, Switzerland, has just started operation with protons circulating in the rings and will provide collisions of nuclei with masses up to that of lead at unprecedented high center-of-mass energies up to  $\sqrt{s_{NN}} = 5.5$  TeV. At these energies, the production of charm (bottom) is one (two) orders of magnitude larger [10] than at the presently highest available collision energies for heavy nuclei at RHIC. Thus, heavy quarks are copiously produced at LHC energies.

Heavy-quarks are excellent tools to study the properties of a QGP, among other interesting probes [11]. Due to their large masses ( $\gg \Lambda_{QCD}$ ), heavy-quarks are dominantly created in early stage perturbative QCD processes. The overall number of heavy quarks is conserved since their heavy mass is much smaller than the maximum temperature of the medium. Thus thermal production is negligible. Also, cross sections for heavy quark-antiquark annihilation are marginal [12].

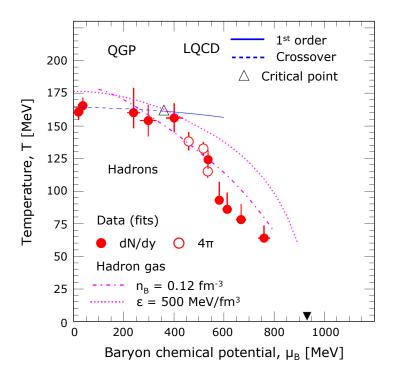

**Figure 1.3:** Quark masses in the QCD vacuum and the Higgs vacuum [13]. A large fraction of the light quark masses is due to the chiral symmetry breaking in the QCD vacuum while heavy quarks attain almost all their mass from coupling to the Higgs field.

As shown in Fig. 1.3, the large masses of heavy quarks are almost exclusively generated through their coupling to the Higgs field in the electro-weak sector, while masses of light quarks (u, d, s) are dominated by spontaneous breaking of chiral symmetry in QCD. This means that in a QGP, where chiral symmetry might be restored, light quarks are left with their bare current masses while heavy-quarks

remain heavy.

Bound systems of a heavy-quark anti-quark pairs, i.e. quarkonia, play a key role in research into the quark gluon plasma. In 1986, Satz and Matsui [14] suggested that the high density of gluons in a quark gluon plasma should destroy charmonium systems, in a process analogous to Debye screening of the electromagnetic field in a plasma through the presence of electric charges. Such a suppression was indeed observed by the NA50 collaboration [15] at SPS energies. However, absorption of charmonium in the cold nuclear medium also contributes to the observed suppression [16] and the interpretation of the SPS data remains inconclusive.

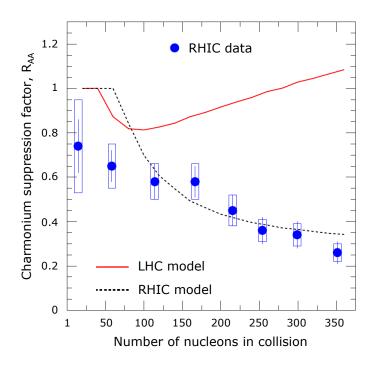

**Figure 1.4:** Statistical Model predictions for charmonium production relative to normalized p + p collisions for RHIC (dashed line) and LHC (solid line) energies. The data points are for top RHIC energies as measured by the PHENIX collaboration [17]. Figure adapted from Ref. [18].

At high collider energies, the large number of charm-quark pairs produced leads to a new production mechanism for charmonium, either through statistical hadronization at the phase boundary [19, 20] or coalescence of charm quarks in the plasma [21]. At low energy, the average number of charm-quark pairs produced in a collision is much lower than one, implying that charmonium is always formed from this particular pair. If charm quarks are copiously produced (in the order of some tens to a few hundred), charm quarks from different pairs can combine to form charmonium, see Fig. 1.4.

This mechanism works if heavy charm quarks can propagate over substantial distance to meet their counterpart. Under these conditions, charmonium production scales quadratically with the number of charm-quark pairs [18]. Thus enhancement rather than strong suppression is predicted for high collision energies. This would be a clear signature of the formation of a quark gluon plasma with deconfined charm quarks and thermalized light quarks.

The ALICE experiment at LHC will measure most of the heavy quark hadrons. Open charm hadrons are identified by their displaced decay vertex with high spatial resolution applying silicon vertex technology. The ALICE Transition Radiation Detector (TRD) measures  $J/\Psi$  production by identifying electrons and positrons from electromagnetic decays over a large momentum range [22, 23] and provides a fast trigger (< 6  $\mu$ s) for high transverse momentum ( $p_T$  > 3 GeV/c) charged particles.

The TRD consists of 540 read-out chambers arranged in 18 supermodules which are subdivided in 6 radial layers and 5 longitudinal stacks. About 1.2 million electronics read-out channels are digitized during the 2  $\mu$ s drift time by the frontend electronics designed in full custom for on-detector operation. The entire TRD is operated from a single workplace, i.e. the ALICE control room, via dedicated graphical user interfaces which are part of the TRD detector control system (DCS). Within this thesis, the TRD DCS design, implementation, and commissioning have been accomplished. The TRD DCS system is fully implemented as a detector oriented hierarchy of objects behaving as finite state machines. It controls and monitors over 65 thousand front-end electronics (FEE) chips, a few hundred low voltage and one thousand high voltage channels, and other sub-systems such as cooling and gas.

The TRD FEE components are mounted on dedicated read-out boards (ROBs). In total, the TRD incorporates over 4 thousand ROBs. Another part of this thesis describes the design and implementation of a test environment for large-scale production quality assurance of the full TRD ROB inventory. The hardware and

## **1** Introduction

software components are described in detail. Additionally, a series of performance studies were carried out earlier including radiation tolerance tests of the TRAP chip which is the core component of the TRD FEE.

This thesis has been written following up to some extent the chronological order in which the various projects were accomplished. It is organized as follows:

Chapter 2 gives a short introduction to the LHC, its layout, main machine and beam parameters, and its accelerator complex. In addition, the LHC experiments are briefly described. The ALICE experiment is explained in more detail in Chapter 3 including a short description of its various sub-detectors. In particular, the detector design and some basic facts of the TRD are summarized in Chapter 4.

Towards an understanding of the TRD operation and readout, the building blocks of the TRD FEE are described in Chapter 5. Radiation tolerance tests of the TRAP chip are reported in detail in Chapter 6, including a series of systematic measurements to characterize the analog pre-amplifier and shaper (PASA) chip, as well as *in situ* functional tests of the prototype PASA-TRAP assemblies in multichip modules (MCMs). The design and implementation of the test environment for quality assurance of the mass-produced ROBs is described in Chapter 7. Results accumulated over the past three years are summarized in Chapter 7 as well.

Chapter 8 gives a brief introduction to the control systems and technologies used in the LHC era. In particular, the tools employed in the implementation of the TRD DCS are summarized. A short description of the TRD DCS requirements in terms of equipment and infrastructure is given in Chapter 9. The TRD control system design and implementation is presented in Chapter 10. The description of the hardware and software architecture is followed by a detailed discussion on the DCS implementation for each TRD sub-system. The way the TRD DCS is distributed over several computers and the integration strategy with the global ALICE control systems are described as well.

*Introduction* This Chapter gives a brief introduction to the Large Hadron Collider (LHC), its layout, main machine and beam parameters, and its accelerator complex. In addition, a short description of the LHC experiments is given.

## 2.1 The accelerator

The idea of following CERN's *Large Electron-Positron Collider* (LEP) with a *Large Hadron Collider* (LHC), housed in the same tunnel, dates back at least to 1977, only two years after LEP itself was conceived. The importance of not compromising the energy of an eventual LHC was one of the arguments for insisting on a relatively long tunnel in the discussions that led to the approval of LEP in 1981. However, it was only in December 1994 that the CERN Council<sup>1</sup> approved the construction of a proton-proton collider working with two counter-rotating beams of protons accelerated to energies of 7 TeV: the LHC project. This venture will enable physicists from all over the world to explore the energy regime that resembles the universe  $10^{-12}$  seconds after the Big Bang when its temperature was still on the order of  $10^{16}$  Kelvin.

The main objective of the LHC is to explore the validity of the Standard Model of particle physics (see Chapter 1) at unprecedented collision energies and rates. The design performance envisages roughly 30 million proton-proton collisions per second, spaced by intervals of 25 ns, with center-of-mass collision energies of 14 TeV that are seven times larger than those of any previous accelerator, e.g.

<sup>&</sup>lt;sup>1</sup>The Council created in 1951 was a provisional body, that decided in 1953 to build a laboratory officially called "Organisation Européenne pour la Recherche Nucléaire" or "European Organization for Nuclear Research". However, the name of the Council stuck to the organization [24].

the most powerful accelerator currently in operation, the Tevatron at Fermilab (Batavia, Illinois), accelerates protons and anti-protons in a 6.3 km ring to energies of up to 1 TeV, hence the name.

#### 2.1.1 Luminosity

The collision energy and the event rate are the crucial parameters for a collider such as the LHC. A high collision rate is required in order to maximize the number of events seen by the detectors, meaning in turn high beam intensities. At present, the achievable production rates for anti protons are too low compared to those of the LHC design performance; therefore, two counter-rotating proton beams are used. As a consequence, two separate vacuum chambers are needed with magnetic fields of opposite polarity to deflect the counter-rotating beams in the same direction.

The product of the event cross-section,  $\sigma$ , and the machine luminosity, L, determines the number of collision events,  $\Delta N$ , per unit time interval,  $\Delta t$ , that are delivered to the LHC experiments,

$$\frac{\Delta N}{\Delta t} = L \cdot \sigma. \tag{2.1}$$

The event cross-section ( $\sigma$ ) is a measure of the probability of a reaction between two colliding particles. It has dimensions of area and can be visualized as the area presented by a "target" particle, which must be hit by a projectile particle for an interaction to occur. The luminosity describes the achieved beam intensity and is an important parameter when deriving cross-sections from events measured over a period of time. Thus, the number of events of a certain class is given by  $N = A \cdot \sigma \int L dt$ , where A is the experiment acceptance (detection efficiency),  $\sigma$ the cross-section, and  $\int L dt$  the luminosity integrated over time. The luminosity has dimensions of (area × time)<sup>-1</sup>.

The luminosity is determined entirely by the accelerator and beam parameters. In the LHC case, i.e. for beams colliding in bunches either head-on or at a small angle, the luminosity is given by

$$L = \frac{f_{\rm rev} n_{\rm b} N_{\rm p}^2}{\sigma_{\rm x} \sigma_{\rm y}} F(\Phi, \sigma_{\rm x,y}, \sigma_{\rm s}), \qquad (2.2)$$

where  $f_{rev}$  is the revolution frequency;  $n_b$ , the number of particle packages per ring ('bunches');  $N_p$ , the number of protons within each bunch; and  $\sigma_x$  and  $\sigma_y$ , the transverse root mean squared (r.m.s.) beam sizes at the interaction points. F is a geometric reduction factor that depends on the crossing angle of the two beams ( $\Phi$ ), the transverse r.m.s. beam size ( $\sigma_{x,y}$ ) and the r.m.s. bunch length ( $\sigma_s$ ). If the particle distribution in the bunches is assumed to be Gaussian, the luminosity becomes

$$L = \frac{1}{4\pi} \left( \frac{f_{\rm rev} n_{\rm b} N_{\rm p}^2}{\sigma_x \sigma_y} \right).$$

(2.3)

The design luminosity of the LHC has been set to  $L = 10^{34} \text{ cm}^{-2}\text{s}^{-1}$  in order to provide more than one hadronic event per beam crossing. This luminosity corresponds to 2,808 bunches, each containing  $1.15 \times 10^{11}$  protons, a transverse r.m.s. beam size of 16  $\mu$ m, an r.m.s. bunch length of 7.5 cm and a total crossing angle of 320  $\mu$ rad at the interaction points [25].

#### **Box 2.1:** The LHC as a lead ion collider

For heavy ion collisions, the luminosity will be  $L = 10^{27} \text{ cm}^{-2}\text{s}^{-1}$  at a center-ofmass energy of 1,148 TeV. Each ring of the LHC will contain in this case 592 bunches, each with  $7 \times 10^7$  lead ions (beam energy of 2.76 TeV per nucleon). The transverse beam sizes will be similar to those of the proton beams.

## 2.1.2 The LHC layout

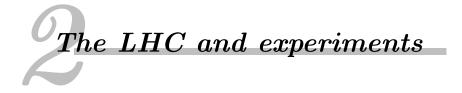

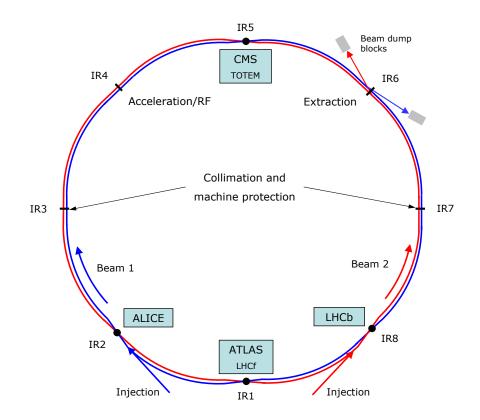

The LHC consists of 8 sectors (shown schematically in Fig. 2.1). Each octant has bending dipole magnets and focusing quadrupole magnets which keep the particles centered on the design orbit. In addition, radio-frequency (RF) cavities in the IR4 straight section focus the particles into longitudinal bunches and accelerates them. In order to keep the 7-TeV proton beams on their 27-km closed orbits, bending fields of 8.4 T are required. To achieve such high magnetic fields and at the same time avoid excessive resistive losses, the dipole magnets have to be superconducting. The LHC consists of a total of 1,232 15-m-long dipole magnets (Fig. 2.2, left) that are cooled down to 1.9 K using superfluid helium.

**Figure 2.1:** Two proton beams circulate in opposite directions around the ring crossing at four designated interaction regions (IRs), where the various LHC experiments are located.

**Figure 2.2:** Dipole magnets installed in the LHC tunnel (left). Internal structure of a superconducting dipole magnet (right). Images reproduced from the public CERN Document Server (CDS) area.

A novel two-in-one magnet construction allows both beam pipes to be housed in a single yoke and cryostat (Fig. 2.2, right), significantly saving space and costs. A total helium inventory of 96,000 kg is available to cool down the LHC total cold mass of 37,000 tons. This makes the LHC the world's biggest cryogenic system. Some selected machine and beam parameters for both, proton-proton and heavyion collisions, are listed in Table 2.1.

| Parameter                             | Proton-Proton                      | Pb-Pb                           |

|---------------------------------------|------------------------------------|---------------------------------|

| Energy per nucleon                    | 7 TeV                              | 2.76 TeV                        |

| Injection energy per nucleon          | 450 GeV                            | 177.4 GeV                       |

| Dipole field                          | 8.4 T                              | 8.33 T                          |

| Design luminosity                     | $10^{34} { m cm}^{-2} { m s}^{-1}$ | $10^{27} {\rm ~cm^{-2} s^{-1}}$ |

| Protons/ions per bunch                | $1.15 	imes 10^{11}$               | $7 \times 10^7$                 |

| Number of bunches                     | 2,808                              | 592                             |

| Bunch length (r.m.s.)                 | 7.5 cm                             | 7.94 cm                         |

| Total cross-section (nucleon-nucleon) | 100 mb                             | 514,000 mb                      |

| Stored beam energy                    | 362 MJ                             | 3.81 MJ                         |

| Energy loss per turn per nucleon      | 6.7 keV                            | 1.12 MeV                        |

| Synchrotron radiation power per ring  | 3.6 kW                             | 83.9 W                          |

Table 2.1: Selected machine and beam parameters. Compiled from Ref. [26].

## 2.1.3 The accelerator complex

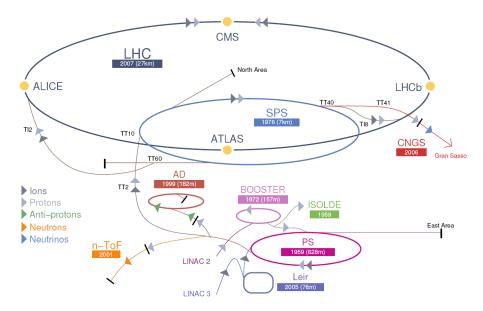

The proton beam of the LHC starts off in a 50-MeV linear accelerator, LINAC2 (Fig. 2.3). It is then passed to a multi-ring booster synchrotron for acceleration to 1.4 GeV, and then to the 628-m-circumference *Proton Synchrotron* (PS) machine to reach 26 GeV. During acceleration in the PS, the bunch pattern and spacing needed for the LHC are generated by splitting the low-energy bunches. A final transfer is made to the 7-km *Super Proton Synchrotron* (SPS) machine, where the beam is further accelerated to 450 GeV. At this point, the beam is ready for injection into the LHC. The cycle takes about 20 s and creates a train of bunches with a total kinetic energy of more than 2 MJ. This is approximately 8% of the beam needed to fill an LHC ring completely, hence the whole cycle is repeated 12 times per ring.

$^{208}\text{Pb}^{+27}$  ions are accelerated in the linear accelerator LINAC3 to 4.2 MeV/nucleon. After that, they are stripped by a carbon foil and the charge state  $\text{Pb}^{+54}$  is selected in a filter line. These selected ions are further accelerated in the *Low*

*Energy Ion Ring* (LEIR) to an energy of 72 MeV/nucleon. The ions are then transferred to the PS where they are further accelerated to 5.9 GeV/nucleon and sent to the SPS. In between, they pass another foil which fully strips the Pb ions to  $Pb^{+82}$ . The SPS accelerates the stripped ions to 177 GeV/nucleon, before injecting them into the LHC where they reach the maximal energy of 2.76 TeV/nucleon.

**Figure 2.3:** The CERN accelerator complex. Figure adapted from the public CERN Document Server (CDS) area. The figure is not to scale.

The particle beams either proton or lead ions are injected in the LHC clockwise and anticlockwise. Both beams collide at the four interaction points mentioned before.

## 2.2 Experiments at the LHC

The LHC features four major experiments (Fig. 2.1): two high-luminosity generalpurpose experiments (ATLAS [27] and CMS [28]); a *b*-meson experiment (LHCb [29]); and one dedicated heavy-ion physics experiment (ALICE [30, 31, 10]). In addition, there are two supplementary experiments at low scattering angles, LHCf [32] and TOTEM [33], which are near ATLAS and CMS, respectively.

#### 2.2.1 ATLAS

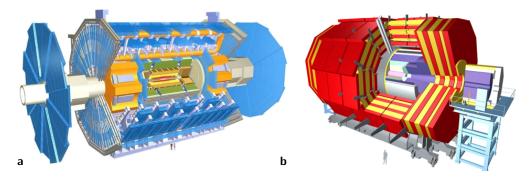

ATLAS (A Toroidal LHC ApparatuS) is a large-scale general purpose-detector with the aim to exploit the full physics potential of the LHC. The main goal is the search for the Higgs boson and the detector is designed to be sensitive to the largest possible Higgs masses. The search for physics beyond the Standard Model (such as supersymmetry or extra dimensions), and measurements of the *W* boson and top quark masses will be covered as well.

ATLAS uses two different magnetic field systems, an inner superconducting solenoid around the inner detector cavity with a 2 T field and an outer superconducting air cored toroid magnet system (Fig. 2.4). The inner detector comprises a large silicon system (pixels and strips) and a gas-based transition radiation straw tracker. The calorimeters use liquid-argon technology for the electromagnetic measurements and also for hadronic measurements in the end-caps of the detector. An iron/scintillator system provides hadronic calorimetry in the central part of the detector. The muon system is based on gas detectors and has precise tracking chambers and trigger chambers for a robust and efficient muon trigger.

**Figure 2.4:** Geometry and basic layout of the two LHC general-purpose experiments. The ATLAS detector (**a**) has a radius of 13 m and is 46 m long, with a weight of 7,000 tons. CMS (**b**) is more compact than ATLAS, and has a radius of 7.5 m and length of 24 m, but weighs 12,000 tons. Figures adapted from Refs. [27] and [28].

### 2.2.2 CMS

The physics program of CMS (Compact Muon Solenoid) features investigations of electroweak symmetry breaking (through the possible observation of one or more Higgs bosons), searches for phenomena beyond the Standard Model, and detailed studies of Standard Model physics and CP violation.

CMS, in contrary to ATLAS, uses only one magnetic system. A single superconducting solenoid generates a magnetic field of 4 T and houses a full siliconbased inner tracking system (pixels and strips), a fully active, scintillating crystal electromagnetic calorimeter, and a compact scintillator/brass hadronic calorimeter (Fig. 2.4). Outside the solenoid, there is an iron-core muon spectrometer sitting in the return field of the powerful solenoid, with tracking and trigger chambers.

## 2.2.3 LHCb

The LHCb detector has a silicon vertex detector around the interaction region; then a tracking system consisting of silicon micro-strip detectors and a straw tracker, and it includes a dipole magnet. It also has two ring-imaging Čerenkov detectors, positioned in front of and after the tracking system, for charged-hadron identification; a calorimeter system and finally a muon system.

LHCb is a single-arm spectrometer with a forward angular coverage from approximately 15 mrad to 300 (250) mrad in the bending (non-bending) plane. The choice of the detector geometry (Fig. 2.5) is motivated by the fact that at high energies both the *b*- and  $b\bar{b}$ -hadrons are predominantly produced in the same forward cone.

**Figure 2.5:** Schematic layout of the LHCb detector. The LHCb detector is 21 m long, 10 m high, 13 m wide, and weighs 5,600 tons. Figure reproduced from the the public CERN Document Server (CDS) area.

### 2.2.4 ALICE

ALICE is the dedicated heavy-ion experiment at the LHC. The ALICE detector is designed to identify and characterize the Quark-Gluon Plasma at LHC energies. The ALICE experiment is presented in Chapter 3.

## 2.2.5 TOTEM

The TOTEM (TOTal Elastic and diffractive cross section Measurement) experiment studies forward particles to focus on physics that is not accessible to the general-purpose experiments. Among a range of studies, it will measure, in effect, the size of the proton and also monitor accurately the LHC luminosity.

TOTEM detects particles produced very close to the LHC beams. It includes detectors housed in specially designed vacuum chambers called *Roman pots*, which are connected to the beam pipes in the LHC. Eight Roman pots are placed in pairs at four locations near the collision point of the CMS experiment.

## 2.2.6 LHCf

The main purpose of the LHCf (Large Hadron Collider forward) experiment is to interpret and calibrate data from large-scale cosmic-ray experiments, e.g. the Pierre Auger observatory, by studying how collisions inside the LHC cause cascades of particles similar to those that cosmic rays create when striking the Earth's atmosphere.

*Introduction* ALICE is the experiment at the LHC optimized for the study of heavy-ion collisions. The ALICE experiment and its various sub-detectors are briefly described in this Chapter. A short introduction to the trigger and data acquisition in ALICE is given as well.

## 3.1 Purpose and physics motivation

An important part of the LHC project is the study of strongly interacting matter at extreme densities (substantially larger than for ground state nuclei) and high temperatures, where the formation of the phase of matter known as Quark-Gluon Plasma (QGP) is expected. A Large Ion Collider Experiment (ALICE) is the dedicated experiment for these studies.

The LHC will run with heavy ions about 10% of its running time, which translates into 10<sup>6</sup> seconds of running time per year. The event rate of Pb-Pb collisions, given the maximum luminosity of  $L = 10^{27}$  cm<sup>-2</sup>s<sup>-1</sup> and an inelastic cross-section of 8 b, will be 8,000 minimum-bias collisions per second. Only some 5% of these events are typically considered as to correspond to the most central collisions. This low interaction rate allows the use of slow but high-granularity detectors, like the time projection chamber (TPC) and the silicon drift detectors. The ALICE rapidity acceptance has been chosen to be large enough to allow the study of particle ratios,  $p_T$  spectra, particle decays, and some variables on an event-by-event basis. Detecting the decay products of low-momentum particles ( $p_T < m$  for m > 1 - 2GeV/ $c^2$ ) requires coverage of about 2 units of rapidity and an adequate coverage in azimuth ( $\Delta \varphi = 2\pi$ ). ALICE has been specifically designed to maximize momentum coverage, from  $\approx 100 \text{ MeV}/c$ , the lowest values relevant for thermodynamical studies, to  $\approx 100 \text{ GeV}/c$ , the transverse momentum of the leading particles of jets with transverse energy well over 100 GeV. The measurement of numerous precision points over a long measured track length in a moderate magnetic field and with minimal material allows to satisfy both requirements.

Although ALICE is dedicated to heavy-ion physics, it will also fully participate in the proton-proton physics program, e.g. for reference measurements for heavy-ion collisions and *pp* physics itself.

Box 3.1: ALICE particle identification (PID) potential

ALICE employs essentially all known PID techniques: specific ionization energy loss, time-of-flight, transition and Čerenkov radiation, electromagnetic calorimetry, muon filters, and topological decay reconstruction.

## 3.2 The ALICE detector

Dominating the ALICE cavern is the huge L3 magnet — the world's largest volume conventional magnet. It is inherited from the former LEP experiment L3. It can provide a solenoidal field, i.e. parallel to the beam axis, of up to 0.5 T for momentum dispersion of charged particles.

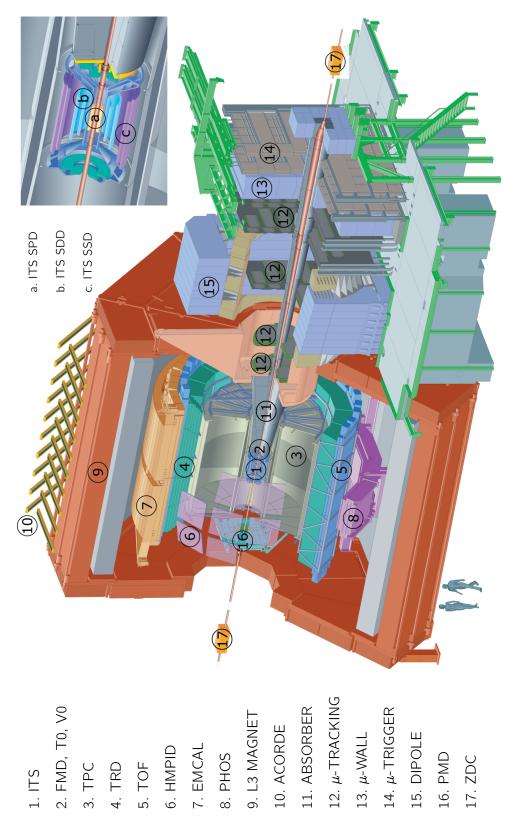

ALICE is composed of various sub-detector systems which are arranged in cylindrical shells around the interaction point embedded in the L3 magnet and a forward muon spectrometer outside (Fig. 3.1). Without being exhaustive, the ALICE detector can be sub-divided into three sections: (i) the central barrel detectors, (ii) the forward detectors, and (iii) the muon spectrometer. A cosmic ray detector is located on top of the L3 magnet.

#### 3.2.1 Central barrel detectors

The main purpose of the barrel detectors is to measure the momentum and identity of particles produced in the region  $|\eta| \le 0.9$  over the full azimuth.

**Figure 3.1:** ALICE schematic layout. Its overall dimensions are  $16 \times 26$  m with a total weight of approximately 10,000 t.

#### Box 3.2: The global ALICE coordinate axis system

In ALICE a right-handed orthogonal Cartesian coordinate system is adopted with the point of origin at the beam interaction point. The *x*-axis is perpendicular to the beam direction and pointing to the accelerator center; *y*-axis is perpendicular to the *x*-axis and to the beam direction, pointing upward; *z*-axis is parallel to the beam direction. Hence the positive *z*-axis is pointing in the direction opposite to the muon spectrometer.

**ITS** The Inner Tracking System (ITS) is a system of six barrel layers of silicon detectors providing high-resolution spatial tracking and precise vertex information. With its inner radius of 4 cm, it is the detector system closest to the interaction point. It consists of three sub-detectors, starting from the center and going outwards: the silicon pixel detector (SPD), the silicon drift detector (SDD), and the silicon strip detector (SSD) [34]. Each of these three sub-detectors has two layers (Fig. 3.2).

The SPD active elements are small pixels on the face of a silicon sensor. It has a resolution of 12  $\mu$ m in the  $r\varphi$  plane and 70  $\mu$ m in the z direction. With its expected occupancy of 0.4% to 1.5%, it is a formidable charged particle multiplicity detector in the region  $|\eta| < 2.1$ . Furthermore, by combining all possible hits in the SPD one can get a rough estimate of the position of the primary interaction.

The other two layers of the ITS, the SDD and SSD, have slightly less granularity than the SPD. They provide further tracking points and charged particle multiplicity measurements. Due to its fine granularity and proximity to the interaction point, the ITS can resolve decays of short-lived particles (such as As and  $\equiv$ s) and determine the point of decay.

The ITS tracking information is used to restrict the global tracking of particles in the central barrel detectors: tracks that do not seem to originate relatively close to the interaction point can be discarded as background tracks from cosmic rays, scattering in materials, or other such sources.

**TPC** The Time Projection Chamber (TPC) is the main tracking device of the ALICE central barrel [35]. It provides charged-particle momentum measurements,

particle identification and vertex determination together with the ITS, TRD and TOF. Being a gaseous detector, particles traversing its 80 m<sup>3</sup> volume ionize the gas and electrons drift towards the readout planes on either end-cap (Fig. 3.2).

The time it takes for the electrons to drift from the high voltage central electrode membrane to the readout chambers of the TPC is roughly 88  $\mu$ s which sets the trigger scale of ALICE, i.e. right after a collision has occurred, during this time no other event is read out, otherwise, the current event would be corrupted. Unlike ATLAS and CMS where each read out event can be tagged with a time stamp, the ALICE TPC does not resolve particles from multiple interactions. The maximum trigger rate of ALICE is therefore around 10 kHz. Particle identification in the TPC is done by using the energy loss of particles in the gas.

**Figure 3.2:** Schematic layouts of the ITS (left) and the TPC (right). The TPC has an outer radius of about 2.5 m and an overall length along the beam direction of 5.0 m. The ITS has an outer radius of about 43 cm and a maximum length of 48.9 cm. Figures generated using the ALICE analysis framework ALIROOT (not to scale).

**TRD** Located outside the TPC barrel, the Transition Radiation Detector (TRD) identifies electrons with momenta above 1 GeV/c and provides triggering capabil-

ity for high transverse momentum ( $p_T > 3 \text{ GeV}/c$ ) charged particles. The TRD is presented in Chapter 4.

**TOF** The Time Of Flight (TOF) detector is placed outside the TRD and provides a measurement of the time it takes a particle to travel from the interaction point, through the magnetic field, to the outer rim of the barrel.

TOF is built of Multigap Resistive Plate Chambers (MRPC). In such a detector, the electric field is high and uniform over the whole sensitive gaseous volume. Any ionization produced by a through-going charged particle immediately starts a gas avalanche process. The signal from the avalanche is then detected at the anode of the detector [36]. This design gives a timing resolution of about 120 ps.

**HMPID** The High Momentum Particle Identification Detector (HMPID) is placed at a distance of about 4.5 m from the beam axis. Its purpose is to identify the particle type of very high momentum particles. The  $\pi/K$  separation goes up to 3 GeV/*c* while K/p separation up to 5 GeV/*c*.

The HMPID exploits the fact that charged particles emit Čerenkov radiation when the velocity of the particle is larger than the speed of light in the medium traversed, v > c/n (*n* is the index of refraction of the medium). The HMPID consists of seven modules composed of a liquid radiator (C<sub>6</sub>F<sub>14</sub>) and a Multi-Wire Proportional Chamber (MWPC) behind detecting the Čerenkov light produced in the radiator through pads covered by CsI, a photosensitive material. The MWPC also detects the particle which produced the Čerenkov light.

**EMCAL** The purpose of the Electro-Magnetic Calorimeter (EMCAL) is to measure the total energy of particles within a large  $\varphi$  segment and roughly the same  $\eta$  range as the TPC and TRD. The EMCAL provides  $p_T$  measurements in the region from 100 MeV/*c* to 100 GeV/*c* [37] making it an excellent detector for jet studies. The readout of the EMCAL is fast enough to participate in the L1 trigger decision, and therefore provides ALICE with a jet-trigger.

The calorimeter is made of Pb-scintillator rods placed so that they point to-

wards the nominal interaction point. Light created by traversing charged particles is collected in fibers and sent to a photo-chip for collection.

**PHOS** The Photon Spectrometer (PHOS) is an electromagnetic calorimeter of lead-tungsten crystals. It will measure photons,  $\pi^0$  (via  $\pi^0 \rightarrow \gamma + \gamma$ ), and  $\eta$ mesons up to a transverse momentum of 10 GeV/c. These measurements can be used to study jet physics, to perform direct measurements of initial temperature, and to look for signatures of chiral symmetry restoration.

#### 3.2.2 Forward detectors

A number of smaller detector systems [30] placed at small angles from the beam line serve to provide global event characteristics, like triggering, primary vertex, and multiplicity.

**ZDC** Distance to the interaction point is measured by four small and dense calorimeters, the Zero Degree Calorimeter (ZDC) detectors.

**PMD** The Photon Multiplicity Detector (PMD) determines the event reaction plane and elliptic flow as well as the ratio of photons to charged particles and the transverse energy of neutral particles.

**FMD** The Forward Multiplicity Detector (FMD) measures the number of charged particles at forward (small) angles relative to the beam line in fine  $\eta$  and  $\varphi$  bins.

**T0** The T0 detector is a high-resolution timing detector which consists of Čerenkov radiators glued onto photo-multiplier tubes. The time resolution of T0 is of the order of 10 ps. A coincidence between the two sides T0-A and T0-C will serve as a L0 trigger and early wake-up signal to other detectors such as TRD.

**V0** In p + p collisions where the density of charged particles is much lower than in A + A, T0 does not have large enough acceptance to provide a L0 trigger at high efficiency. The V0 detector was therefore designed to have a larger acceptance to provide the first trigger in pp. V0 is also used to discriminate against beam-gas interactions by requiring the coincidence of the scintillators on both sides of the interaction region.

#### 3.2.3 Muon spectrometer

In addition to the central barrel detectors for tracking and particle identification, and the forward detectors for global event characterization, ALICE features a muon spectrometer [38] whose main purpose is to measure dileptons (mainly  $\mu^+\mu^-$ ), hence the complete spectrum of heavy quark mesons (e.g.  $J/\Psi$ ,  $\Psi'$ , etc.).

The spectrometer consists of several parts. Closest to the interaction point is the cone-shaped front absorber which serves as a filter such that the most likely particles to be observed in the rest of the spectrometer are  $\mu^+\mu^-$ . Behind the absorber nose are two tracking stations, one of them placed inside the L3 magnet while the second one is flushed with the edge of the solenoidal field in order to allow the spectrometer to precisely determine where the particles left the field. Dominating the spectrometer is the large dipole magnet, which bends the trajectory of charged particles in the *yz* plane. A third tracking station is located in the middle of the dipole to allow precise measurements of the angle of deflection. Two more stations sit further back, on either side of another muon filter (an iron wall about 1 m thick).

All tracking stations in the muon spectrometer are cathode plane detectors. Finally, behind the last tracking station are the trigger chambers for measuring the time-of-flight of the particles, hence allowing for identification. These chambers are resistive plate chambers.

**ACORDE** ALICE Cosmic Ray Detector (ACORDE) consists of an array of plastic scintillator counters placed on the three upper faces of the L3 magnet. It serves as a cosmic ray trigger, and together with other ALICE sub-detectors, provides precise information on cosmic rays with primary energies around  $10^{15}-10^{17}$  eV.

## 3.3 Trigger and data acquisition

The ALICE trigger system is based on the concept of hierarchical trigger levels with data reduction in each level. The trigger issued at the earliest stage of data taking is called Level-0 (L0) trigger. After this L1 and L2 triggers follow if the events are accepted in each level. In addition, to these ALICE global trigger levels, the TRD receives a *pre-trigger* which arrives even earlier than L0 trigger. A brief description of these trigger levels is given in the following.

#### 3.3.1 Pre-trigger system

The pre-trigger system provides a fast wake-up signal to the TRD allowing its digital electronics to be in a low-power mode most of the time. The wake-up signal consists of direct inputs from the T0, V0, TOF, and eventually ACORDE detectors while a copy of these inputs is sent in parallel to the central ALICE trigger. The pre-trigger system also allows for very low latency (6  $\mu$ s) data processing in the TRD for L1 trigger contributions.

#### 3.3.2 L0, L1, L2 trigger levels

The L0 and L1 triggers gate the fast detectors, while only after a L2 decision level has been reached, the "slow" TPC is read out. The L0 signal reaches the detectors at 1.2  $\mu$ s. This small time budget allows only some detectors, e.g TOF, V0, T0, and TRD-pretrigger, to contribute to the L0 decision which is relevant for detectors like HMPID and TRD. Various detectors, e.g. PHOS, TOF, TRD, etc., contribute to the L1 decision [39]. These inputs are collected by the ALICE *Central Trigger Processor* (CTP) which in turn send the L1 trigger signal to all detectors at 6.5  $\mu$ s after the collision. The L2 includes a past-future protection scheme. The high multiplicities expected in the ALICE environment make events containing more than one central collision non-reconstructable. The L2 waits until the end of the past-future protection interval (88  $\mu$ s — equaling the TPC drift time) in order to verify that the event can be taken.

The trigger information is distributed from the CTP to dedicated *Timing*, *Trigger and Control receiver* (TTCrx) *Application Specific Integrated Circuits* (ASIC) which are implemented in each sub-detector readout electronics and synchronized with the LHC machine clock cycle (40 MHz) via optical fiber [40]. The clock, trigger, asynchronous control commands, and synchronization information arrive at the TTCrx chip as encoded signal. TTCrx decodes the signal, and forwards it to lower level components in the ALICE sub-detectors front-end electronics. L0 and L1 triggers are sent as trigger information synchronous to the LHC clock at fixed time with respect to the bunch crossing time. The L2 trigger information is sent asynchronously as asynchronous control commands.

#### 3.3.3 High-Level Trigger

The HLT system provides high level decision for further event reduction based on online and real-time event reconstruction using ALICE offline software. The TPC, ITS, and muon spectrometer are tracking detectors and need a longer time span after the collision to deliver their data. This is compensated by the detailed information they provide. The HLT profits from this information (e.g. up to 76 MB/event at rates of up to 200 Hz for the TPC) in order to reduce the data rate as far as possible. After data reduction in the HLT, the data are returned to the ALICE data acquisition chain and recorded onto an archival-quality medium for subsequent off-line analysis. The HLT accomplishes data reduction in many ways as detailed in Ref. [40].

#### 3.3.4 Data acquisition

The ALICE data acquisition (DAQ) system reads out data from the front-end electronics of each sub-detector in parallel over hundreds of optical detector data links (DDL), performs event building, and archives it to permanent storage for later analysis. A bandwidth of 1.25 GB/s to mass storage is consistent with constraints imposed by technology, cost, storage capacity, and computing power needed to reconstruct and analyze the data. It includes the data flow from the sub-detector electronics up to the DAQ computing fabric and to the HLT farm, the transfer of information from the HLT to the DAQ fabric, and the data archiving in the CERN computing center [40]. The DAQ system also includes software packages performing the following functions: data quality monitoring, system performance monitoring, and overall control of the system.

The ALICE TRD

*Introduction* This Chapter gives a short description of the ALICE Transition Radiation Detector (TRD). The detector design, readout, and basic infrastructure are briefly summarized.

# 4.1 Transition radiation

Transition radiation (TR) photons are emitted when a particle moves across the interface of two materials with different dielectric constants. For ultra-relativistic particles, this radiation appears in the X-ray region. The energy radiated when a charged particle crosses the boundary between two media with plasma frequencies  $\omega_{p_1}$  and  $\omega_{p_2}$  is

$$E = \frac{\alpha \hbar}{3} \frac{(\omega_{\rho_1} - \omega_{\rho_2})^2}{\omega_{\rho_1} + \omega_{\rho_2}} \gamma, \qquad (4.1)$$

where

$$\omega_{p_{1,2}} = \sqrt{\frac{4\pi\alpha n_{e_{1,2}}}{m_e}},\tag{4.2}$$

$\gamma$  is the Lorentz factor,  $\alpha$  is the the fine structure constant ( $\alpha = 1/137$ ),  $n_e$  is the electron density in the medium, and  $m_e$  is the electron rest mass [41]. Eq. (4.2) can be written in terms of the Bohr radius ( $a_{\infty} = r_e \alpha^{-2}$ ) as

$$\hbar\omega_{p} = \frac{m_{e}c^{2}}{\alpha}\sqrt{4\pi n_{e}r_{e}^{3}} = \sqrt{4\pi n_{e}a_{\infty}^{3}} \times 27.2 \text{ eV}.$$

(4.3)

Here,  $r_e$  is the classical electron radius. For styrene, polypropylene and similar materials,  $\sqrt{4\pi n_e a_{\infty}^3} \approx 0.8$  so that  $\hbar \omega_p \approx 20$  eV [42]. This radiation hence offers the possibility of "particle identification" at highly relativistic energies, where

Čerenkov radiation or ionization measurements no longer provide useful particle discrimination. Electron discrimination is possible for momenta from about 1 GeV/*c* to 100 GeV/*c*. The angular distribution of transition radiation is peaked forward with a sharp maximum at  $\theta = 1/\gamma$ , hence collimated along the direction of the radiating particle. From Eq. (4.1) it can be observed that the energy radiated by a single foil depends on the squared difference of the plasma frequencies of the two materials; if the difference is large (e.g.  $\hbar \omega_{air} \approx 0.7$  eV and  $\hbar \omega_{polypropylene} \approx 21$  eV), the relation becomes

$$E \approx \frac{1}{3} \alpha \gamma \hbar \omega_p. \tag{4.4}$$

The average number of radiated photons is of order  $\alpha\gamma$ , i.e.

$$\langle N \rangle \approx \alpha \gamma \frac{\hbar \omega_p}{\hbar \langle \omega \rangle}.$$

(4.5)

The emission spectrum typically peaks between 1 keV and 30 keV (soft X-rays).

**Box 4.1:** Basic TR detection in the ALICE TRD In order to intensify the TR-photon flux, the ALICE TRD uses periodic arrangements of sandwich radiators interleaved by X-ray detectors, namely, *Multi-Wire Proportional Chambers* (MWPC) filled with a high-Z gas mixture (Xe/CO<sub>2</sub>) for efficient X-ray absorption.

# 4.2 Detector requirements and design

#### 4.2.1 Physics requirements

The main purpose of the ALICE TRD is to identify electrons in the central barrel with momenta above 1 GeV/*c* where the TPC is no longer efficient in pion rejection using specific energy loss (dE/dx) measurement. Furthermore the TRD provides fast (6  $\mu$ s) triggering capability for high transverse momentum ( $p_T > 3 \text{ GeV}/c$ ) charged particles.

The purpose of this Section is to describe some basic facts about the ALICE TRD. A comprehensive summary of the design, performance and construction can be found in the technical design report (TDR) [43]. Some newly developed devices

and general updates since the submission of the TDR are given in this Section as well.

#### 4.2.2 Detector design

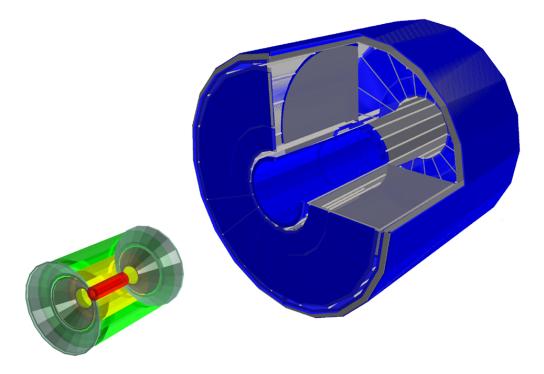

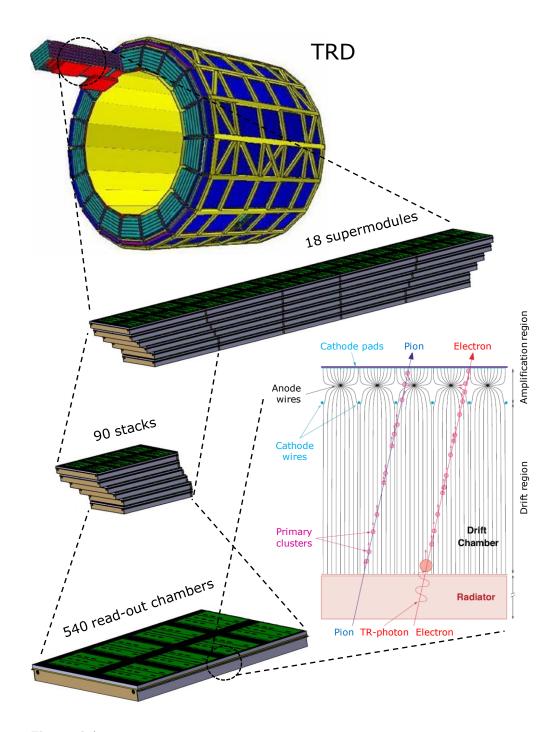

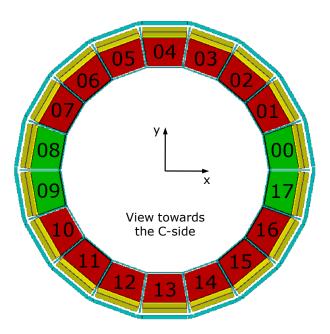

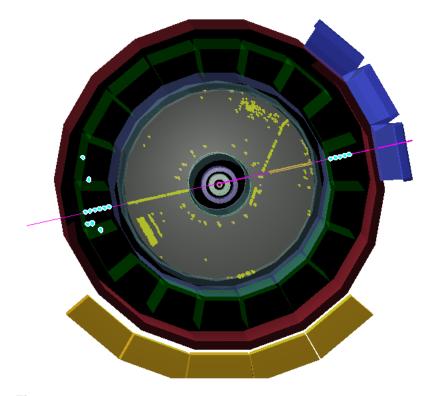

The TRD has a cylindrical geometry, and is located outside the TPC barrel forming a ring with an inner radius of 2.9 m and an outer radius of 3.68 m. Its axial length is about 7 m. It consists of 18 trapezoidal elements (supermodules) with a total of 540 individual gas detector modules arranged in 6 radial layers which are subdivided into 5 longitudinal sections (stacks) as illustrated in Fig. 4.1.

Each detector consists of a sandwich radiator, a combination of polypropylene fiber mats embedded in Rohacell foam sheets of 48 mm overall thickness; it is followed by a drift chamber with a 30 mm drift gap and a 7 mm amplification gap read out via a segmented cathode pad plane glued to a multi-layer carbon fiber honeycomb backing. The chambers are operated with a Xe/CO<sub>2</sub> (85%/15%) mixture with a total volume of 27.2 m<sup>3</sup> in order to achieve a high conversion probability for transition radiation photons. The chosen radiator provides about 100 boundaries. Hence approximately one transition radiation photon is expected to be produced in the sensitive range of soft X-rays. A synopsis of the main TRD parameters is given in Table 4.1.

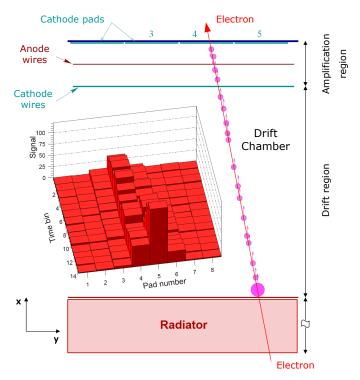

A particle traversing a TRD module enters the drift chamber together with the produced transition radiation photon. Both the charged particle and associated photon ionize the gas in the chamber and create electron clusters. The transition radiation photon is absorbed shortly after entering the drift chamber due to the efficient TR-photon absorption provided by the chosen gas mixture. The charged particle constantly produces a track of electron clusters on its way through the chamber. These electrons drift towards the amplification region where they are accelerated and further collide with gas atoms, thus producing avalanches of electrons around the anode wires (Fig. 4.1).

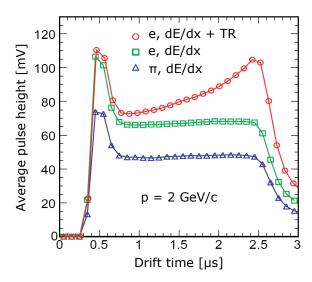

The large cluster at the beginning of the drift chamber produced from the transition radiation photon is specific to electrons and hence used to identify them from the large pion background. The average pulse shape versus the drift time

**Figure 4.1:** Schematic layout of the TRD (not to scale). The TRD consists of 540 read-out chambers arranged in 18 supermodules which are subdivided in 6 radial layers and 5 longitudinal stacks. On the bottom-right, the TRD operation principle is shown (projection in the plane perpendicular to the wires). Electrons produced by ionization energy loss and by TR absorption drift along the field lines toward the amplification region where they produce avalanches around the anode wires. These avalanches induce a signal on the cathode pads.

for electrons and pions is shown in Fig. 4.2. Electrons and pions have different pulse heights due to the different ionization energy loss. A characteristic peak at larger drift times of the electrons is due to the absorbed transition radiation. The produced electrons with energy loss due to ionization and transition radiation absorption induce signals on the cathode pads (Fig. 4.3).

| Pseudo-rapidity coverage               | $-0.84 < \eta < 0.84$                                   |

|----------------------------------------|---------------------------------------------------------|

| Azimuthal coverage                     | 360°                                                    |

| Radial position                        | 2.9 < <i>r</i> < 3.68 m                                 |

| Total longitudinal length              | Over 7.0 m                                              |

| Total number of detector modules       | 540                                                     |

| Largest (smallest) module              | 1,450 $	imes$ 1,144 (1,080 $	imes$ 922) mm <sup>2</sup> |

| Azimuthal segmentation                 | 18 sectors (supermodules)                               |

| Radial segmentation                    | 6 layers                                                |

| Longitudinal segmentation              | 5 stacks                                                |

| Active detector area                   | 683 m <sup>2</sup>                                      |

| Radiator                               | Fibers/foam sandwich, 4.8 cm per layer                  |

| Radial detector thickness              | $X/X_0 = 23.4\%$ for 6 layers                           |

| Detector gas                           | Xe/CO <sub>2</sub> (85%/15%)                            |

| Gas volume                             | 27.2 m <sup>3</sup>                                     |

| Depth of drift region                  | 3 cm                                                    |

| Depth of amplification region          | 0.7 cm                                                  |

| Nominal magnetic field                 | 0.4 T                                                   |

| Drift field                            | 0.7 kV/cm                                               |

| Drift velocity                         | 1.5 cm/ $\mu$ s                                         |

| Lorentz angle                          | $8^\circ$ at magnetic field 0.4 T                       |

| Number of readout channels             | 1,181,952                                               |

| Time samples in $r$ (drift)            | 20                                                      |

| ADC                                    | 10 bit, 10 MHz                                          |

| Number of multi-chip modules           | 70,848                                                  |

| Number of readout boards               | 4,104                                                   |

| Event size for $dN_{ch}/d\eta = 8,000$ | 11 MB                                                   |

| Event size for <i>pp</i>               | 6 kB                                                    |

| Trigger rate limit                     | 100 kHz                                                 |

|                                        |                                                         |

Table 4.1: Synopsis of the main TRD parameters. Adapted and updated from Ref. [39].

**Figure 4.2:** Average pulse height versus drift time. The different pulse heights indicate the different ionization energy loss of electrons (green rectangles) and pions (blue triangles). The characteristic peak at larger drift times of the electron (red circles) is due to the absorbed transition radiation. Figure adapted from Ref. [43].

**Figure 4.3:** Schematic illustration of the track assigned to an electron showing the projection in the bending plane of the ALICE magnetic field. In this direction the cathode plane is segmented into pads. The insert shows the distribution of pulse heights over pads and time bins spanning the drift region for a measured electron track. Figure modified from Ref. [43].

In order to detect produced electrons, each TRD readout chamber has 144 pads in direction of the amplification wires ( $r\varphi$ -direction) and either 12 or 16 pad rows in *z*-direction in the local coordinate frame of a single readout chamber (see Fig. 4.3). The pads have a typical area of 6 – 7 cm<sup>2</sup> and cover a total active area of 683 m<sup>2</sup> with approximately 1.2 million readout channels.

# 4.3 Readout and basic infrastructure

#### 4.3.1 Readout electronics chain

The TRD readout electronics is mounted directly on the readout chambers (ROC). The signals are read out at 10 MHz sampling rate so that the signal height on all pads is sampled in time bins of 100 ns. Thus the readout data from the TRD are characterized by four coordinates: chamber, pad row, pad column and time bin. In the drift region a time bin corresponds to a space interval of 1.5 mm in drift direction according to an average drift velocity of 1.5 cm/ $\mu$ s (2  $\mu$ s total drift time).

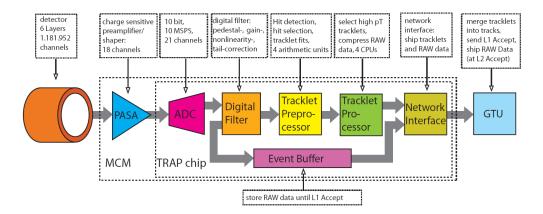

Figure 4.4: Overview of the TRD readout electronics chain. Figure adapted from Ref. [43].

The readout pads feed a charge-sensitive preamplifier whose noise is determined by its input capacity, therefore requiring its proximity to the pad planes. The preamplifier also implements first-level shaping and tail cancellation functionality. The differential amplifier outputs are digitized by a custom 10-bit ADC at 10 MHz. The remainder of the TRD electronics chain (Fig. 4.4) implements a short 64-word single event buffer plus a tracklet processor which identifies potential high- $p_T$  track candidates for further processing.

Beyond the 1.2 million analog channels which are digitized during the 2  $\mu$ s drift time, the TRD also implements an on-line trigger which is capable of tracking most of the up to 6,000 expected charged particles within the six detector layers with a very tight time budget of 6  $\mu$ s for all digitization and processing [44].

The readout is performed in two stages: first, during the trigger processing, which all tracklet candidates are shipped within 600 ns from 65,664 MCMs to the global tracking unit using 1,080 optical links each at 2.5 Gb/s speed for merging of the six detector layers; and second, in which the event buffer is read out in case the event is accepted [45]. The first stage of the readout is started by the L0 trigger, and the second stage is triggered by the L1 signal arrival.

#### 4.3.2 Low voltage

Low voltage power is required by several TRD sub-systems, namely, readout boards, power control unit (PCU), power distribution box (PDB), pre-trigger system, and global tracking unit. All together, in normal running conditions, it amounts an electrical power of more than 65 kW. For this to be accomplished, 89 water-cooled Wiener PL512/M [46] low voltage power supplies provide 255 individual channels.

#### 4.3.3 High voltage

The TRD readout chambers require an electric potential of -2.1 kV to generate the necessary drift field and about +1.7 kV in order to reach sufficient gas gain. This leads to a total of 1,080 HV channels needed to operate the entire detector. The specifications for each channel are demanding. For instance, the relative stability is required to be better than 0.1% over 24 hours while the ripple per channel is required to be smaller than 50 mV peak-to-peak. A current readout sensitivity below 1 nA and an efficient protection mechanism against over-voltages are also required. Currently, the TRD HV system is foreseen to be operated with 32-channel Iseg EDS series modules [47] for both drift and anodes. The TRD readout electronics is described in more detail in Chapter 5, the TRD infrastructure is presented in Chapter 9, and the TRD sub-systems are explained in detail in Chapter 10 from the controls point of view.

Part II

# **TRD FEE quality assurance**

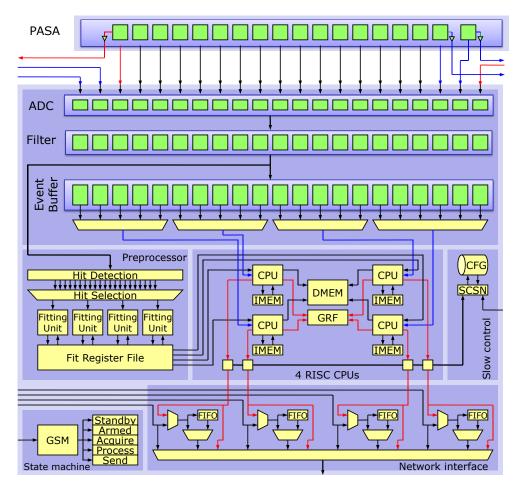

**Introduction** The TRD front-end electronics (FEE) performs two main tasks. First, it acquires, digitizes, and buffers the detector data from over 1.2 million analog channels; second, it computes local on-line tracking within 6  $\mu$ s. The TRD FEE components are presented in this Chapter.

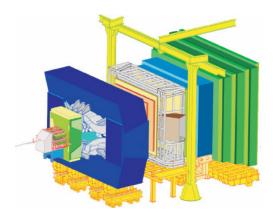

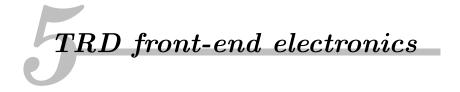

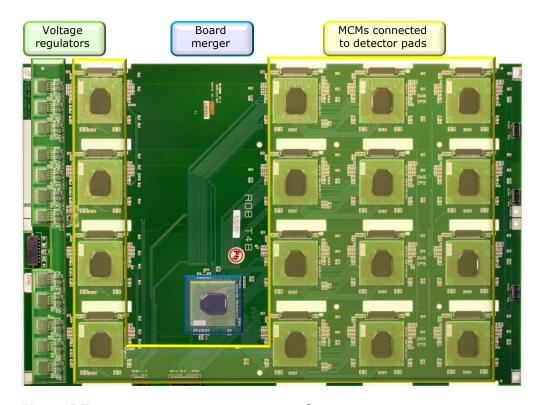

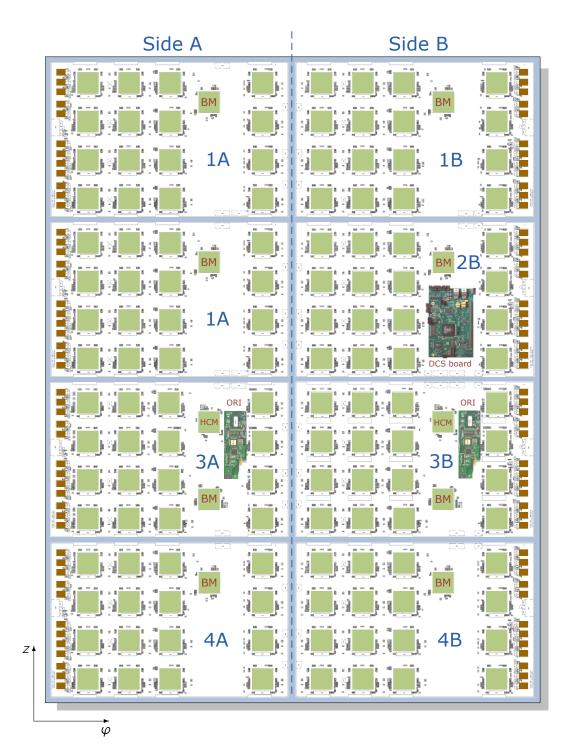

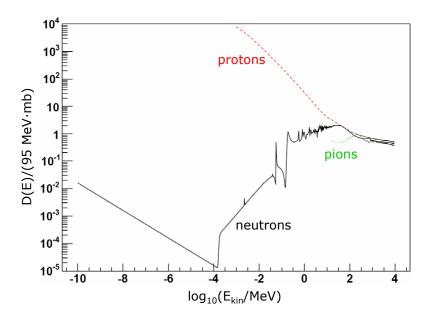

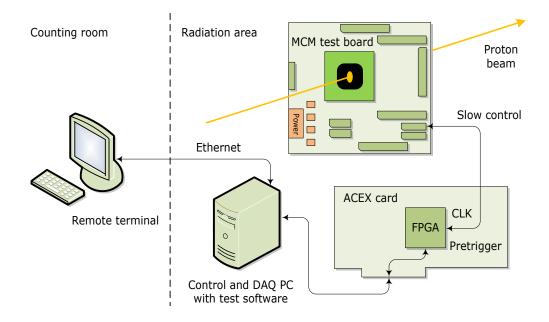

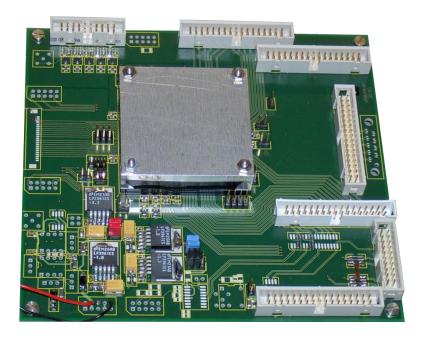

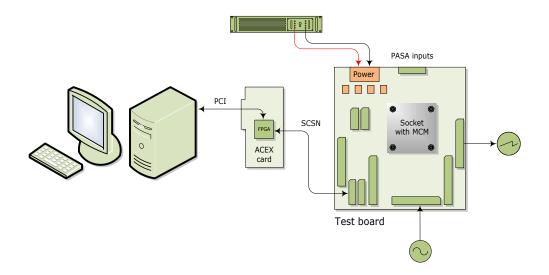

**Figure 5.1:** Front-end electronics components mounted on a TRD readout chamber with average dimensions of  $1.4 \times 1.1 \text{ m}^2$ . The various FEE components are described in this Chapter.

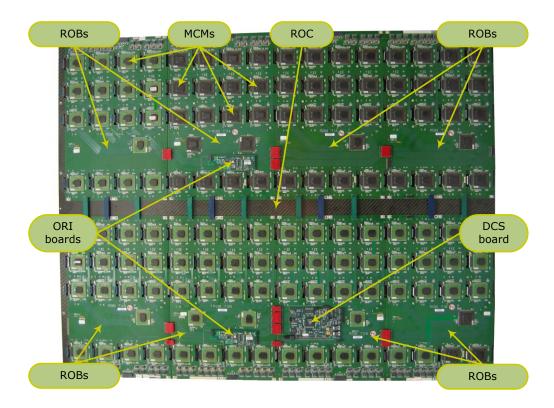

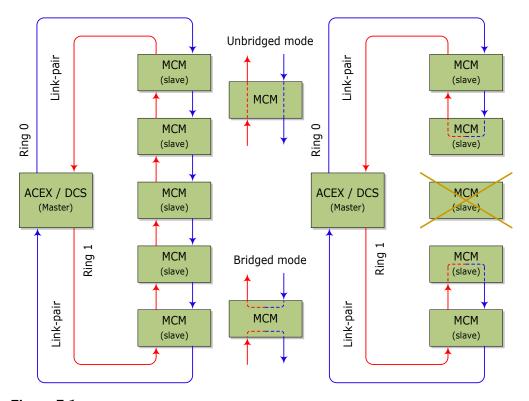

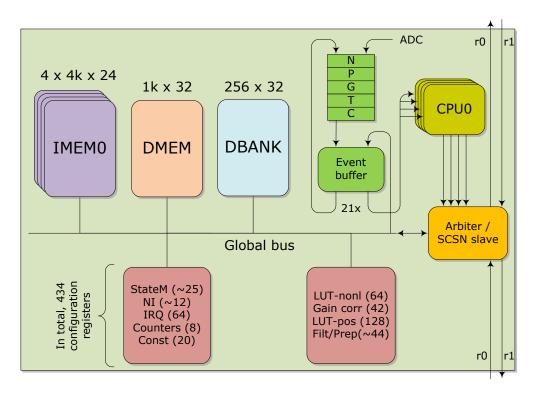

The FEE task implies a very high required integration density and emphasizes the requirements on the total power dissipated by all electronics components. In order to minimize the overall noise and to cope with the data rate, the whole FEE is mounted directly on the readout chambers (Figs. 5.1 and 5.2). The main functionality is implemented in a Multi-Chip Module (MCM), the basic FEE building block, consisting of two custom chips: one pure analog chip, the Preamplifier and Shaping Amplifier (PASA) [48] and one mixed mode TRAcklet Processor (TRAP) [49] chip.

**Figure 5.2:** The TRD front-end electronics is mounted directly on the readout chambers. It implements over 1.2 million analog channels and an on-board computer farm of over a quarter-million central processing units for the triggering and identifying of electrons.

The MCMs are hosted by large custom Read-Out Boards (ROB) [50] that integrate voltage regulators, detector control interface boards and optical data links. The TRD is read out by 4,104 ROBs each one hosting up to 18 MCMs leading to a total inventory of 70,848 MCMs and an on-board computer farm of over a quarter-million central processing units (CPUs).

#### **Box 5.1:** Readout board functionality

A fully equipped ROB provides the necessary setup for exploiting the whole complex functionality of the FEE as it interconnects 17 or 18 MCMs, distributes system clock and pre-trigger signals, merges and ships data over optical links and hosts slow control interface boards.

## 5.1 Multi-Chip Module

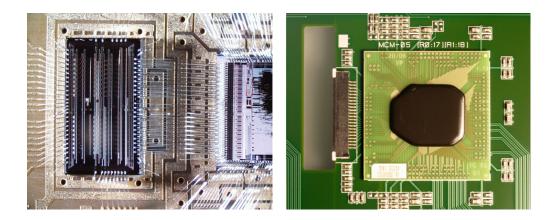

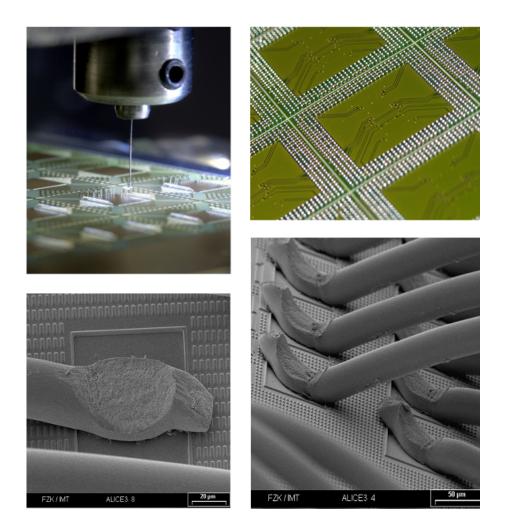

The TRD MCM houses both PASA and TRAP chips on one carrier, namely, a full custom  $4 \times 4$  cm<sup>2</sup> printed circuit board (PCB) designed as *Ball Grid Array* (BGA) consisting of 432 pads and soldered directly to the ROBs. The PASA analog outputs are bonded chip-to-chip to the TRAP ADC inputs (Fig. 5.3). Some selected design and production parameters are given in Table 5.1.

**Figure 5.3:** Chip-to-chip bonding wires connecting PASA outputs with TRAP ADC inputs (left). The entire PASA chip is observed. Most of the MCM bonds are chip-to-board including power and ground signals, PASA inputs, and all the I/O signals of the TRAP chip. After application of glob-top for mechanical protection and cooling interface, the MCMs are soldered directly to the ROBs (right).

The MCMs are manufactured using the low-cost *chip-on-board* (COB) technology which offers the possibility to integrate more functions in the same volume to fit to a limited place. For the TRD MCM production, the silicon chips (PASA and TRAP) are glued directly to the PCB substrate and then (inter-)connected by bonding with gold wires with a diameter of 25  $\mu$ m. An encapsulation resin (glob-top) is dispensed on the MCM to guarantee stability against thermal and mechanical stress, thus protecting the assembly. The MCM has 18 charge sensitive inputs, three differential ADC inputs, three differential PASA outputs and several digital ports.

| BGA                                                              |                                   |  |  |  |

|------------------------------------------------------------------|-----------------------------------|--|--|--|

| Package type $BGA432 (31 \times 31 \text{ pads}, 4 \text{ row})$ |                                   |  |  |  |

| Ball pitch                                                       | 1.27 mm                           |  |  |  |

| Ball diameter                                                    | 0.75 mm                           |  |  |  |

| Ball composition                                                 | tion Sn/Pb (37%/63%)              |  |  |  |

| РСВ                                                              |                                   |  |  |  |

| Dimensions                                                       | $41.15 \times 41.15 \text{ mm}^2$ |  |  |  |

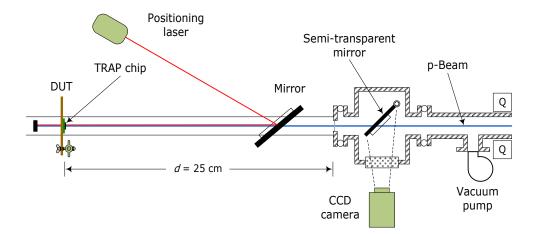

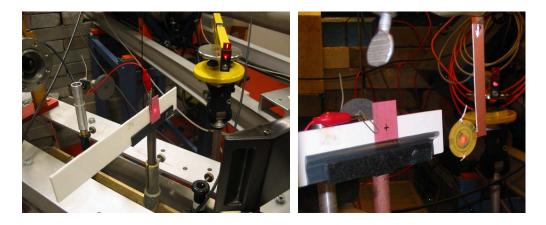

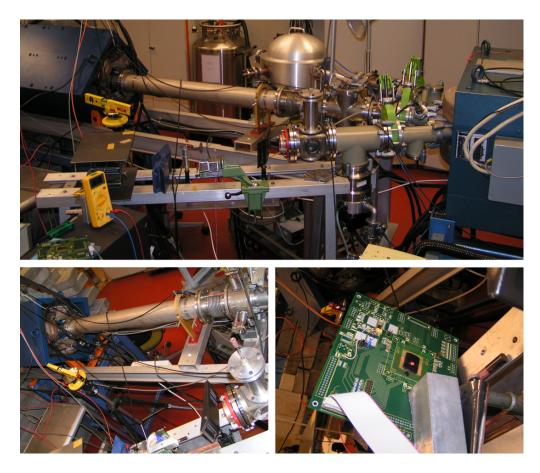

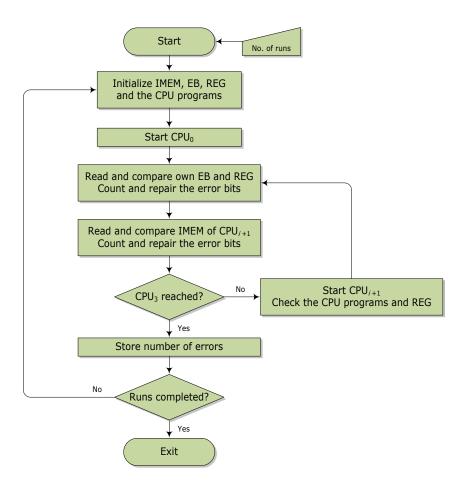

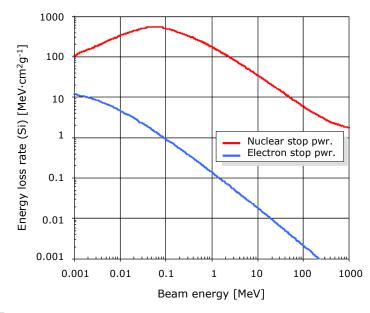

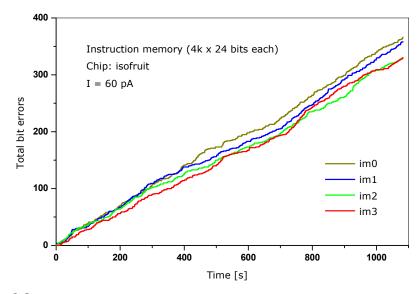

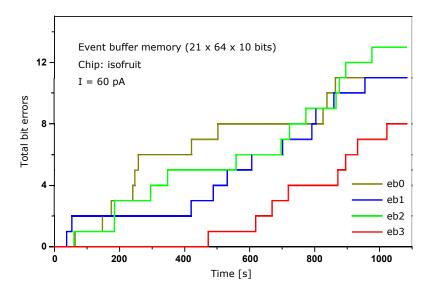

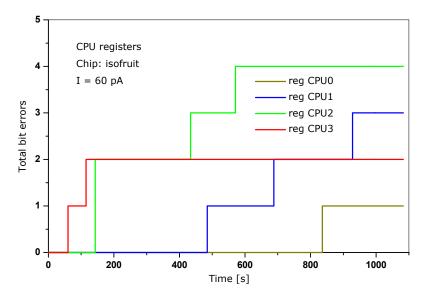

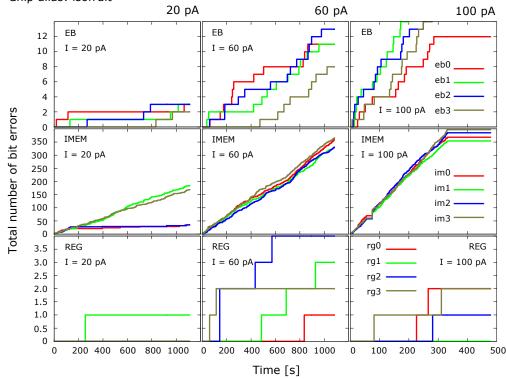

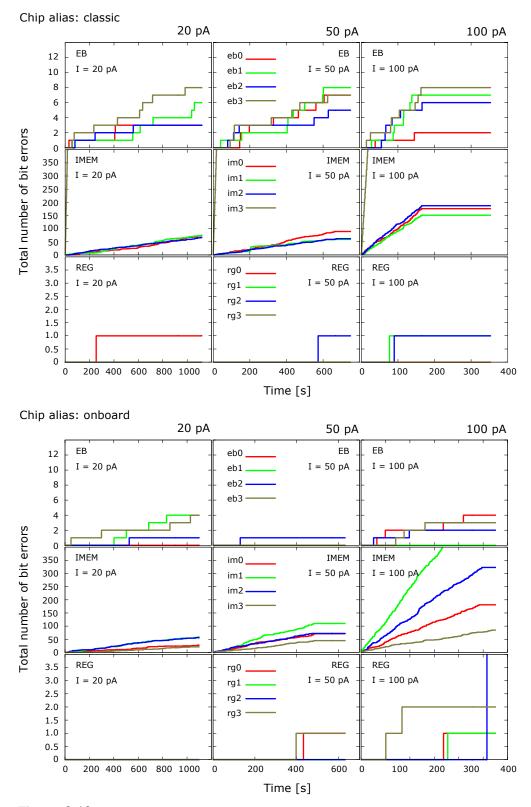

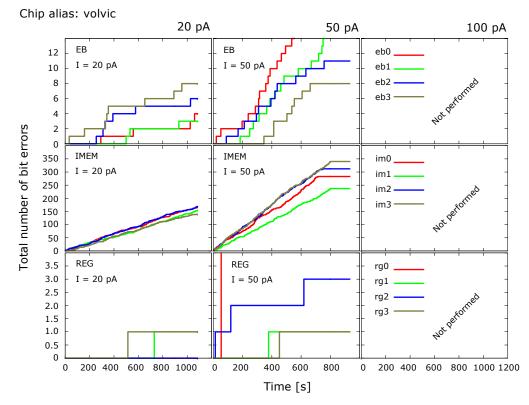

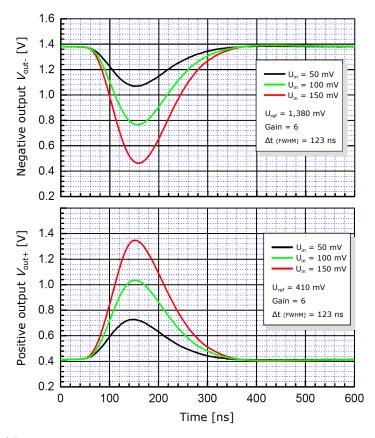

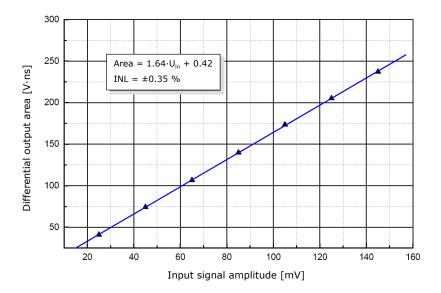

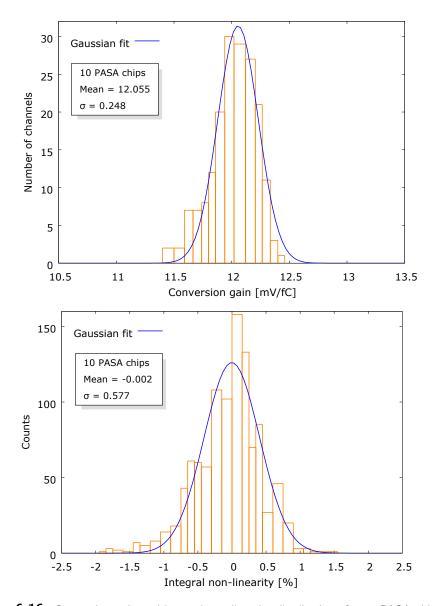

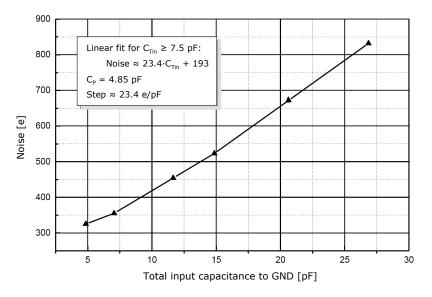

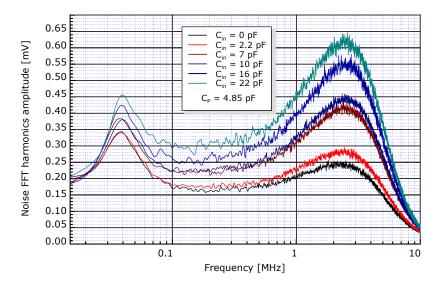

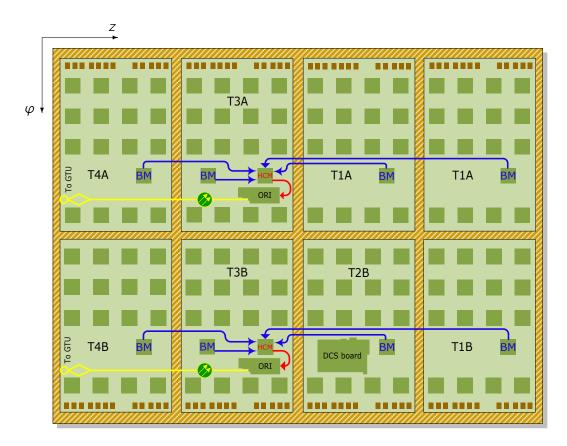

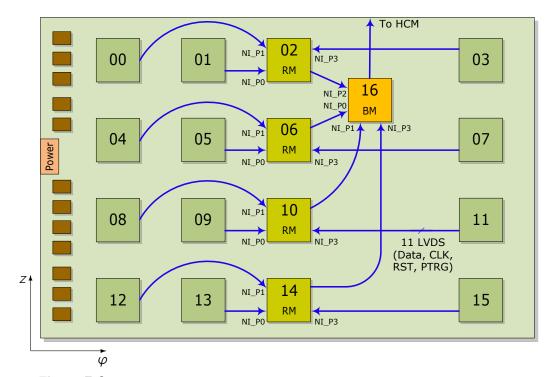

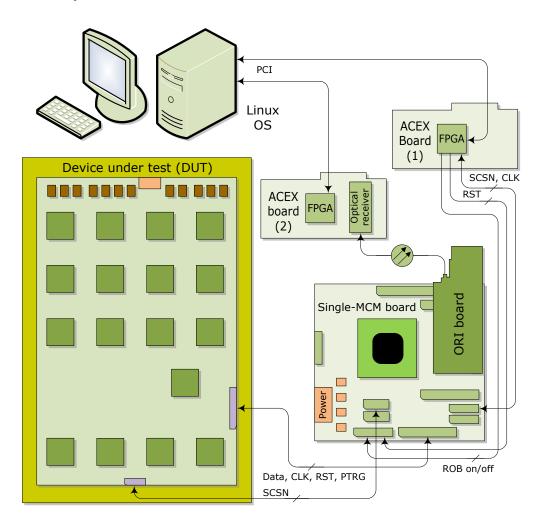

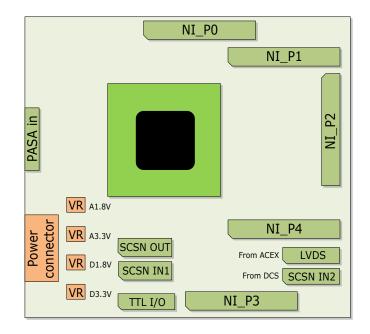

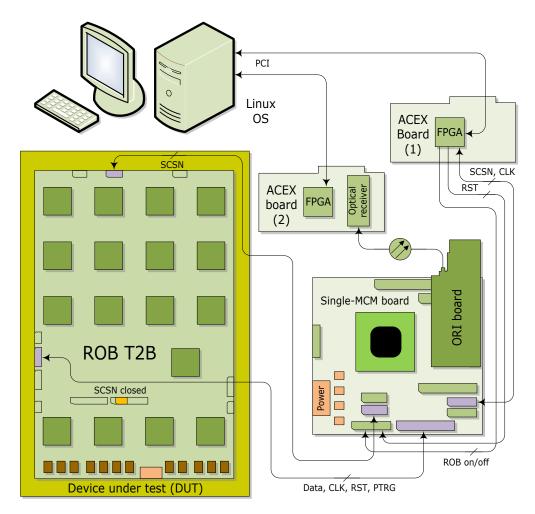

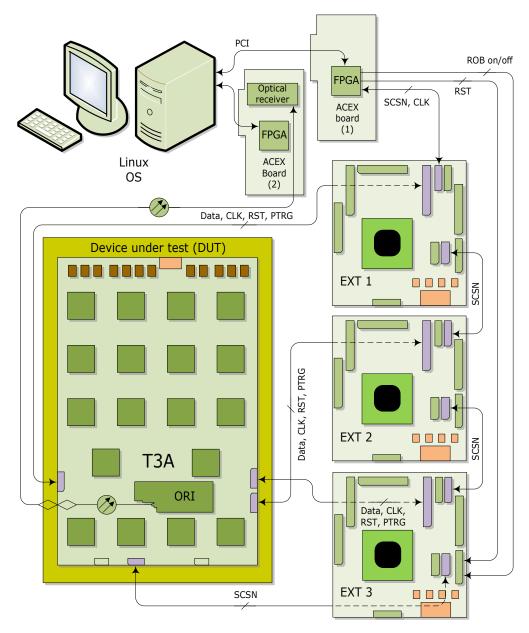

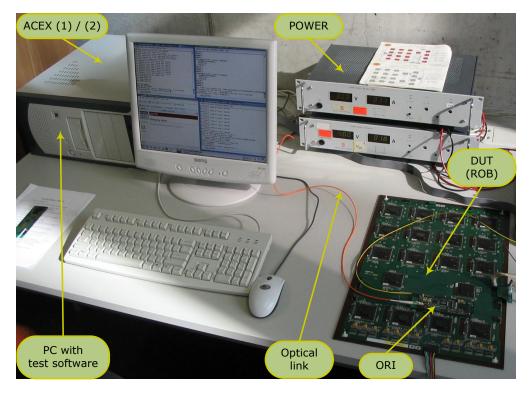

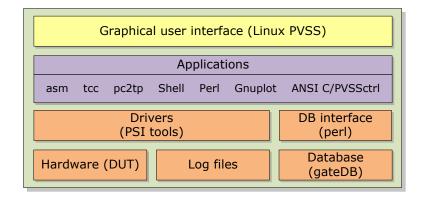

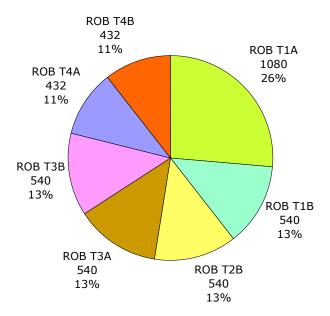

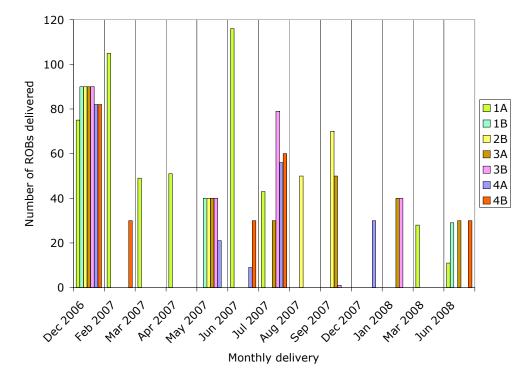

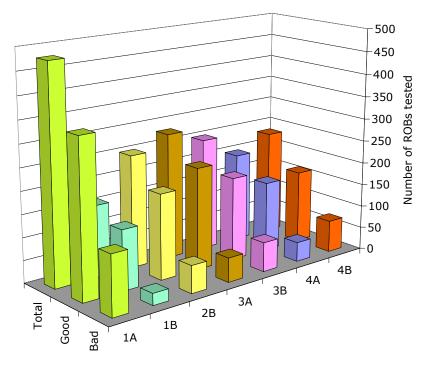

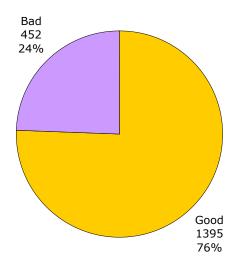

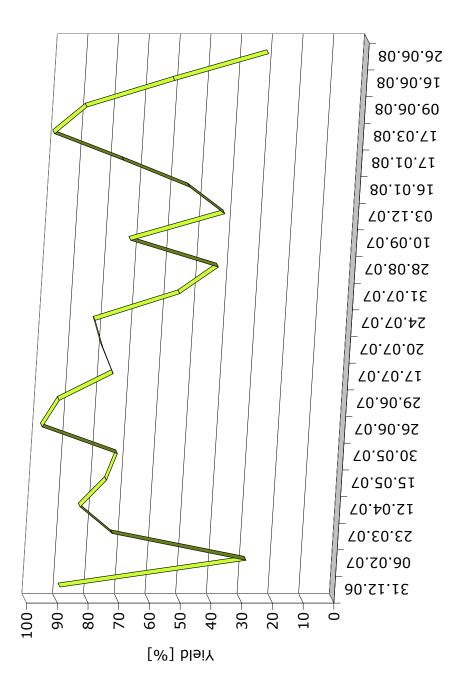

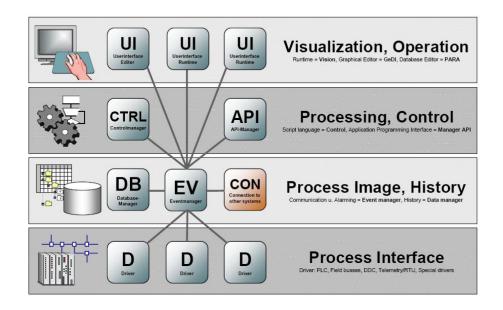

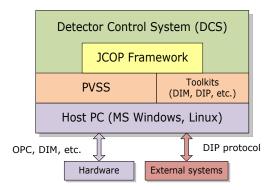

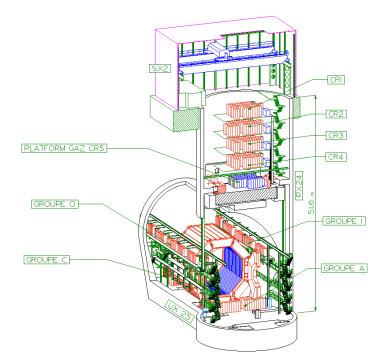

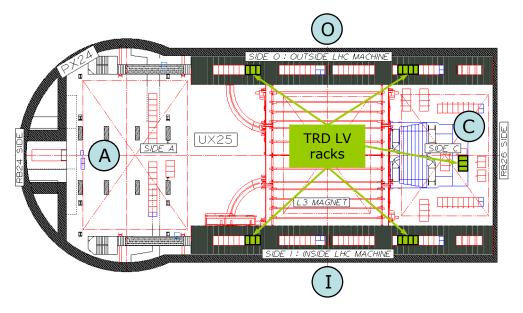

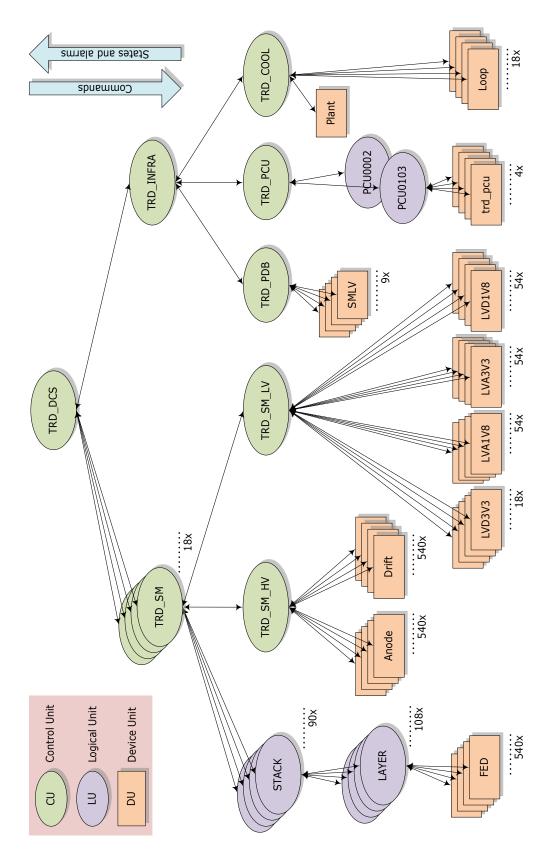

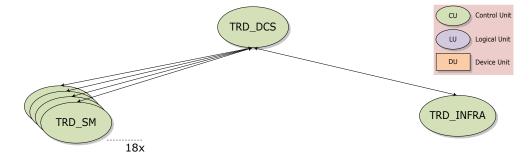

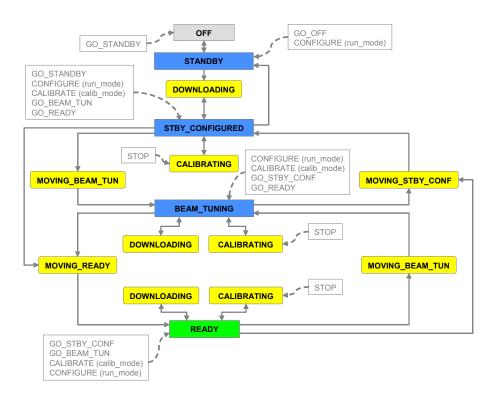

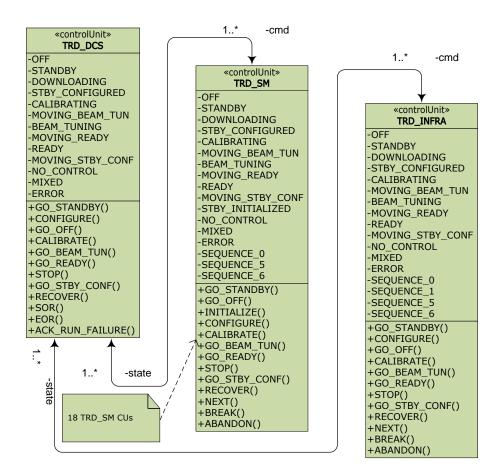

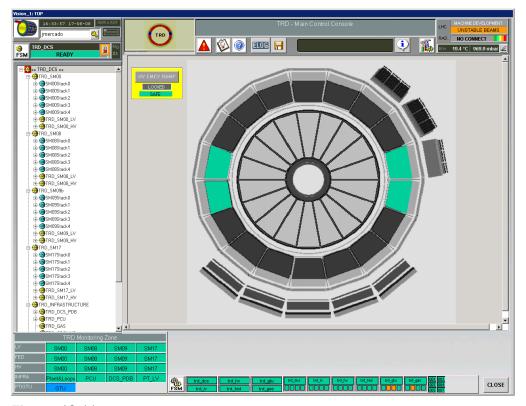

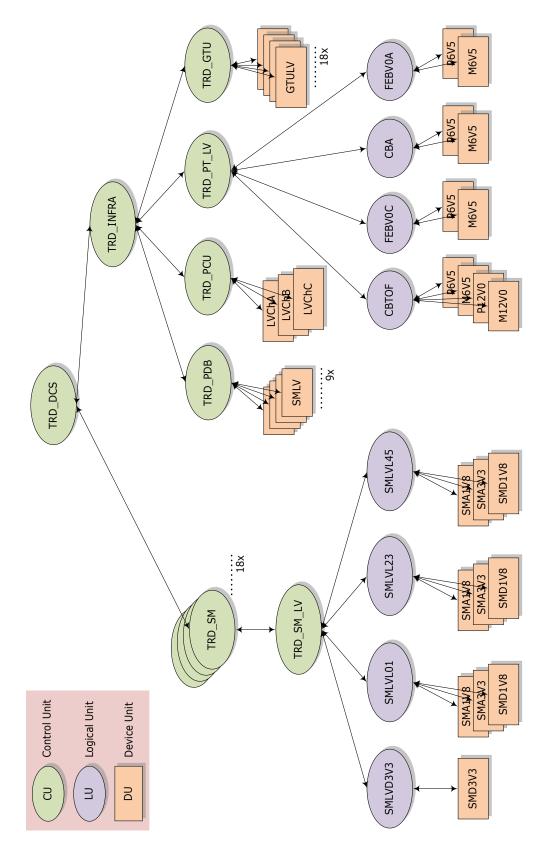

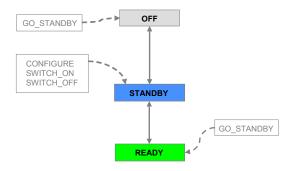

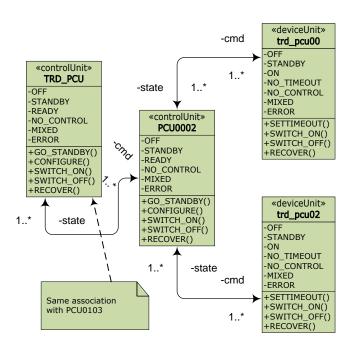

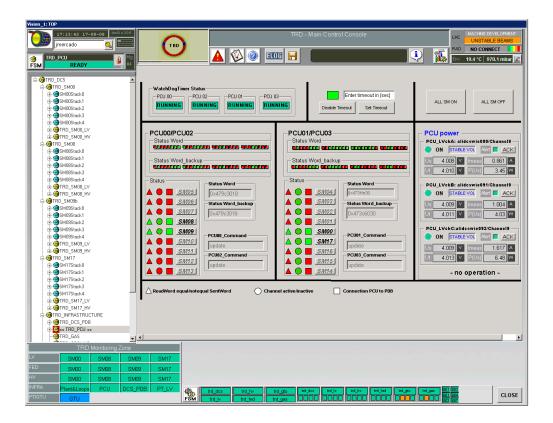

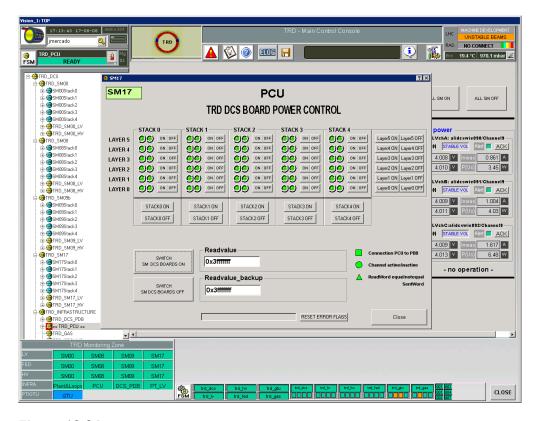

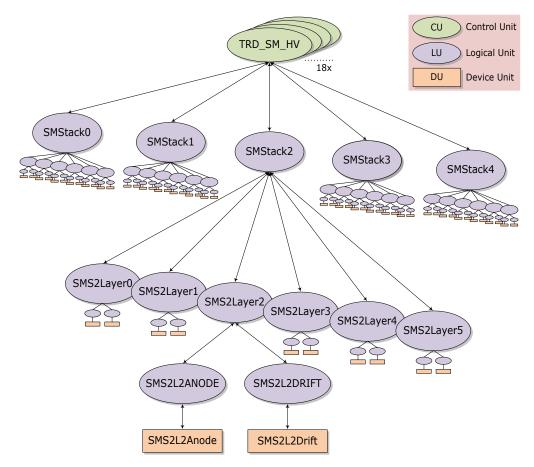

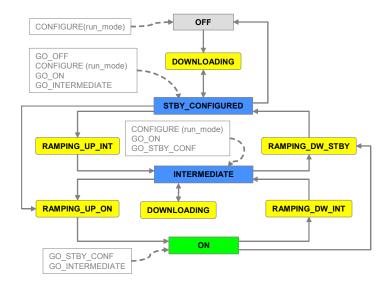

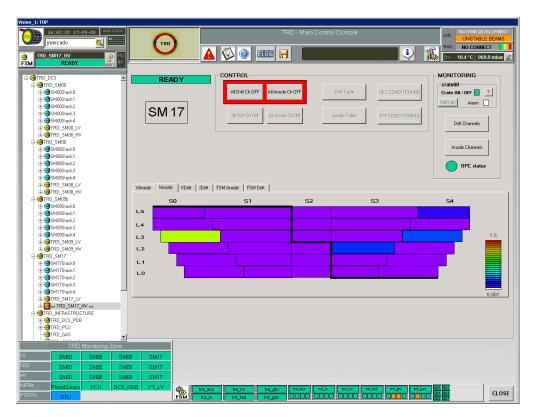

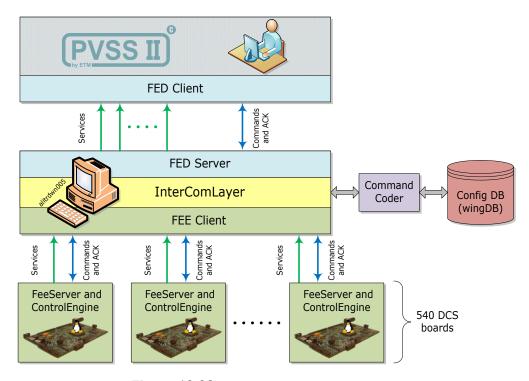

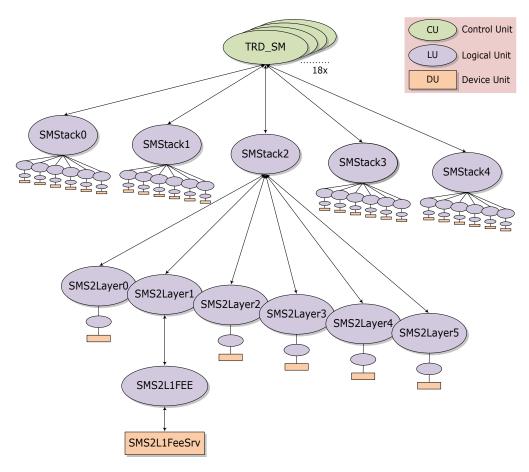

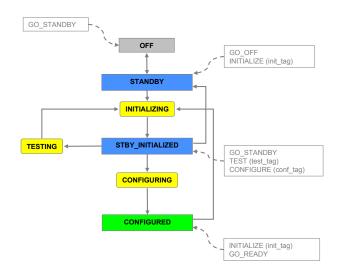

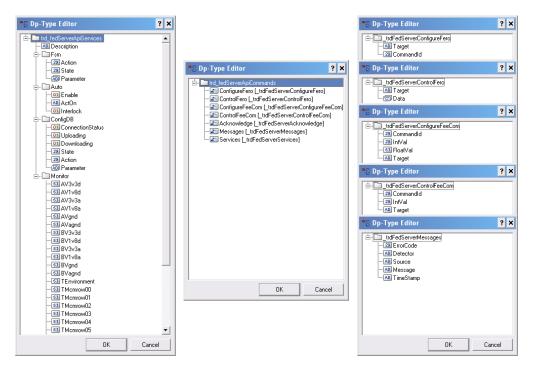

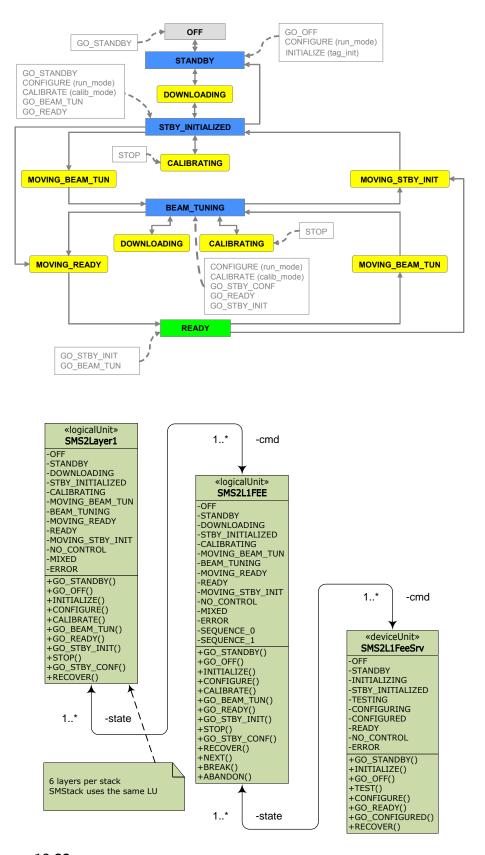

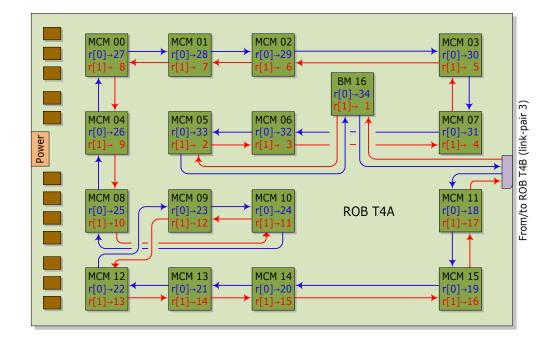

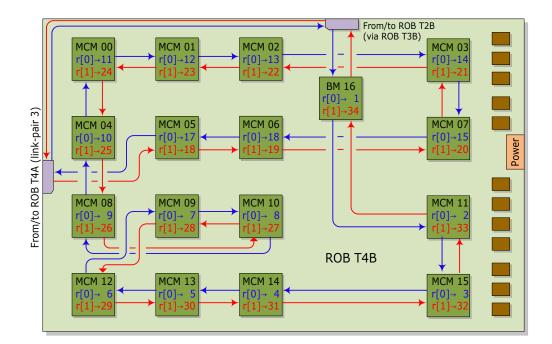

| Conductive layers                                                | 2 layers                          |  |  |  |