# Dissertation submitted to the

## Combined Faculty of Natural Sciences and Mathematics

of Heidelberg University, Germany

for the degree of

Doctor of Natural Sciences

Put forward by

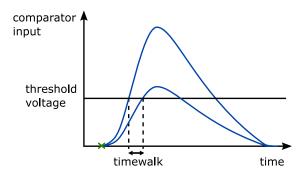

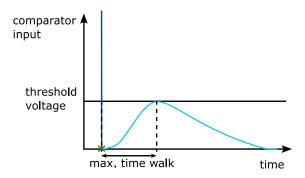

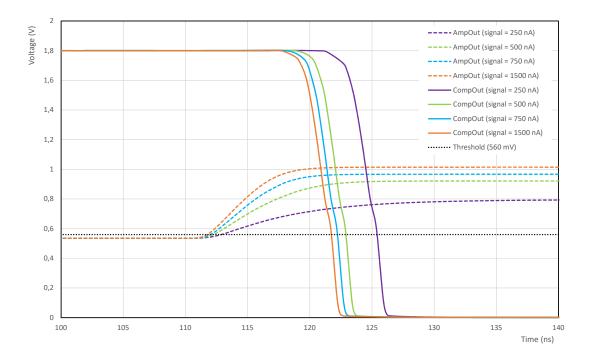

Alena Larissa Weber

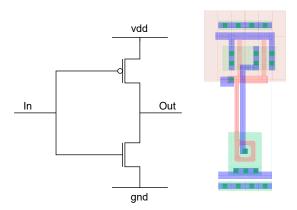

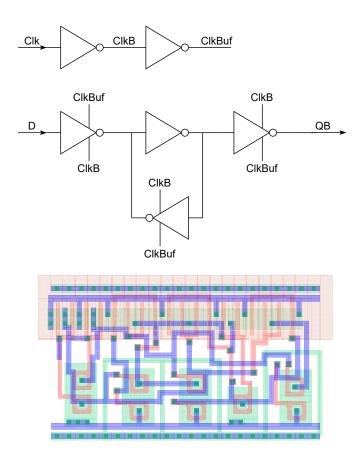

born in: Karlsruhe

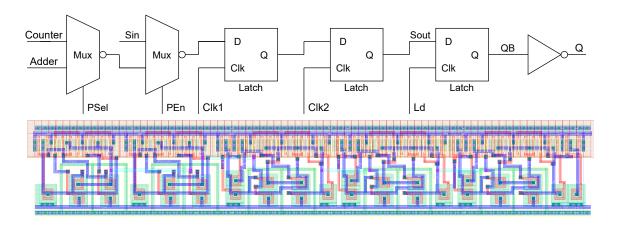

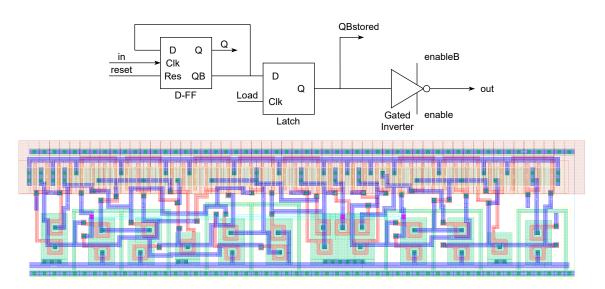

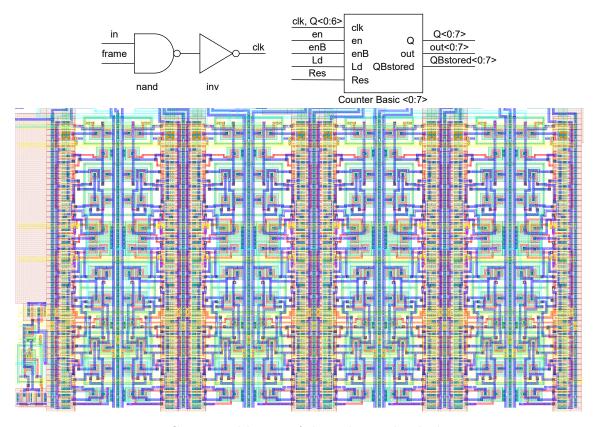

Oral examination: 12.10.2021

# Development of Integrated Circuits and Smart Sensors for Particle Detection in Physics Experiments and Particle Therapy

Referees:

Prof. Dr. André Schöning

Jun.-Prof. Dr. habil. Loredana Gastaldo

## **Abstract**

Future particle physics experiments have to cope with increasing demands on particle detection concerning resolution and high rates. Particle detection is the key task of tracking detectors in particle physics experiments and in medical physics in the field of particle therapy. These detectors determine the trajectory of the particles, which allows the reconstruction of the vertices and the identification of the particles. Particle detection is also important for monitoring the particle beam used for medical applications in particle therapy centres. For this purpose, particle detectors are used to ensure safe and accurate treatment.

High Voltage Monolithic Active Pixel Sensors (HV-MAPS) are a new promising technology for smart particle detection sensors. They offer promising time and vertex resolution, are cost-effective to produce, are radiation hard and can be thinned down to  $50\,\mu m$ .

The focus of the thesis is to investigate the suitability of HV-MAPS sensors for tracking detectors and beam monitoring and to develop smart sensor chips for these applications. In the course of this thesis, two HV-MAPS sensor families with multiple generations, the MuPix and HitPix, were developed in HV-CMOS technology. The MuPix is a large HV-CMOS sensor, which is suitable as a tracking sensor and will be used in the Mu3e experiment. It offers a time resolution of less than 10 ns and an efficiency of more than 99.8%. The HitPix implements in-pixel counting and fast projection readout. It can handle high rates and radiation levels. This makes it suitable as a beam monitor, especially for particle therapy centres.

With the MuPix and the HitPix, two HV-MAPS chips have been successfully designed for particle detection with the advantages of HV-CMOS technology. Therefore, this thesis provides an important contribution to the application and further development of a promising new technology, both in the field of medical and particle physics.

## Zusammenfassung

Zukünftige Teilchenphysikexperimente müssen steigenden Anforderungen an die Teilchendetektion hinsichtlich Auflösung und hohen Raten gerecht werden. Der Teilchennachweis ist die Hauptaufgabe von Spurdetektoren in Teilchenphysikexperimenten und in der medizinischen Physik auf dem Gebiet der Ionenstrahltherapie. Mit Hilfe dieser Detektoren werden die Spuren von Teilchen bestimmt, wodurch der Ursprung und die Art der einzelnen Teilchen rekonstruiert werden können. Auch zur Überwachung des medizinisch genutzten Teilchenstrahls in Ionenstrahltherapiezentren ist die Teilchendetektion wichtig. Hierfür werden Teilchendetektoren eingesetzt, um eine sichere und genaue Behandlung zu gewährleisten.

Ein neues vielversprechendes Konzept für intelligente Sensoren zur Teilchendetektion sind High Voltage Monolithic Active Pixel Sensors (HV-MAPS). Sie bieten eine vielversprechende Zeit- und Ortsauflösung, sind kostengünstig in der Herstellung, strahlenhart und können auf 50 µm gedünnt werden.

Der Schwerpunkt der Arbeit liegt auf der Untersuchung der Eignung von HV-MAPS Sensoren für Spurdetektoren und Strahlüberwachung sowie auf der Entwicklung von Sensorchips für diese Anwendungen. Im Rahmen dieser Arbeit wurden zwei HV-MAPS Sensorfamilien mit mehreren Generationen, der MuPix und der HitPix, in HV-CMOS Technologie entwickelt. Der MuPix ist ein großer HV-CMOS Sensor, der sich als Spursensor eignet und im Mu3e Experiment eingesetzt werden wird. Er zeichnet sich durch eine Zeitauflösung unter 10 ns und eine Effizienz von über 99,8 % aus. Der HitPix ermöglicht eine pixelinterne Zählfunktion und eine schnelle Projektionsauslese. Er kann hohe Teilchenraten verarbeiten und hält einer hohen Strahlungsbelastung stand. Dadurch eignet er sich als Strahlmonitor, insbesondere für Ionenstrahltherapiezentren.

Mit dem MuPix und dem HitPix wurden erfolgreich zwei HV-MAPS Chips für die Teilchendetektion mit den Vorteilen der HV-CMOS Technologie entwickelt. Damit leistet diese Arbeit einen wichtigen Beitrag zur Anwendung und Weiterentwicklung einer vielversprechenden neuen Technologie, sowohl im Bereich der Medizin- als auch der Teilchenphysik.

## Contents

| Αl | ostra | ct                                                              | į   |

|----|-------|-----------------------------------------------------------------|-----|

| Zu | ısamı | menfassung                                                      | iii |

| I  | Int   | roduction                                                       | 1   |

| 1  | Mot   | ivation, outline and contributions                              | 3   |

| 2  | Phy   | sics of semiconductor sensors                                   | 9   |

|    | 2.1   | Basics of semiconductors                                        | 10  |

|    |       | 2.1.1 Different types of semiconductors                         | 10  |

|    |       | 2.1.2 PN-junction                                               | 15  |

|    | 2.2   | Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)      | 20  |

|    |       | 2.2.1 Structure and working principle of MOSFETs                | 20  |

|    |       | 2.2.2 IV characteristics                                        | 22  |

|    | 2.3   | Noise types                                                     | 24  |

|    | 2.4   | Radiation damage                                                | 26  |

| 3  | Sen   | sors for particle detection and tracking                        | 29  |

|    | 3.1   | Hybrid and monolithic pixel sensors                             | 30  |

|    | 3.2   | High Voltage Monolithic Active Pixel Sensors (HV-MAPS)          | 31  |

| 4  | App   | plication for particle physics experiments and particle therapy | 35  |

|    | 4.1   | Application for the Mu3e experiment                             | 36  |

|    |       | 4.1.1 Motivation of the Mu3e experiment                         | 36  |

|    |       | 4.1.2 Concept of the Mu3e detector system                       | 36  |

|    |       | 4.1.3 MuPix – sensor development for Mu3e                       | 40  |

|    | 4.2   | Application for particle therapy                                | 41  |

|    |       | 4.2.1 Particle therapy at HIT                                   | 41  |

|    |      | 4.2.2     | Beam monitoring at HIT                                                | 42  |

|----|------|-----------|-----------------------------------------------------------------------|-----|

|    |      | 4.2.3     | $\operatorname{HitPix}$ – sensor development for $\operatorname{HIT}$ | 44  |

| II | De   | velopi    | ment of integrated circuits for HV-MAP sensors                        | 47  |

| 5  | Amı  | plifier   |                                                                       | 49  |

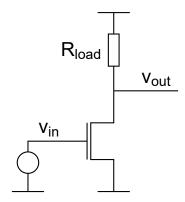

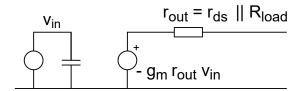

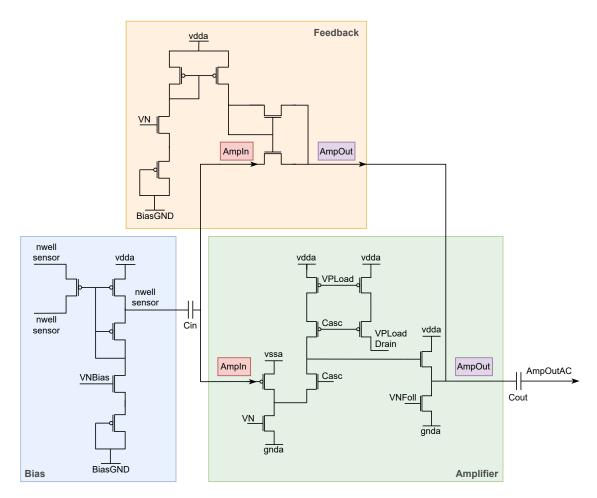

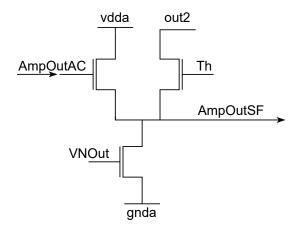

|    | 5.1  | Voltag    | e sensitive amplifier                                                 | 50  |

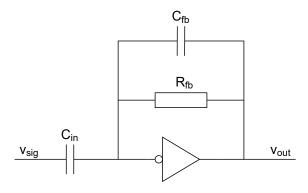

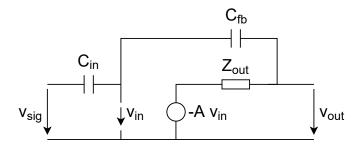

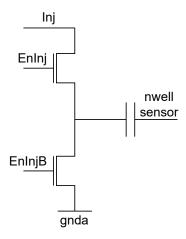

|    | 5.2  | Charge    | e sensitive amplifier                                                 | 52  |

|    | 5.3  | Test si   | gnal generation                                                       | 56  |

| 6  | Con  | nparat    | or                                                                    | 57  |

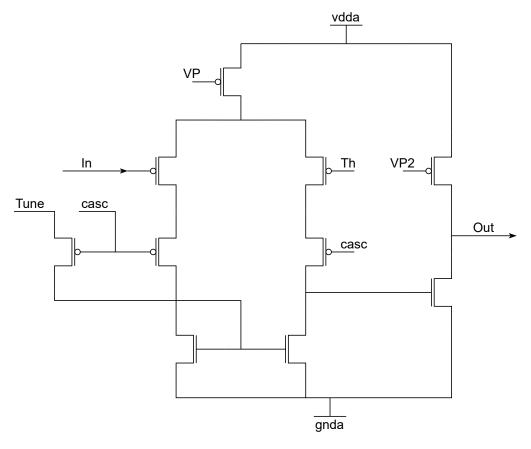

|    | 6.1  | Optim     | ised comparator design                                                | 58  |

|    | 6.2  | Compa     | arator placement                                                      | 60  |

|    | 6.3  | Timew     | alk problem                                                           | 62  |

|    | 6.4  | Timew     | ralk correction methods                                               | 64  |

|    |      | 6.4.1     | Time over threshold method                                            | 64  |

|    |      | 6.4.2     | Two threshold method                                                  | 64  |

| 7  | Rad  | liation h | nard library                                                          | 67  |

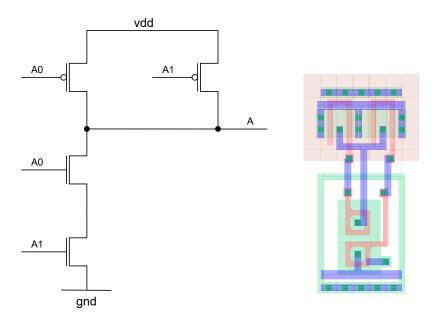

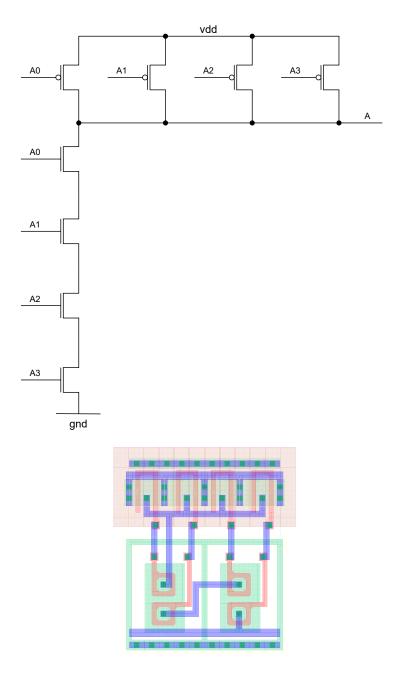

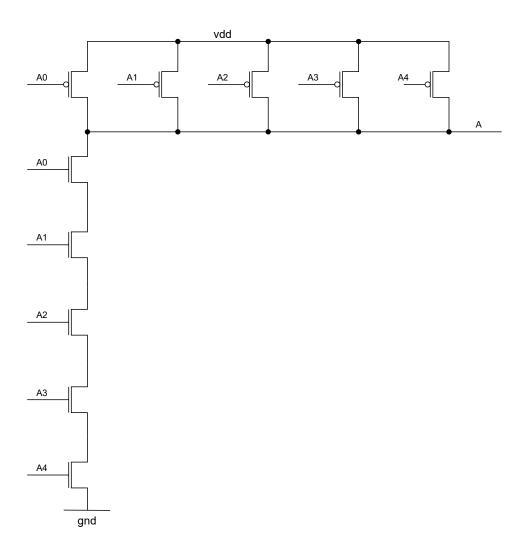

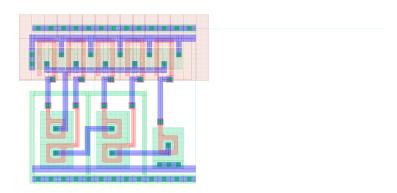

|    | 7.1  | Radiat    | ion hard elements with enclosed NMOS transistors                      | 68  |

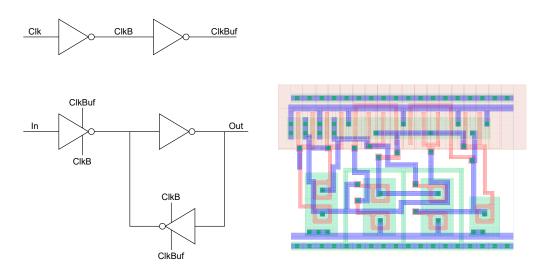

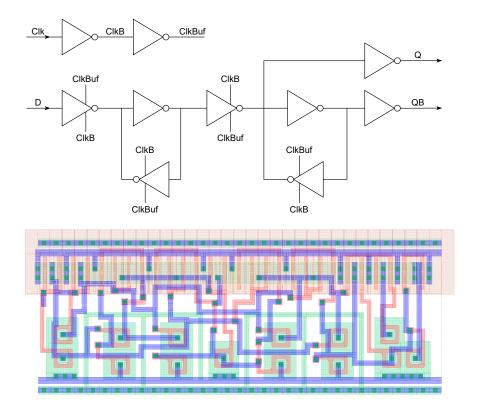

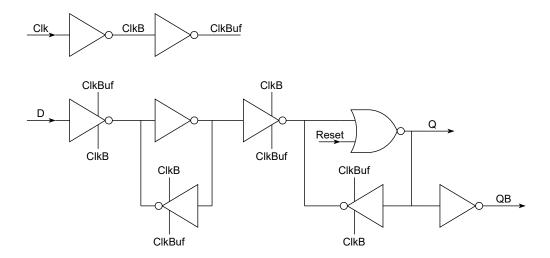

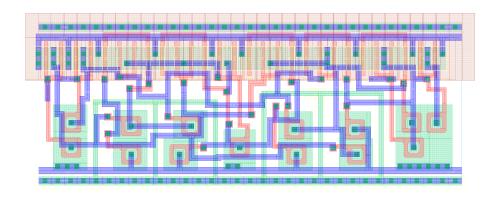

|    | 7.2  | Librar    | y elements                                                            | 68  |

| 8  | Cou  | ınter ar  | nd adder                                                              | 81  |

|    | 8.1  | Radiat    | ion hard 8 bit in-pixel counter                                       | 82  |

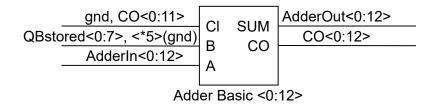

|    | 8.2  | In-pixe   | el 13 bit adder                                                       | 84  |

| Ш  | De   | evelopi   | ment of smart sensor chips and characterisation                       | 87  |

| 9  | MuF  | Pix chip  | for particle detection in physics experiments                         | 89  |

|    | 9.1  |           | ecture                                                                | 90  |

|    |      | 9.1.1     | MuPix pixel                                                           | 93  |

|    |      | 9.1.2     | Column drain readout                                                  | 95  |

|    | 9.2  | Charac    | eterisation                                                           | 104 |

|    |      | 9.2.1     | Measurements of efficiency and threshold tuning of MuPix8             |     |

|    |      | 9.2.2     | Measurements of threshold tuning and voltage regulator of MuPix10     | 106 |

| 10 | HitP | ix chip   | for particle detection in particle therapy                            | 111 |

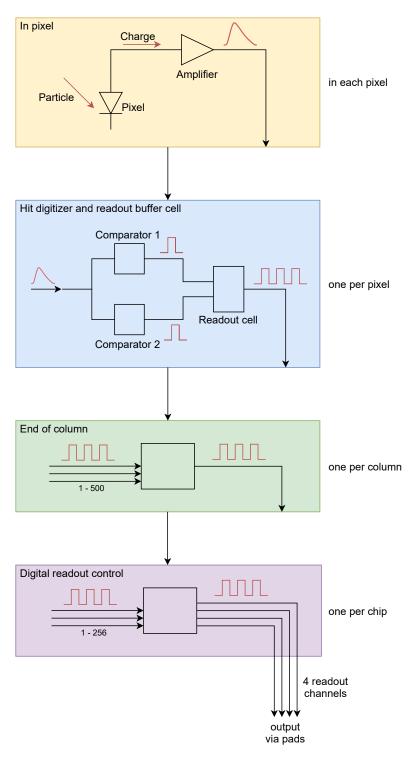

|    | 10.1 | Archite   | ecture                                                                | 112 |

|    |      | 10.1.1    | HitPix pixel                                                          | 114 |

|    |      | 10.1.2    | Address based readout                                                 | 116 |

|     | 10.2   | Measu  | rement setup                                                                                                             | 121 |

|-----|--------|--------|--------------------------------------------------------------------------------------------------------------------------|-----|

|     | 10.3   | Charac | eterisation                                                                                                              | 124 |

|     |        | 10.3.1 | Measurements of leakage current, amplifier and mismatch of non-                                                          |     |

|     |        |        | irradiated HitPix                                                                                                        | 124 |

|     |        | 10.3.2 | Measurements of leakage current and amplifier of irradiated $\operatorname{HitPix}$ .                                    | 134 |

|     |        | 10.3.3 | $Test beam \ measurements \ of \ counter \ and \ adder \ modes \ of \ non-irradiated$                                    |     |

|     |        |        | $Hit Pix \ \dots $ | 138 |

|     |        | 10.3.4 | Testbeam measurements of counter mode of irradiated HitPix                                                               | 142 |

| IV  | Sur    | mmary  | y and conclusion                                                                                                         | 147 |

| ٧   | Ap     | pendi  | x                                                                                                                        | 153 |

| Pu  | blico  | ations |                                                                                                                          | 155 |

| Bik | oliogi | raphy  |                                                                                                                          | 157 |

| Lis | t of F | igures |                                                                                                                          | 167 |

| Ac  | knov   | wledge | ements – Danksagung                                                                                                      | 173 |

## Part I

## Introduction

## Chapter 1

## Motivation, outline and contributions

This section presents the motivation of this thesis, describes the outline and explains the author's contributions.

#### Motivation

Particle detectors for future particle physics experiments have to meet increasingly high requirements in terms of resolution and high rates.

In order to discover new physics beyond the standard model of particle physics, increasingly sensitive experiments are being built. An important part of these experiments are tracking detectors that record the trajectories of particles. This requires high time and vertex resolution as well as high detection efficiency and radiation hardness. Another application is particle therapy. Here, particle beams are used for tumour treatment. Beam monitoring is necessary to observe and verify the beam in order to guarantee an effective treatment as well as to prevent damage to healthy tissue. The smart sensors for this monitoring must be radiation hard, able to handle the high rates in the beam and display it accurately.

High Voltage Monolithic Active Pixel Sensors (HV-MAPS) are a new promising smart sensor technology for particle detection. HV-MAPS collect the signal charge in the sensor by drift and not by diffusion. Charge collection by drift is fast and allows for better time resolution in comparison to standard MAPS using mainly diffusion. The achieved time resolution of HV-MAPS is less than 10 ns. Furthermore, the HV-MAPS technology enables the development of robust, thin and cost-efficient sensors. With HV-MAPS it is possible to realise a fill factor of 100% and high efficiency. The developed HV-MAPS are realised as application specific integrated circuits (ASICs) in a standard 180 nm HV-CMOS technology. This enables the implementation of complex circuits in CMOS logic.

The focus of the thesis is to investigate the suitability of HV-MAPS sensors for tracking detectors and beam monitoring and to develop sensor chips for these applications. Two HV-MAPS sensor families have been developed for two different applications. One is a large sensor specifically for particle tracking (MuPix) while the other is a radiation hard sensor that can handle high rates and is therefore suitable as a beam monitor (HitPix).

The Mu3e experiment is a particle physics experiment at the Paul Scherrer Institute in Switzerland that searches for the lepton flavour violating decay of  $\mu^+ \to e^+e^-e^+$ . A new, highly sensitive detector system is being built for the Mu3e experiment. The requirements for the Mu3e tracking detector are challenging: the sensors for the tracking detector have to be thinned to 50 µm to reduce multiple scattering and the time resolution has to be better than 20 ns. In addition, a high efficiency with 100 % fill factor is required. The developed full reticle size tracking sensor MuPix meets these requirements of Mu3e with an efficiency of more than 99 % and a time resolution better than 10 ns. The designs described in this thesis are the final designs that will be used for the upcoming final submission of MuPix, the final sensor for detector construction.

The Heidelberg Ion Beam Therapy Centre (HIT) is a centre for tumour treatment with particle therapy. A beam monitor is needed to guarantee safe and effective treatments.

The sensors are placed directly in the beam, meaning that they must be radiation hard and able to cope with the high rates in the beam focus. With the HitPix, a new sensor family was developed from scratch which will be used to investigate whether HV-MAPS implemented in HV-CMOS can meet the necessary requirements for beam monitoring. The HitPix was successfully put into operation and tested in several beam tests.

With the developed sensor chips, this thesis makes an important contribution to the application and further development of HV-CMOS pixel sensors for the field of medical and particle physics.

#### Outline of the thesis

This work focuses on the development of integrated circuits and smart sensors (HV-MAPS) for particle detection in physics experiments in the field of tracking detectors and in particle therapy in the context of beam monitoring. The work is divided into four parts. It starts with the introduction, the second part focuses on the development of integrated circuits for HV-MAPS, while in the third part, the chip development and characterisation is presented. The last part summarises and concludes the thesis.

The first part gives an introduction to the thesis. Firstly, the motivation, outline and the author's contributions are presented (chapter 1), followed by an introduction to the physics of semiconductor sensors (chapter 2) and to sensors for particle detection and tracking (chapter 3). Two different applications of HV-MAPS as sensors for particle detection are presented: Mu3e's tracking detector and a beam monitoring sensor in the context of particle therapy at HIT (chapter 4).

The second part focuses on the development of integrated circuits for HV-MAPS carried out in the scope of this thesis. The two main circuits for signal generation are presented, starting with the amplifier (chapter 5) followed by the comparator (chapter 6). Then a special library for minimising the leakage current caused by radiation is presented (chapter 7). The last chapter of section 2 is dedicated to the explanation of a counter and adder for beam monitoring and handling of high rates (chapter 8).

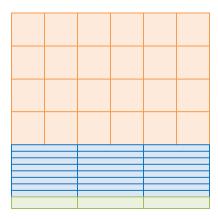

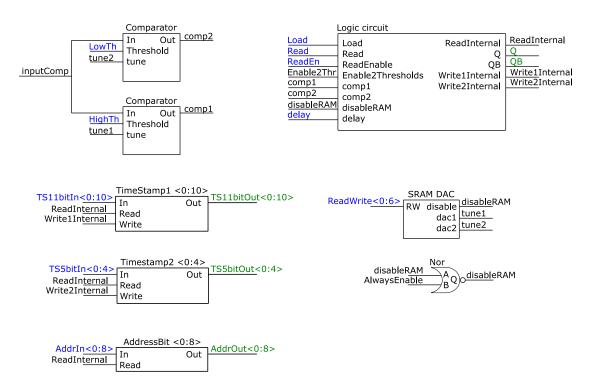

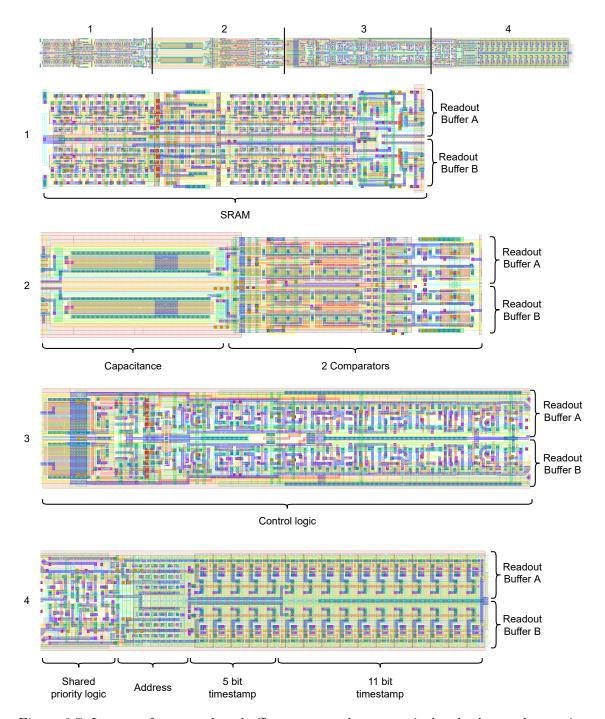

The third part describes the development of smart sensor chips and their characterisation: the MuPix and the HitPix, which the author conducted as part of this work. The design of the MuPix with its readout architecture and various measurements is presented (chapter 9). Next, the architecture of the HitPix and its characterisation in laboratory and beam tests is explained (chapter 10).

In the fourth part, the entire work is summarised and a brief outlook is given.

#### Contributions from the author

The development of several smart sensors for particle detection conducted in this work is an extensive task and is partly based on existing developments. The characterisations,

in-beam measurements and data analyses involves contribution from many people. The structure of the report of the author's contributions follows the structure of the thesis.

The charge sensitive amplifier used in the designed sensors is relying on the charge sensitive amplifiers developed by the working group for many years. Its behaviour was verified by the author with simulations. The comparator is based on a standard design. The transistor sizes were optimised by the author and the circuit was transferred into a radiation hard design with closed transistors for the HitPix project. The 180 nm HV-CMOS radiation hard library for minimal leakage currents has been developed entirely by the author. It is the first library within the designer group with a focus on minimal leakage current. The presented counter is based on the ripple counter principle and was realised by the author in the 180 nm HV-CMOS process using the library she designed. The adder was implemented by the author in the 180 nm HV-CMOS process.

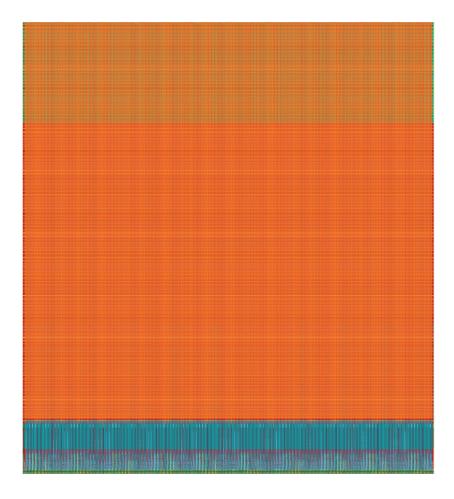

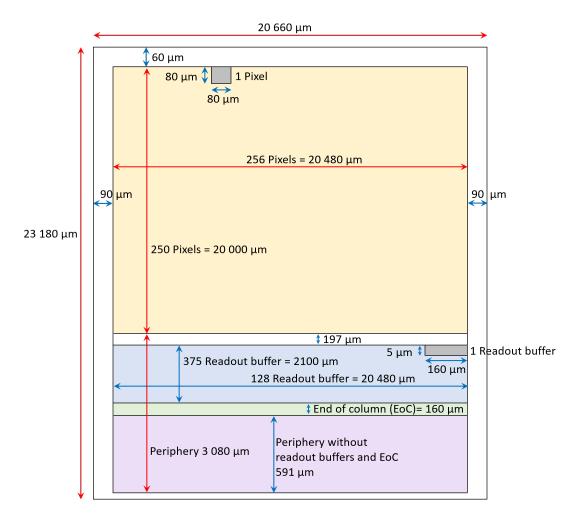

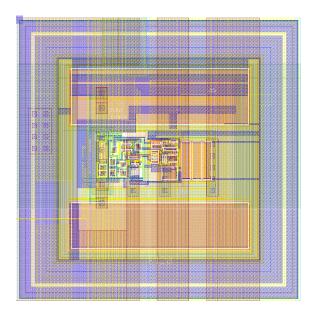

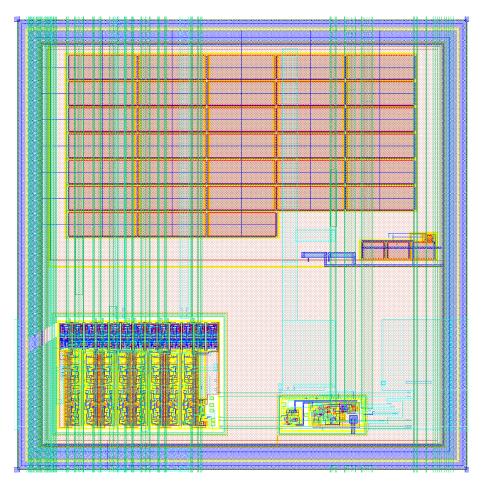

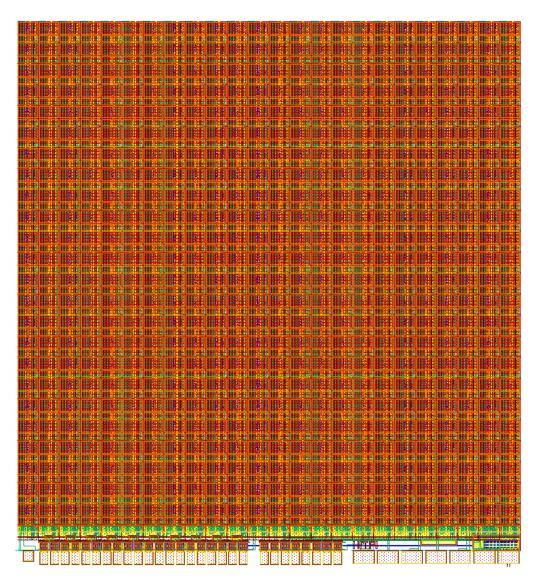

Before this work began, there were already small prototypes of the MuPix, up to the MuPix7. The MuPix8 is the first larger prototype (8 mm × 19.5 mm). The author started to work on the readout buffers in a column-drain architecture already during her master thesis, and continued working on this chip in the frame of this work. The author designed the pixel and readout buffer matrices, the top level analogue design and parts of the top level digital design of the MuPix9. The MuPix10 is the first full-size MuPix ASIC (20.66 mm × 23.18 mm). Here the author further developed the readout buffer and all its sub-circuits. The developed readout buffer is the design for the final MuPix. The entire readout buffer matrix has an optimised layout to minimise space requirements. In addition, the author has carried out simulations of the individual parts, at column level and at matrix level of the MuPix10 to verify the design.

The author performed the threshold tuning measurements of the MuPix8 and their analysis with the support of a group member from the Karlsruhe Institute of Technology (KIT). The adapter boards for the existing GECCO system for the MuPix9 and MuPix10 were designed by the author. She also modified the firmware and software of the GECCO system for these two chips with a developer of the GECCO system.

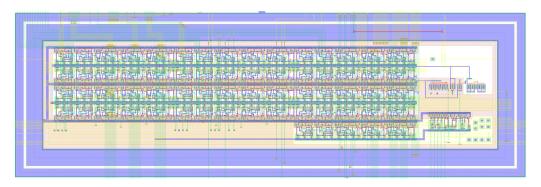

HitPix, HitPixISO and HitPix2 are completely developed and implemented by the author herself. They are not based on predecessor sensor chips. The author developed the HitPix, HitPixISO and HitPix2 architectures. She designed the pixels including amplifier, comparator, in-pixel counter and adder. She developed the row control and the readout shift register to realise an address-based readout architecture. In addition, the author realised the complete top level design. Most of the circuits were designed using the radiation hard library developed by her.

An adapter board for the HitPix and its variants was designed by the author for the GECCO system. The firmware and software were adapted for the HitPix by the author and

a developer of the GECCO system. The measurements of the unirradiated and irradiated samples in the laboratory were carried out by the author. The testbeam measurements at the Heidelberg Ion Therapy Centre (HIT) were also carried out by the author together with two other members of the group from the KIT, who took care of the data transmission and beam settings. With the support of a KIT group member the data from the HitPix was analysed by the author.

## Chapter 2

## Physics of semiconductor sensors

The smart sensors developed and later presented in this thesis are HV-CMOS sensors. They are based on transistors implemented on silicon wafers. In this chapter, the special properties of a semiconductor, the structure and the characteristics of MOSFET transistors are presented. Then the types of noise are introduced and the radiation damage in CMOS transistors is described.

#### 2.1 Basics of semiconductors

The ASICs developed are based on silicon and MOSFET transistors. To understand how the ASICs work, it is first necessary to have a clear comprehension of the properties of silicon as a semiconductor and how MOSFET transistors work. The two subsections first explain the different types of semiconductors and then the pn-junction.

#### 2.1.1 Different types of semiconductors

The different types of semiconductors are presented in this section with focus on silicon. Silicon is the most often used semiconductor [1] mainly for consumer electronics [2]. This leads to a high availability and a low price.

In the periodic table of elements, silicon is located in the fourth main group due its four valence electrons, see figure 2.1.

| III | IV | V  |

|-----|----|----|

| В   | С  | N  |

| Al  | Si | Р  |

| Ga  | Ge | As |

Figure 2.1: A section of the fourth group of the chemical periodic system of elements to show the position of silicon. For doping elements from the neighbouring groups like boron or arsenic are used.

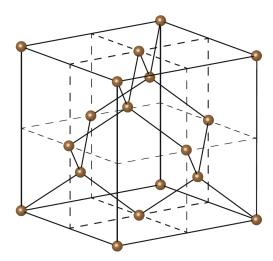

The silicon atoms are arranged in a diamond cubic latter structure, see figure 2.2. The atoms are connected by covalent bonds. Each valence electron is shared with another silicon atom, so each atom is connected with four covalent bonds to four other atoms. Because all the valence electrons are involved in these bonds, pure silicon has a low conductivity [3].

The allowed states of an electron in solid state materials, like in a silicon crystal, for a time-independent potential are described by the time-independent Schrödinger equation:

$$\left(-\frac{\hbar^2}{2m}\nabla^2 + V(\vec{r})\right)\Psi(\vec{r}) = E\Psi(\vec{r})$$

(2.1)

$\hbar = \frac{h}{2\pi}$  is the reduced Planck constant.

$V(\vec{r})$  is the periodic potential by the crystal lattice containing the link to the crystal lattice defining  $\vec{R}$ :

Figure 2.2: The silicon atoms are arranged in a diamond lattice repeating a pattern including 8 atoms. (From [4])

$$V(\vec{r}) = V(\vec{r} + \vec{R}) \tag{2.2}$$

In case of periodic potentials the time-independent Schrödinger equation is solved by Blochwaves [5]

$$\Psi(\vec{r}) = e^{i\vec{k}\vec{r}} u_{\vec{k}}(\vec{r}) \tag{2.3}$$

where

$$u_{\vec{k}}(\vec{r}) = u_{\vec{k}}(\vec{r} + \vec{R}) \tag{2.4}$$

describes the periodicity of the lattice.

This leads to possible energy states for electrons. The quasi-continuous electron states are called band. Two bands have a particularly important significance as they define the electrical conductivity of insulators, semiconductors and conductors: the band with the lowest energy not fully occupied in ground state (conduction band) and the next lower band (valence band). Electrons in the valence band are not available for current flow, whereas electrons in the conduction band (and holes in the valence band) are free to move and lead to current flow if an electric field is applied. At  $T=0\,\mathrm{K}$  the fermi energy is defined in the middle between the occupied states and the unoccupied states.

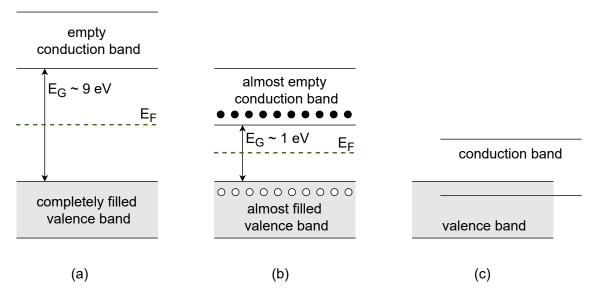

The different energy band structures for insulator, semiconductor and metal are shown in figure 2.3. In an insulator and a semiconductor, the valence band is separated from the

Figure 2.3: Schematic energy bands for insulator (a), semiconductor (b) and metal (c) and the fermi energy  $E_F$ . In an insulator (a) and a semiconductor (b), the valence band is separated from the conduction band by the so-called band gap. In an insulator (a) the conduction band is empty and the valence band is filled, whereas in a semiconductor (b) they are almost empty and almost full. The band gap is smaller in semiconductors than in insulators. In a conductor (c) the two bands overlap. (Modified from [4] and [6])

conduction band by the so called band gap (figure 2.3 (a)). For insulators and semiconductors the fermi level is located inside the band gap. The band gap of insulators is larger than  $4\,\mathrm{eV}$ , for semiconductors less than  $4\,\mathrm{eV}$  (figure 2.3 (b)). For silicon the band gap is  $1.12\,\mathrm{eV}$  at room temperature and for silicon dioxide  $9\,\mathrm{eV}$ . With increasing pressure and temperature, the band gap of semiconductors is decreasing. At  $T=0\,\mathrm{K}$  in a semiconductor all electrons are in the valence band and none in the conduction band. In the case of semiconductors, small additional energy (for example thermal energy or external fields) make it possible to bring electrons from the valence band to the conduction band where they can contribute to a current flow.

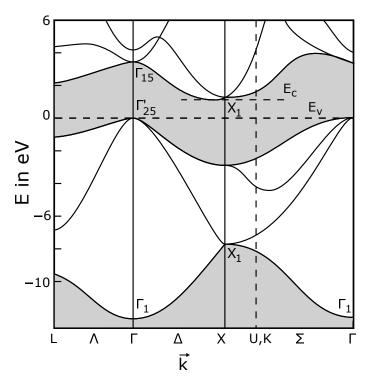

The band structure of semiconductors leads to a division into direct and indirect semiconductors. Figure 2.4 shows the simplified band structure of silicon as an example of an indirect semiconductor and gallium arsenide as an example of a direct semiconductor. The indices on the x-axes are the miller indices which describe the crystal orientation. In the case of a direct semiconductor, the maximum of the valence band and the minimum of the conduction band are at the same reciprocal lattice vector (miller indices). The needed band gap energy  $E_G$  to bring an electron from the valence band with the energy  $E_V$  to the conduction band with  $E_C$  is

$$E_G = E_C - E_V. (2.5)$$

Figure 2.4: Simplified band structures of silicon (indirect semiconductor) on the left and gallium arsenide (direct semiconductor) on the right. Silicon is an indirect semiconductor because the maximum of the valence band and the minimum of the conduction band are not at the same Miller indices. In direct semiconductors such as gallium arsenide, they are at the same Miller indices. (From [4] after [8])

In an indirect semiconductor the maximum of the valence band and the minimum of the conductive band are not at the same miller indices, the band gap is indirect. Because of the indirect band gap it is not enough to bring an electron from the valence to the conductive band with the band gap energy  $E_G$ .

The detailed band structure of silicon is shown in figrue 2.5. The band gap is approximately 1.12 eV.

To move an electron from the valence band up to the conduction band, more energy is necessary or an additional impulse has to be transferred to the crystal lattice via a phonon. In the case of a direct semiconductor the maximum of the valence and the minimum of the conductive band are directly above each other, leading to a direct band gap [4]. Direct semiconductors are more efficient for light generation and absorption, therefore gallium arsenide is often used for LEDs [7].

Pure semiconductors (intrinsic semiconductors) have a high resistivity at room temperature, because thermal excitation only generates a small amount of free electrons and holes. The conductivity of intrinsic silicon is described by:

$$\sigma_i = n_i e(\mu_e + \mu_h) \simeq 2.8 \cdot 10^{-4} (\Omega \text{m})^{-1}$$

(2.6)

with the intrinsic charge carrier density  $n_i$ , the elementary charge e and the charge carrier mobility of the electrons  $\mu_e$  and holes  $\mu_h$ . The given approximate value is at room temperature. To be able to put the conductivity of silicon into perspective, the conductivity of copper is 12 orders of magnitude larger with:  $\sigma_{Cu} \simeq 10^8 (\Omega \text{m})^{-1}$  [4].

Figure 2.5: Detailed band structure of silicon. The minimum of the valence band  $E_V$  and conduction band  $E_C$  are not at the same miller indice, therefore silicon is an indifferent semiconductor. (From [9] after [10])

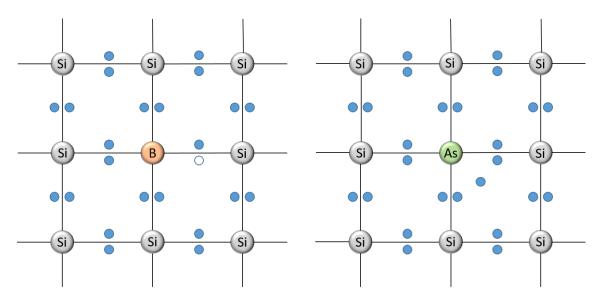

The resistivity of a semiconductor can be manipulated with a process called doping: impurity atoms are built into the crystal structure, the semiconductor is now called extrinsic. In the case of silicon typically elements of the III or the V group of the periodic system of elements are used. Elements of the III group have one electron less, the ones of the group V one electron more than silicon.

With elements from the III group, like boron, a vacancy in a covalent bond is added, see figure 2.6 (a). Simplified, this adds a mobile hole (electron acceptor) to the valence band. Impurity addition of electron acceptors to a semiconductor is called p-doping. In a p-doped (also p-type) semiconductor holes are majority carriers and electrons minority carriers.

If, instead of atoms of the group III, atoms of the group V are used for doping, each atom brings an additional electron into the lattice. Now electrons are majority carriers and the holes are minority carriers, the semiconductor is called n-doped (n-type), see figure 2.6 (b) [11].

Doping changes the fermi level of semiconductors: with p-doping the fermi level is decreased, with n-doping increased.

Figure 2.6: Schematic of doped silicon lattice: on the right p-doping with boron generating a hole and on the left n-doping with arsenic leading to an unpaired electron.

#### 2.1.2 PN-junction

An n- and a p-doped semiconductor in contact with each other, is called a pn-junction. This represents one of the simplest semiconductor devices: the diode. The behaviour of this interface is important to understand the characteristics of transistors in section 2.2. The n-doped and p-doped parts show a strong concentration gradient of charge carriers. This leads to a diffusion current  $i_{\text{diff}}$ , bringing electrons from the n-doped to the p-doped region and holes from the p-doped to the n-doped region [12]:

$$\vec{i}_{\text{diff}} = -eD\nabla n \tag{2.7}$$

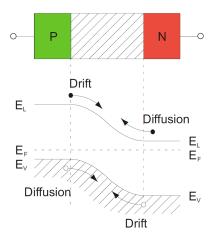

D is the diffusion constant, e the elementary charge and n the charge carrier density. At the interface, recombination of charge carriers leads to a zone without free charge carriers: the depletion zone. The fixed leftover ionized atoms in the n-doped and p-doped interface build a space charge region with an intrinsic electric field. The electric field leads to a drift of electrons and holes in the opposite direction of the diffusion. Figure 2.7 shows the drift and diffusion current directions of the charge carriers at a pn-junction.

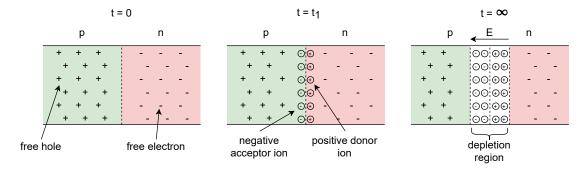

In figure 2.8 the evolution of the charge concentrations and the forming of the depletion region is shown. At time t = 0 the p- and n-doped semiconductors build a pn-junction. Then at  $t = t_1$  the free charge carriers move, due to diffusion, and recombine with each other in the area around the doping transition forming the depletion region. Here, the immobile ionized atoms form an electric field. At time  $t = \infty$  the pn-junction reaches equilibrium, the driving gradients of drift and diffusion currents compensate [3].

Figure 2.7: The directions of the drift and diffusion currents for electrons in the conduction band and holes in the valence band at a pn-interface. On the left, the semiconductor is p-doped and on the right n-doped. (From [4])

Figure 2.8: Evolution of the equilibrium of the pn-junction over time after a sudden contact. In the first figure, the two semiconductors form a pn-junction at  $t=t_1$ . The next figure shows at  $t=t_1$  the movement due to diffusion of the free charge carriers. Around the doping transition they recombine and create a depletion zone. The immobile ionised atoms form an electric field. At the time  $t=\infty$ , the pn-transition reaches its equilibrium. (After [3], modified)

In equilibrium, the space charge region depends only on the doping of both semiconductors. The charge density using the Schottky approximation is [4]:

$$\rho(x) = \begin{cases}

0 & \text{for } x \le -x_p \\

-eN_A & \text{for } -x_p < x \le 0 \\

+eN_D & \text{for } 0 < x \le x_n \\

0 & \text{for } -x_p < x

\end{cases} \tag{2.8}$$

The charge carrier amounts in the space charge region have to be the same for both parts of the junction:

$$N_A x_p = N_D x_n \tag{2.9}$$

Therefore the space charge region is larger in the lower doped side.

With the one-dimensional Maxwell equation for the electrical field and the boundary conditions in equations 2.1.2 and 2.1.2 the electrical field E can be calculated [4]:

$$E = \begin{cases} \frac{-eN_A}{\epsilon \epsilon_0} (x + x_p) & \text{for } -x_p < x < 0\\ \frac{+eN_D}{\epsilon \epsilon_0} (x - x_n) & \text{for } 0 < x < x_n \end{cases}$$

(2.10)

The maximum of the field is at x = 0 leading to

$$E_{max} = -\frac{eN_A}{\epsilon \epsilon_0} x_p = -\frac{eN_D}{\epsilon \epsilon_0} (-x_n)$$

(2.11)

The differences of the potentials  $\phi$  in the n- and p-doped area outside the space charge region lead to a voltage drop across the depletion region, the so called built-in voltage  $U_{bi}$ :

$$U_{bi} = \phi_p - \phi_n \tag{2.12}$$

With the intrinsic  $(E_f)$  and extrinsic  $(E_F)$  fermi energies the needed potentials are calculated:

$$E_f - E_F^p = -e\phi_p = kT \ln\left(\frac{N_A}{n_i}\right) \tag{2.13}$$

$$E_F^n - E_f = -e\phi_n = kT \ln\left(\frac{N_D}{n_i}\right) \tag{2.14}$$

This leads to:

$$U_{bi} = kT \ln \left( \frac{N_A N_D}{n_i^2} \right) \tag{2.15}$$

For silicon  $U_{bi}$  is typically between 0.6 V and 0.8 V [4]. The detailed derivation of the potentials and energies can be found in [4] and [8].

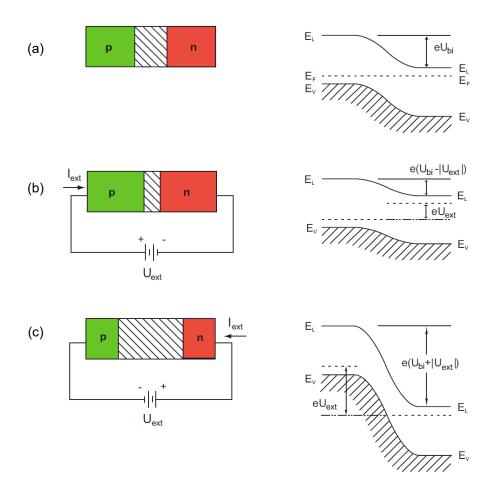

So far, the pn-junction has been considered without external voltage. Now the description is extended by an external voltage  $U_{ext}$ . The external voltage changes the width of the depletion zone. In figure 2.9 the two different cases and their effect on the depletion region are shown. If an external voltage is applied with higher potential to the p-doped and negative potential to the n-doped region, it is called forward bias, if it is applied in the other direction it is called reverse bias.

#### Forward bias

- $U_{bi}$  decreases with  $U_{ext}$ :  $U_{bi, \text{ reverse bias}} = U_{bi} |U_{ext}|$ .

- The drift current is reduced compared to the diffusion current.

- In comparison to the equilibrium more electrons diffuse from the n- to the p-part while more holes diffuse from the p- to the n-part.

- The depletion region is shortened.

#### Reverse bias

- $U_{bi}$  increases:  $U_{bi, \text{ reverse bias}} = U_{bi} + |U_{ext}|$ .

- The diffusion current is reduced compared to the drift current.

- The depletion region gets wider.

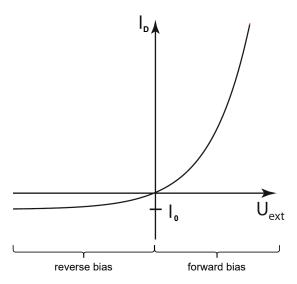

The current of a diode as a function of the applied voltage is described with the Shockley equation:

$$I_D = I_0(e^{\frac{eU_{ext}}{kT}} - 1) (2.16)$$

The ideal I/V characteristic of a diode is shown in figure 2.10. For the forward bias the current increases exponentially while for the reverse bias the current is approximately  $I = I_0$ , because the exponential part of the Shockley equation is negligible [8].

Figure 2.9: Diode without external voltage (top), with external voltage as forward bias (middle) and as reverse bias (bottom). Without external voltage, the diode is in equilibrium. If an external voltage is applied in the forward direction (higher potential for the p-doped region and negative potential for the n-doped region), the junction region shrinks:  $U_{bi}$  decreases and the drift current is reduced. With reverse bias, the junction region becomes wider because  $U_{bi}$  increases and the diffusion current is reduced. (From [4])

Figure 2.10: Ideal I/V characteristic of a diode. For the forward bias the current increases exponentially while for the reverse bias the current is approximately  $I = I_0$ .

### 2.2 Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)

The basic elements for sensor electronics are transistors. They are used for signal amplification and readout electronics. For the HV-CMOS sensors in this thesis, metal-oxide-semiconductor field-effect transistors (MOSFET) are used exclusively. The next sections present their structure and characteristics.

#### 2.2.1 Structure and working principle of MOSFETs

A MOSFET has four different pins: source, drain, gate and bulk. The basic idea of a MOSFET is that with a control voltage between gate and source, the conductivity between drain and source can be changed. Therefore, the MOSFET is often called a voltage-controlled resistor or a voltage-controlled current source. MOSFETs consist of differently doped areas of silicon, silicon-oxide as an insulator and poly-silicon as a conductor [13]. Depending on the source and drain doping there is a distinction between n-channel (NMOS) and p-channel (PMOS) transistors. The bulk is the substrate contact.

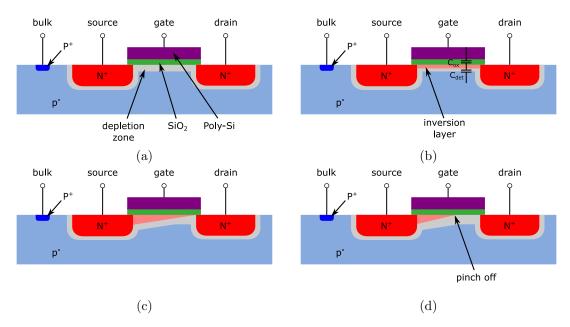

Figure 2.11 (a) shows the structure of an n-channel MOSFET. The source and drain are n-doped and placed in p-doped silicon substrate. For a p-channel MOSFET, the doping types are inverted. The poly-silicon gate is isolated from the substrate with a thin SiO<sub>2</sub> layer. The source-substrate and drain-substrate interfaces form two pn-junctions (i.e. diodes). In NMOS transistors the substrate potential has to be at a lower potential than source and drain, in which case the diodes are reverse biased.

Figure 2.11: Schematic structure of an NMOS transistor without applied voltages (a). In (b)  $U_{GS} > U_{Th}$  is applied, an inversion layer is formed and the transistor is operated in linear mode. (c) shows the transition between linear mode to saturation and in (d) the transistor is operated in saturation. (Modified from [6] after [14])

When the control voltage between gate and source is 0 V, no current can flow between source and drain. Without applied voltages a depletion zone is formed around the source and drain regions. The gate has a metal-oxide-semiconductor (MOS) structure, which also leads to a depletion zone below the gate. Instead of metal, poly-silicon is often used, due to manufacturing reasons, with the same behaviour [13] [11].

If a voltage higher than the threshold voltage  $U_{Th}$  is applied between gate and source ( $U_{GS}$ ), a conduction channel is created between drain and source. In this case, the majority carriers are no longer available for recombination. This leads to an accumulation of minority carriers in the substrate under the gate, the inversion layer. In the case of a p-doped substrate (NMOS transistor), the inversion layer is an n-conduction channel connecting source and drain, see figure 2.11 (b). In this operation mode, the drain-source current  $I_{DS}$  increases linearly as a function of  $U_{DS}$  and the transistor behaves like a voltage-controlled resistor [13] [14] [6].

When  $U_{DS}$  reaches the value  $U_{DS, sat}$ , free electrons migrate to the source, narrowing the channel near the drain (channel pinch-off) (see figure 2.11c). The narrowed channel limits the increase in current. At higher  $U_{DS}$ , the pinch-off point shifts towards source (see figure 2.11d). In this mode the current does not change with increasing  $U_{DS}$ . The drain-source current depends on  $U_{GS}$ , this operation mode is called saturation and the transistor behaves like a voltage-controlled current source [13] [14] [6].

#### 2.2.2 IV characteristics

After explaining the structure and the basic functionality of a transistor, the IV characteristic is now derived for an NMOS transistor. The derivation follows the example of [3].

The charge density in the channel near the source is described with the gate capacitance per unit area  $C_{Ox}$ , the width of the transistor W and the voltage difference between gate and channel. Because no mobile charge carriers exist in the channel for  $V_{GS} < V_{Th}$ , the charge density can be described by:

$$Q = WC_{Ox}(V_{GS} - V_{Th}) (2.17)$$

Because the charge density varies over the channel due to the variation of the voltage between gate and channel, equation 2.17 has to be modified to

$$Q(x) = WC_{Ox}(V_{GS} - V(x) - V_{Th})$$

(2.18)

V(x) can take values between 0 and  $V_D$  if the channel is not pinched off. The current is given by the passing charge per unit length and its velocity

$$I = Q \cdot v. \tag{2.19}$$

with

$$v = -\mu_n E = +\mu_n \frac{dV(X)}{dx} \tag{2.20}$$

Now equations 2.18 and 2.20 are inserted in 2.19:

$$I_D = WC_{Ox}(V_{GS} - V(x) - V_{Th})\mu_n \frac{dV(x)}{dx}$$

(2.21)

x describes the channel length, therefore  $I_D$  has to be integrated over the channel:

$$\int_{x=0}^{x=L} I_D dx = \int_{V(x)=0}^{V(x)=V_{DS}} \mu_n W C_{Ox} (V_{GS} - V(x) - V_{Th}) dV$$

(2.22)

$$I_D = \mu_n C_{Ox} \frac{W}{L} \left[ (V_{GS} - V_{Th}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.23)

For a constant  $V_{GS}$   $I_D$  is rising until the maximum  $I_{D, Sat}$  at  $V_{DS} = V_{GS} - V_{Th}$ , here the current saturates due to the channel pinch off:

$$I_{D, Sat} = \frac{1}{2} \mu_n C_{Ox} \frac{W}{L} (V_{GS} - V_{Th})^2$$

(2.24)

In the case  $V_{DS} \ll 2(V_{GS} - V_{Th})$ , equation 2.23 can be simplified to:

$$I_D \approx \mu_n C_{Ox} \frac{W}{L} (V_{GS} - V_{Th}) V_{DS}$$

(2.25)

Here, for a constant  $V_{GS}$   $I_D$  as a function of  $V_{DS}$  is linear corresponding to the resistor-like behaviour of the transistor. The equivalent resistance is therefore:

$$R = \frac{V_{DS}}{I_D} \approx \frac{1}{\mu_n C_{Ox} \frac{W}{L} (V_{GS} - V_{Th})}$$

(2.26)

The value of the resistance can be controlled by  $V_{GS}$ , according to equation 2.26. In the case  $V_{GS} = V_{Th}$ , R becomes infinite, the transistor is turned off. Therefore, the transistor can be seen as a voltage-controlled switch.

After the saturation point the channel shrinks (pinch off) as explained in section 2.2.1. After  $V_{DS} = V_{GS} - V_{Th}$  further increase of  $V_{DS}$  shifts the pinch off point towards the source contact. Therefore, the integral borders in equation 2.22 have to be changed to contain only the channel:

$$\int_{x=0}^{x=L_P} I_D dx = \int_{V(x)=0}^{V(x)=V_{GS}-V_{Th}} \mu_n W C_{Ox} (V_{GS} - V(x) - V_{Th}) dV$$

(2.27)

This leads to an equation independent of  $V_{DS}$

$$I_D = \mu_n C_{Ox} \frac{W}{L_P} \left[ (V_{GS} - V_{Th})^2 \right]$$

(2.28)

This is under the assumption that  $L_P \approx L$  is identical to the saturation current from equation 2.24. So for  $V_{DS} > V_{GS} - V_{Th}$  the current saturates and the transistor behaves like a current source controlled by  $V_{GS}$ .

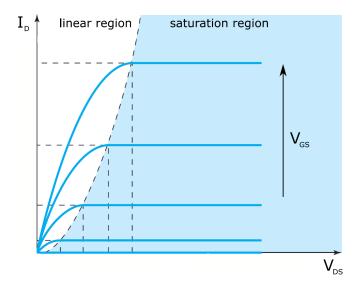

Figure 2.12 shows  $I_D$  as a function of  $U_{DS}$  for different  $U_{GS}$  values. In the first half (white background), the transistor behaves like a voltage controlled resistor (linear region). Later the transistor is in saturation (blue background).  $I_{DS}$  stops rising and the transistor behaves like a voltage-controlled current source.

In this analysis it is assumed that the current remains constant in the saturation range. However, this is an approximation. Actually the current increases slightly, inversely proportional to the length of the transistor. This behaviour is described by the channel length modulation and a correction factor  $\lambda$  is added to the equation 2.28. For more information on channel length modelling, see [16] [11] [15].

Figure 2.12: IV characteristics of a MOSFET for different  $U_{GS}$  values, from bottom to top the  $U_{GS}$  voltage increases. (Modified from [15])

#### 2.3 Noise types

Statistical fluctuations in all circuits cause variations in voltages or currents, these are called noise [4]. First, the current I through a sample with a length l is considered. Assuming n carriers with a defined charge of e and a velocity v are moving through the sample, the introduced current is

$$I = \frac{nev}{l} \tag{2.29}$$

The fluctuations of this current are given by

$$\langle di \rangle^2 = \left(\frac{ne}{l} \langle dv \rangle\right)^2 + \left(\frac{ev}{l} \langle dn \rangle\right)^2 \tag{2.30}$$

It can be seen that there are two mechanisms that contribute to the total noise. The fluctuations of velocity are leading to the so called thermal noise (also called Johnson's noise) while the number fluctuations are the reason for shot noise and flicker noise (also called 1/f noise) [17].

#### Thermal noise

The charge carriers move within a conductor and semiconductor due to their kinetic or thermal energy. This is called Brownian movement. Considering the thermal noise of a resistor, the expected values are given by the Nyquist formulas with the Boltzmann constant  $k_B$ :

$$d\langle i^2\rangle_{thermal} = \frac{1}{R} \frac{dP_n}{df} df = \frac{1}{R} 4k_B T df$$

(2.31)

$$d\langle u^2\rangle_{thermal} = R\frac{dP_n}{df}df = R4k_BTdf$$

(2.32)

From these formulas it follows that the noise is not dependent on the current flowing through the resistor. The thermal noise is dependent on the bandwidth, the absolute temperature and the resistance value. The frequency spectrum of thermal noise is white (constant power spectral density) [18] [4].

The thermal noise has to be taken into account, especially for the channel of the input transistor of the charge sensitive amplifier. This channel behaves like a resistor with nonuniform resistance. The thermal noise leads to current fluctuation of the current flowing through the resistor.

#### Shot noise

Shot noise occurs during the transport of charge carriers across a potential barrier, for example, at the pn-junction. The spectral noise current density is described by the Schottky relation [4]

$$d\langle i^2\rangle_{shot} = 2eI_0 df \tag{2.33}$$

with the electronic charge e and the average current  $I_0$ . The shot noise is directly proportional to the current [18] [4].

#### Flicker noise

The Flicker noise is, unlike the noise types mentioned before, not white. The noise spectrum becomes "non-white" or non-uniform whenever the fluctuations are not purely random in time.

In transistors, charge carriers can be trapped in the gate insulator. This leads to fluctuations in the transistor current. The number of charge carriers and their mobility are influenced by the oxide/bulk charge. This current varies with the trapping of the charge carriers. Charge capture is described by two time constants, the capture time and the emission time [16].

A pure 1/f distribution of the spectral power density occurs with an infinite number of uniformly distributed time constants. Already 3 trapping processes with different time constants can result in a 1/f spectrum for a wide range [17] [4]. In the case of an amplifier the charge trapping in the gate insulator causes fluctuation of the oxide and bulk charge. The spectral density of this trapping process has the typical dependency of 1/f [17] [4].

#### 2.4 Radiation damage

For many years the radiation hardness of CMOS transistors has been studied due to many application fields of semiconductor devices in radiation environments, such as in space or high energy physics [19] [20].

Radiation damage in metal oxide semiconductors (MOS) changes the basic electro-physical characteristics of transistors [21]. The damages can be separated into two different groups: bulk damage and surface damage. The bulk damage influences the signal generation in the silicon sensor part. The surface damage, on the other hand, influences the behaviour of the CMOS electronics.

#### Bulk damage

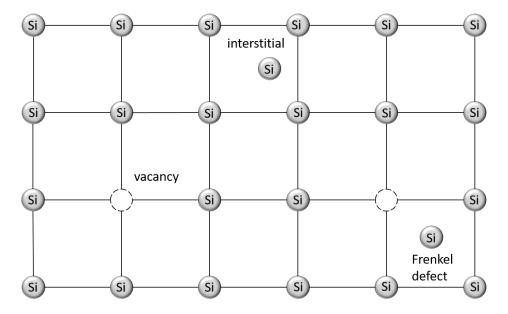

Bulk damage is caused by defects in the crystal structure of silicon due to non-ionizing energy loss of particles [6]. The transferred energy from particles can be large enough to lead to point and cluster defects by removing atoms from the lattice leaving a vacancy. The removed atom can stop somewhere else in the lattice and is called interstitial. In the case that vacancy and interstitial are locally close they form a so called Frenkel defect (see figure 2.13).

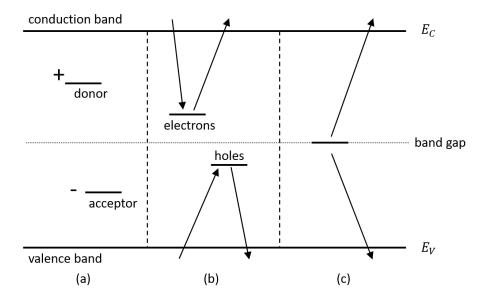

These defects lead to macroscopic effects in the band structure as shown in figure 2.14:

#### • Donor and acceptor generation

States close to the conduction and valance band change the effective doping concentration. They lead to a change of the depletion zone and can lead to type inversion of n-type to p-type substrate. The depletion voltage can drop first and then start to rise later with higher radiation [22].

#### • Charge trapping

Charge generated by particles can be trapped by defects leading to a lower signal due to less available charge. The trapping reduces the charge collection efficiency of the sensor.

#### • Increase of leakage current

If the states are close to the middle of the band structure, they lead to a higher leakage current due to more generation centres. More leakage current leads to more shot noise. If the sensor is cooled during operation, the leakage current is smaller.

Parts of these damages can heal over time. This is called annealing. Most likely Frenkel effects "repair themselves" with time. The annealing effect accelerates at moderately higher temperatures. Therefore, the irradiated sensors measured in section 10.3.2 were cooled down to -40°C to prevent annealing processes [22].

Figure 2.13: Defects in the silicon lattice: vacancy if an atom is removed, interstitial where the removed atom rests. In the case that vacancy and interstitial are locally close, they form a Frenkel defect.

Figure 2.14: Additional states in the band structure of silicon due to lattice defects. There are 3 different types: donor and acceptor generation (a), charge trapping (b) and increase of leakage current (c). First the donor and acceptor generation (a), these are states close to the conduction and valance band. They change the effective doping concentration and lead to a change of the depletion zone. Charge generated by particles can be trapped (b) by defects leading to a lower signal due to less available charge. If the states are close to the middle of the band structure (c), they lead to a higher leakage current due to more generation centres. (After [4] [22])

#### Surface damage

Surface damage due to ionizing damage changes the electrical behaviour of CMOS electronics. Electron hole pairs generated by the charged particles in the silicon oxide are quite immobile. Nevertheless, the electrons are more mobile than the holes and can sometimes leave the oxide through the gate contact. But the holes will most likely remain in the oxide, leading to a positive charge accumulation there.

In the past the total dose tolerance was limited by the radiation damage in the gate oxide [19]. In the deep sub-micron technologies, like the used 180 nm HV-CMOS process, the gate oxide is thinner and the tunnelling gets easier, therefore these technologies are inherently more radiation tolerant [19]. Nevertheless, special layouts for NMOS transistors have to be used to reduce the leakage current flow.

Trapping centers are built and space charge is accumulated in the silicon oxide leading to a shift in threshold voltages [21] [23]. Furthermore, the mobility of charge carriers in the near surface semiconductor region is decreasing [21]. The charge trapped in the oxide leads to a negative threshold voltage shift for NMOS and PMOS transistors [24] [25] [23]. The charge trapped in the interface shifts the threshold voltage for NMOS in a negative direction and a positive one for PMOS [24] [25] [23]. The threshold shift due to irradiation depends on the thickness of the oxide [23].

In the p-well and p-substrate underneath the field oxide an inversion layer is generated. This layer is formed by the accumulation of positive charge in the silicon oxide after irradiation. The inversion layer allows for a leakage between source and drain and also for inter transistor leakage between neighbouring  $n^+$  implants. The leakage between source and drain can be avoided by forcing all source to drain current to flow only underneath the gate oxide by using a closed gate. With the closed gate, no current path is available underneath the field oxide or along the edges of the active area [26] [20]. The inter transistor leakage between  $n^+$  implants, also caused by the inversion layer, can be prevented by the use of separating guard rings. These isolate the  $n^+$  implants wherever it is necessary [26].

An enclosed transistor design together with guard rings where needed are a common and successful approach to reduce the leakage current [23] [20] [26] [27] [19]. Different papers have studied the radiation effects on enclosed NMOS transistors in different commercial CMOS technologies, like in standard commercial  $0.6 \,\mu m$  [23],  $0.5 \,\mu m$  [26],  $0.35 \,\mu m$  CMOS [20] or  $0.25 \,\mu m$  [19] CMOS processes.

The calculation of (W/L) for enclosed transistors, as used for the radiation hard library, is explained in detail in [19]. The enclosed transistors have a non-symmetrical geometry because the source and drain contacts can be chosen inside and outside or the other way around. This leads to an asymmetric behaviour of the device [19].

## Chapter 3

## Sensors for particle detection and tracking

First, the differences between hybrid and monolithic pixel sensors are shown. Then monolithic active sensors (MAPS) are explained, followed by monolithic active pixel sensors (HV-MAPS). The smart sensors developed in this thesis are HV-MAPS.

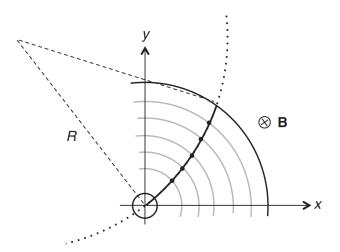

Figure 3.1: The tracking detector consists of several layers, charged particles leave bent trajectories in the detector due to the magnetic field. (From [28])

In many particle physics experiments particle beams are brought to collision at high energies. Other experiments, like Mu3e, collide particles with fixed targets. In both cases the elapsing particle reactions are observed. Many particles decay before they reach the detector. In this case the decay products with sufficient lifetime are observed. In the analysis of the detector's information, the original interaction process with the following decay processes are reconstructed. For this, the involved particle types, their energy and their origin are necessary.

The task of the so-called tracking detectors is to resolve the location and time of the particle hit as precisely as reasonable for the following reconstruction. By this, the particle trajectories and their momenta can be calculated. To get the necessary information, most tracking detectors have a similar structure: several cylindrically arranged layers of particle tracking sensors are built around the interaction point, with the beam axis as symmetry line. A magnetic field parallel to the beam axis leads to bended trajectories of charged particles, see figure 3.1. The magnetic field is usually provided by a solenoid magnet around the detector. On the path of a particle through the tracking detector, it is scattered at the detector itself. To reach a high spatial resolution, the deflection should be small which leads to the requirement for minimal material budget.

#### 3.1 Hybrid and monolithic pixel sensors

The goal of pixel sensors is a two dimensional information on the particle-sensor interaction point. This is achieved by a segmentation of the sensor in two directions leading to a pixel matrix [17].

There are two major approaches to realising this: hybrid and monolithic pixel sensors.

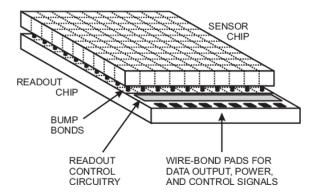

Figure 3.2: A hybrid pixel detector consists of a sensor and a readout chip connected by bump bonds. (From [17])

Hybrid pixel sensors consist of two application-specific integrated circuits (ASIC): the sensor and the readout ASIC (front-end chip). Sensor and readout ASIC are connected in every pixel by bump bonds (figure 3.2) [4]. Particles flying through the sensor generate charge. The signal processing is then done on the readout ASIC. As the pixel has to match the corresponding part of the readout ASIC, the pixel size is limited by the bump bond size. An advantage of hybrid pixel sensors is that both chips can be developed individually and both parts do not need to have the same development cycle. For example the sensor ASIC can be used for several generations of readout ASICs. Also the sensor chips can be used with different front-end chips for different applications and for both ASICs different fabrication technologies can be used. A disadvantage is that the assembling of the connecting bonding is complex as well as time and cost intensive. Furthermore, the sensor ASIC can often not be produced in standard processes leading to an expensive fabrication that is only offered by a few manufacturers. Another disadvantage is the detector thickness due to two ASICs causing multiple scattering [29].

The other common approach is monolithic pixel sensors. In the case of implementations with electronics inside the pixels, these sensors are referred to as monolithic active pixel sensors (MAPS). Here, the sensor and readout are realised on one chip: signal generation, amplification and signal processing are done on the same die.

#### 3.2 High Voltage Monolithic Active Pixel Sensors (HV-MAPS)

The idea of using commercial technologies to develop a monolithic active pixel chip was published first in 1989 [30]. In 2001, monolithic active pixel sensors produced in a standard CMOS technology (MAPS) were presented for charged particle tracking in [31]. In contrast to passive pixel sensors, in which the photo-diode used as the sensor is directly connected to the output line, in active pixel sensors the pixel itself contains an amplifier.

For the first prototype, the minimum ionising particle MOS active pixel (MIMOSA), a standard 0.6 µm CMOS technology was chosen. The used CMOS technology provides a twin-well implanted in a p-type epitaxial layer. A photo-diode already available in CMOS technology was chosen as sensor with the partially depleted thin epitaxial silicon layer as sensitive sensor volume. The charge collection in these MAPS is efficient and on the order of 100 ns [31].

At that time, CMOS sensors were already used for visible light detection, as the standard VLSI technology makes the sensors cheap. Furthermore, the concept is power-saving as the in-pixel are only active during readout and no clock signal has to be distributed. The pixels are easy accessible by addresses for readout. Another advantage is that complex circuits can be realised with CMOS to implement a variety of functionalities [31].

However, MAPS in CMOS technology are also interesting for particle tracking. For particle physics experiments, high efficiency and spatial resolution of detected minimum ionizing particles (MIPs) is necessary. Pixel sizes are usually between 10 and 20 times the minimum feature size of the fabrication process, which means that small pixels are possible. The substrate can be thinned down to a few tens of microns, so that multiple scattering is low. Another advantage is that sub-micron VLSI technologies are less sensitive to radiation damage. In addition, a signal-to-noise ratio of over 100 can be achieved. The n-well and the p-type epitaxial layer form the photo diode. As the charged particles pass through the diode, they generate electrons in the epitaxial layer that move to the n-well diode contact mainly by diffusion. A relativistic charged particle typically generates 80 pairs of electrons and holes per micrometre of silicon. The most important technology parameter for MAPS is therefore the thickness of the epitaxial layer, as this defines the number of electron-hole pairs generated. An epitaxial layer between 12 and 16 µm leads to about 1000 electron-hole pairs per MIP [31].

In 2006, a realisation of MAPS in a triple-well CMOS process was proposed by [32]. The triple-well process makes it possible to implement more complex signal processing circuits at pixel level and to increase the size of the charge-collecting electrode. The deep n-well available in the triple-well technology is used as sensor electrode and part of the readout electronics are placed in the same physical area. The chosen 0.13 µm technology has a thin oxide of about 2 nm, resulting in a high radiation tolerance [32].

The charge in MAPS is collected by diffusion causing a slow collection time of about 100 ns [4] [17] and small amplitudes [33]. To solve these problems, a MAPS using high voltage (HV-MAPS) realised with high voltage CMOS (HV-CMOS) technology was presented in 2007 [34]. HV-CMOS technologies provide standard submicron CMOS transistors (which operate at less than 3.3 V) and high voltage transistors (operating at for example up to 60 V) in a triple-well process. The low-voltage transistors are used for the internal electronics

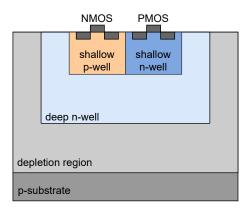

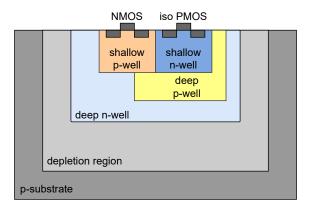

Figure 3.3: In a triple-well structure electronics can be placed in shallow n- and p-wells. A high voltage is applied at the substrate leading to a large depleted area.

(signal amplification, signal processing and readout). The high voltage transistors are used in the output driver [34].

Many HV-CMOS processes offer so-called floating logic. Floating logic allows the implementation of low-voltage electronic blocks in which the ground node is electrically isolated from the substrate. If a p-substrate is used, all transistors of a floating block are placed in a single, low-doped deep n-well. The triple-well structure allows the use of a p-substrate with a deep n-well and a shallow n- and p-well, as seen in figure 3.3. The transistors are placed in these shallow wells with PMOS transistors located in the n-well and NMOS transistors in the p-well [34]. Small standard low-voltage transistors can be used, although a high reverse bias voltage with respect to the p-substrate is applied to the deep n-well. This is possible because the transistors inside the n-well are shielded from the large voltage and are driven with low voltage between their electrodes. In a 0.35 μm process, the depletion area between the deep n-well and the substrate is about 10 μm for a reverse bias of 60 V. This leads to about 780 electrons generated by a MIP. The depleted area can be larger than the depleted area of a typical pn-junction in a MAPS.

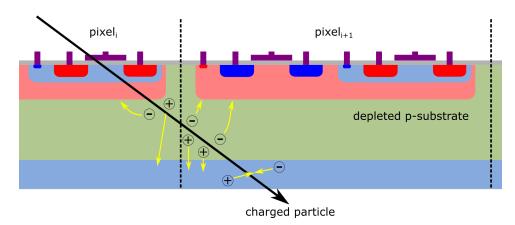

For a pixel, the deep n-well has two functions: on one hand it is used to isolate the shallow wells and on the other hand it is used as charge collecting electrode. Complex electronics can therefore be placed inside the n-well. The deep n-well is connected to a highly-resistive circuit based on PMOS transistors between the analogue positive supply voltage (vdda) of 1.8 V and the n-well [34]. The charge generated by a particle in the depleted region is separated by the strong electric field and the negative charge is collected by the n-well [35]. To detect the charge, the n-well is floating, which means that it is acting like a capacitance. The collected charge leads to a small potential drop in the n-well. This small potential drop is amplified by a charge sensitive amplifier also located in the pixel. This is an important property of the pixel: the electronics in the pixel is floating so it can measure the potential change in its own substrate [36] [37].

Figure 3.4: A particle generates electron-hole pairs inside a HV-CMOS sensor. The electrons are collected by the collecting electrode, the deep n-well. Here the charge is collected by two pixel electrodes (charge sharing). (From [6])

Due to the strong field, charge is collected by drift, resulting in a fast charge collection process with a time resolution on the order of 15 ns [35] [38] [39]. Figure 3.4 shows a charged particle moving through the HV-CMOS sensor. The electrons are collected by drift in the charge collection electrode (deep n-well). The holes are collected by the substrate contact and do not contribute to the signal charge. If an electron-hole pair is generated outside the depletion region, it is not collected in time to contribute to the signal. In the figure, the generated charge is collected by two neighbouring pixels, which is called charge sharing. If all generated charge is collected by the same pixel, there is no charge sharing and only this pixel generates a hit signal [34] [6].

$\rm HV\text{-}MAPS$  offers 100 % fill factor as the pixels are fully sensitive. In addition to the advantages of MAPS,  $\rm HV\text{-}MAPS$  enable a fast signal response as charge collection is mainly done by drift. This makes  $\rm HV\text{-}MAPS$  suitable for particle detection, for example in tracking detectors.

### Chapter 4

## Application for particle physics experiments and particle therapy

In this work, sensors for particle detection were developed for two applications: for particle tracking in the Mu3e experiment (MuPix) and for beam monitoring in particle therapy for HIT (HitPix). In this chapter first the Mu3e experiment will be presented to illustrate the environment and requirements of MuPix. The motivation for the Mu3e experiment is explained in 4.1.1 and in 4.1.2 the detector system with the different sub-detectors is described. Section 4.1.3 focuses on the impact of the MuPix for Mu3e.

The second application of a particle detection sensor is beam monitoring in cancer treatment centres that offer particle therapy, such as the Heidelberg Ion Therapy Centre (HIT). In section 4.2.1 particle therapy is explained, followed by a short introduction to beam monitoring at HIT. In section 4.2.3 the idea of a HV-MAPS beam monitoring chip is discussed.

#### 4.1 Application for the Mu3e experiment

#### 4.1.1 Motivation of the Mu3e experiment

The Mu3e experiment aims to search for the lepton flavour violating decay  $\mu^+ \to e^+e^-e^+$  with a sensitivity of one in  $10^{16}$  muon-decays in the second phase [40]. In the first phase, the existing muon beam line  $\pi E5$  at the Paul Scherrer Institute (PSI) will be used to reach a single event sensitivity of  $2 \cdot 10^{-15}$ , representing  $10^8$  muon decays per second. In the second phase, it is planned to use a new muon beam line studied in the high intensity muon beam HiMB project at PSI with a higher intensity [41] [42].

In the Standard Model of particle physics the  $\mu^+ \to e^+e^-e^+$  decay is strongly suppressed because lepton flavour violation is suppressed at tree level. Models beyond the Standard Model allow an experimentally accessible amount of lepton flavour violating processes like the  $\mu^+ \to e^+e^-e^+$  decay. Observing this process would new physics could be discovered [40] [42].

In phase I the detector has to provide a single event sensitivity of  $2 \cdot 10^{-15}$  on the branching fraction which requires more than  $2.5 \cdot 10^{15}$  stopped muons, leading to a run time of 400 days [42].

For Mu3e two types of background are particularly important. One is the muon decay with internal conversion  $\mu^+ \to e^+ e^- e^+ \bar{\nu}_\mu \nu_e$ . This requires precise momentum resolution for suppression. This is achieved by an ultra-thin detector to minimise multiple scattering. In addition, there is combinatorial background, for example, due to Michel decays and Bhabha scattering. Here, an excellent momentum, vertex and time reconstruction are necessary for the suppression [40] [42] [41].

#### 4.1.2 Concept of the Mu3e detector system

The Mu3e detector consists of different sub-detector systems to fulfil the requirements in efficiency and momentum resolution, timing and track measurements [43]:

- Ultra thin pixel tracking detector

- Scintillating fibre detector

- Scintillating tile detector

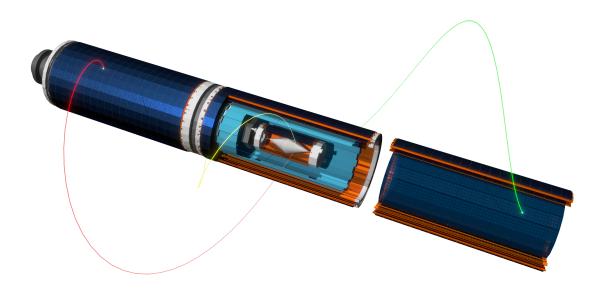

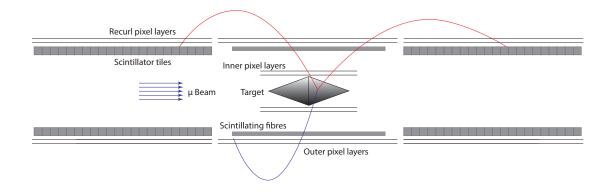

The muons are stopped at a target, such that the decaying muon is at rest and emits all decay products at the same time. Figure 4.1 shows an open 3D view of the detector [42].

A magnetic field of 1 T is provided by a solenoid around the whole Mu3e detector. The silicon pixel tracker is used to measure the momenta of the particles. The dominant factor

Figure 4.1: Open view of the Mu3e detector with the stopping target in light gray, the pixel tracker in orange and the scintillating fibre detector in light blue. (From [42])

for the momentum resolution is multiple Coulomb scattering in the pixel detector material. Therefore, the detector has to be as thin as possible. This is achieved with thinned silicon High Voltage Monolithic Active Pixel chips [44] [45] (see chapter 3.2).

In the following, the different parts forming the Mu3e detector system are introduced.

The task of the **magnet** is to provide a homogeneous solenoidal magnetic field of  $B=1\,\mathrm{T}$  for the tracking detector to allow a precise momentum determination of the muon decay products. The magnetic field has to be homogeneous. The requirements only allow field inhomogeneities along the beam line below relative deviation of  $10^{-3}$  within  $\pm 60\,\mathrm{cm}$  around the center of the magnet. Furthermore, the magnet has to be stable and operation has to stay at reasonable costs. To fulfil the requirements a superconducting magnet design with a closed cooling system has been chosen. The magnet has been delivered in 2020 and performs as expected [46] [42].

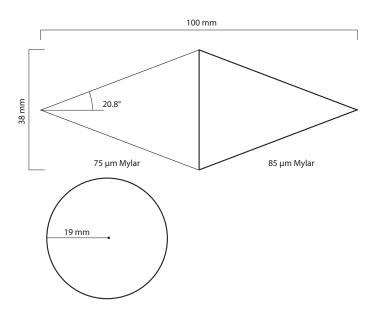

The muons ( $p = 28 \,\mathrm{MeV/c}$ ) are stopped at a **target**. The stopping target is optimised for stopping power, for keeping its impact on the track measurement low and for wide spreading of the  $\mu$ -stops. A target similar to the one used for SINDRUM [47] shaped like a double cone made out of Mylar is chosen for Mu3e. The dimensions of the stopping target are shown in figure 4.2. The target has a mass of 0.671 g and a total area of 6 386 mm<sup>2</sup> [42].

The **pixel tracker** has to provide precise hit information of the electrons for track reconstruction. To allow for high vertex and momentum resolution the multiple scattering needs

Figure 4.2: Dimensions of the stopping target for Mu3e. The target is shaped like a double cone and made out of Mylar. (From [42])

to be minimized leading to the task of material minimization in the active area. Therefore, High Voltage Monolithic Active Pixel Sensors (HV-MAPS) thinned to 50 µm were chosen to build the pixel tracker. The HV-MAPS are mounted on thin flexible High Density Interconnect (HDI) circuits which provide the power, signal and data lines. The HV-MAPS developed for the Mu3e experiment are called MuPix. The data are read out by three differential lines per chip at a bandwidth of 1.25 Gbit/s per line [42]. The MuPix chips are bonded to the HDI using Singlepoint Tape Automated Bonding (SpTAB), so no additional bonding material is necessary [48] [49]. Thin polyimide foils provide the mechanical stability. Due to the requirement of minimal material no further support structure is allowed. Therefore, the pixel modules consist only of the sensor, the HDI and the polyimide foil. The cooling system is based on a dry helium atmosphere for minimum additional multiple scattering [49] [42].

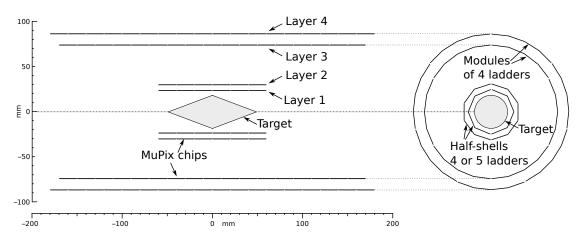

Figure 4.3 shows the three parts of the Mu3e pixel tracker: in the middle, close to the target, the central pixel tracker is located and on the sides two recurl trackers are placed. The central pixel detector detects the hits for track and decay vertex reconstruction. Reconstruction of hits with higher purity and improved momentum resolution is possible with the hits measured by the recurl trackers. All three parts of the pixel tracker are built out of the same HV-MAPS chip, the MuPix. The central pixel tracker consists of four layers while the recurl trackers are made up of two layers each [42]. Figure 4.4 shows the central tracker with the different layers from two different perspectives.

Besides the pixel tracker the Mu3e detector contains two timing detectors, the scintillating fibre and scintillating tile detector. Their location is shown in figure 4.1 [43].

Figure 4.3: The Mu3e pixel tracker consists of the central tracker and two recurl trackers. It is complemented by two timing detectors, the scintillating fibre and tile detectors. (From [42])

Figure 4.4: The central pixel tracker is formed by four layers of MuPix chips. The layers are built up from modules consisting of 4 or 5 ladders. (From [42])

The purpose of the **scintillating fibre detector** (SciFi detector) is mainly to suppress accidental combinatorial background from tracks with different timing. This leads to challenging specifications of the SciFi detector: time resolution of 250 ps, efficiency of more than 95 %, spatial resolution around 100 µm. Because the SciFi detector is located in the central region of the experiment (see figure 4.1 in light blue), it has to be as thin as possible and compact, similar to the pixel tracker. In addition to the timing measurement, the SciFi detector can perform a time of flight measurement to help resolving the direction of rotation of the recurling tracks. The SciFi detector has a radius of 61 mm and a length of about 300 mm [50] [51] [42].

The scintillating tile detector is located in the recurl section inside the pixel layers as shown in figure 4.3. The aim of the scintillating tile detector is a time resolution below 100 ps and close to 100 % efficiency. This is necessary to identify a coincident signal from three electrons and suppress combinatorial background. With a time resolution below 100 ps the tile detector provides the most precise timing information of the particle tracks possible. Because the scintillating tile detector, unlike the fibre detector, is not located in the centred region of Mu3e, but in the recurl stations, there are no strong constraints in material budget. Nevertheless, the detector is placed inside the recurl pixel detectors leading to tight spatial constraints [52] [42].

Both the scintillating fibre and tile detector are read out by a custom mixed-signal Silicon Photo-Multiplier (SiPM) readout ASIC called MuTRiG (Muon Timing Resolver including Gigabit-link). The MuTRiG has 32 channels and is fabricated in UMC 180 nm CMOS technology. The output signals of the tile SiPMs are connected via a flexible printed circuit board to a MuTRiG chip. In [53] the MuTRiG is explained in detail.

Everything described until here, the different detectors, their electronics, the power distribution and the data acquisition systems are located inside the magnet. Everything in the magnet is packed densely, all parts produce heat, therefore a **cooling** concept for the whole experiment is needed. Except for the pixel tracker a water cooling system is used. The pixel detector has a special cooling system with gaseous helium to keep it at a temperature below 70 °C. The helium cooling system is a trade-off between cooling potential and radiation length [49] [42].

#### 4.1.3 MuPix – sensor development for Mu3e

As explained in the previous section, one of the main detector systems for the Mu3e experiment is the pixel tracker. All parts of the tracking detector (central part and recurl stations) will be built from highly specialised custom smart sensor ASICs: the MuPix. The development of such a specialised smart sensor in different generations for Mu3e is one core part of this thesis.

There are several requirements for a sensor used in a tracking detector. It must be thin to reduce multiple scattering, for Mu3e the sensors have to be thinned down to  $50\,\mu\text{m}$ . In addition, time resolution in the nanosecond range is needed, less than  $20\,\text{ns}$  in the case of Mu3e. Spatial resolution is also important and leads to the desired pixel sizes, e.g.  $80\,\mu\text{m} \times 80\,\mu\text{m}$  in the case of Mu3e. For high efficiency, a  $100\,\%$  fill factor of the pixel matrix is required.

These requirements can be fully met by HV-MAPS. These monolithic devices can be thinned to 50 µm. The pixel sizes for Mu3e can be realised. The HV-MAPS offer a time resolution of a few nanoseconds due to the fast charge collection by drift. Complex readout architectures and special data formats can be realised with the CMOS logic available in HV-CMOS processes. The sensitive sensor area can be maximised by a fully customised layout design.

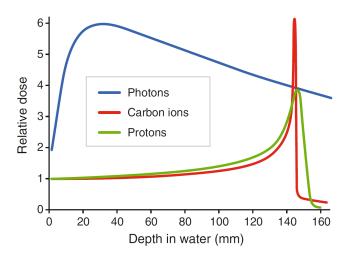

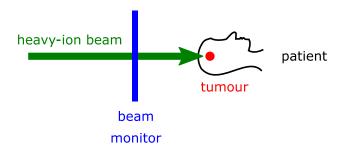

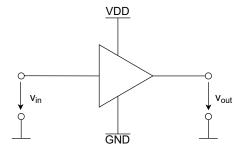

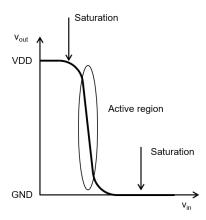

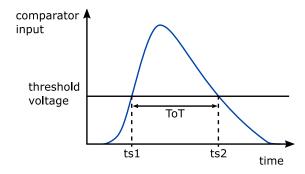

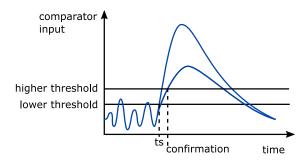

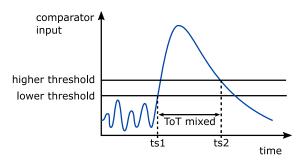

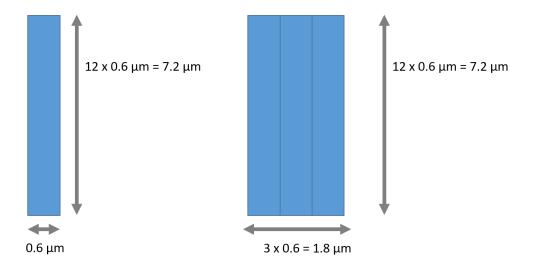

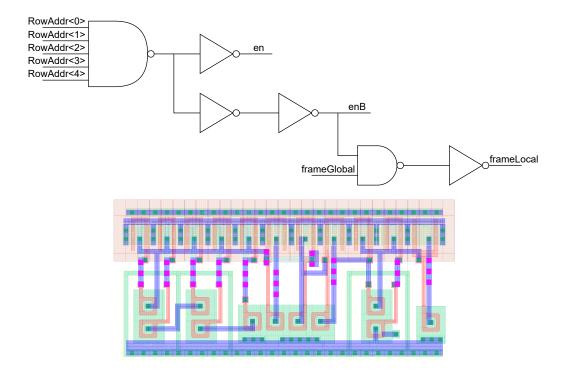

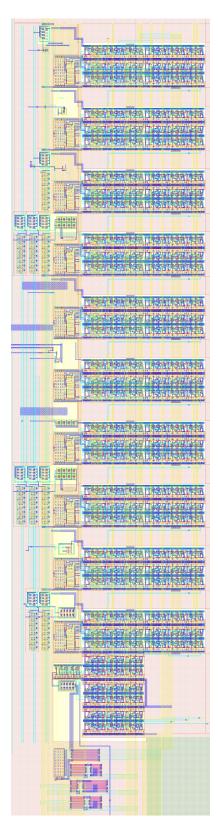

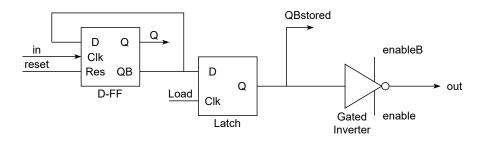

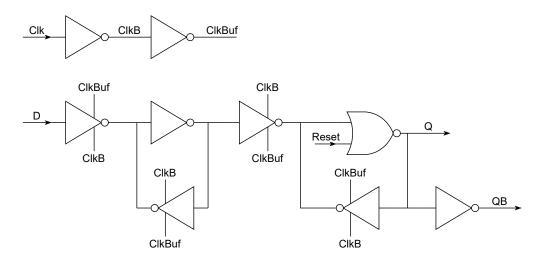

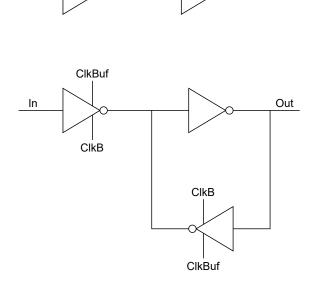

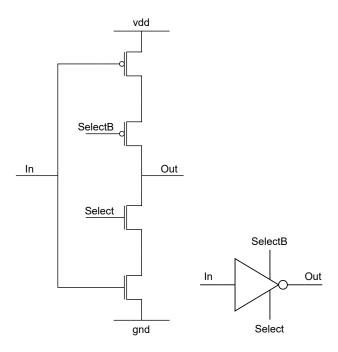

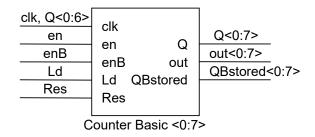

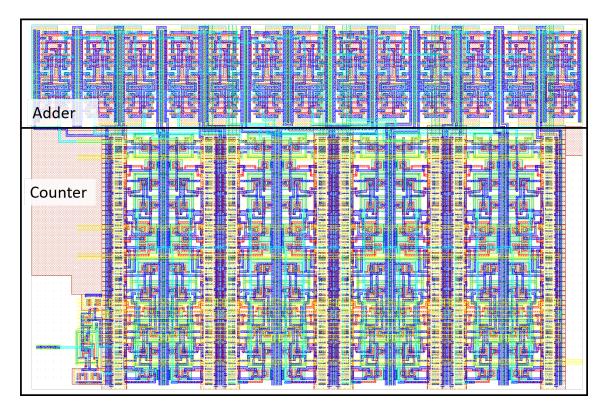

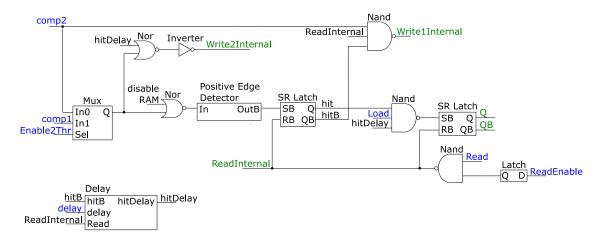

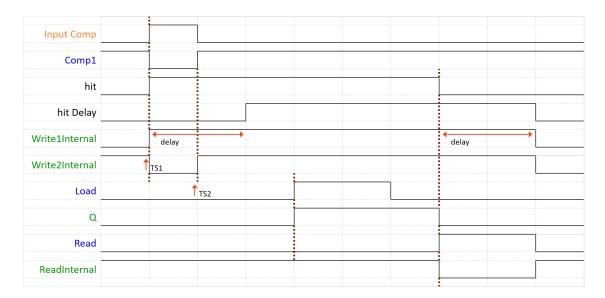

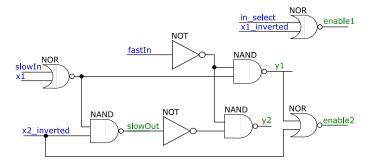

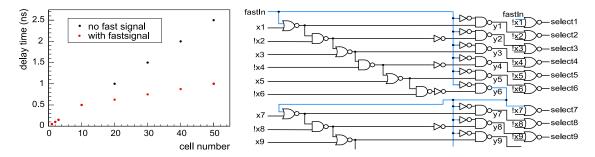

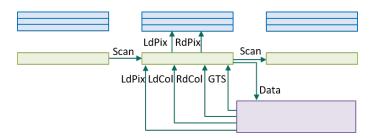

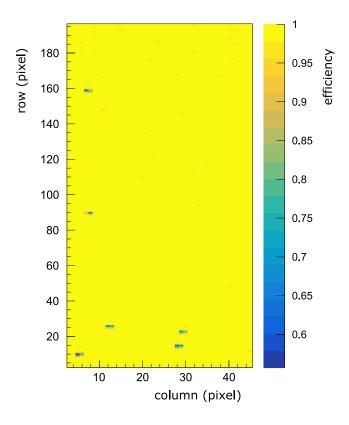

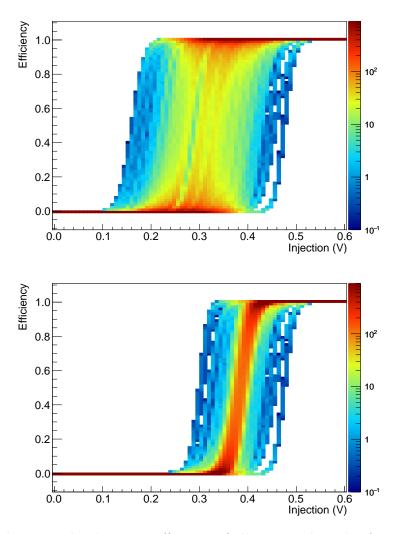

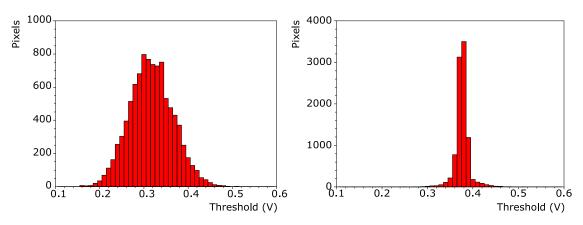

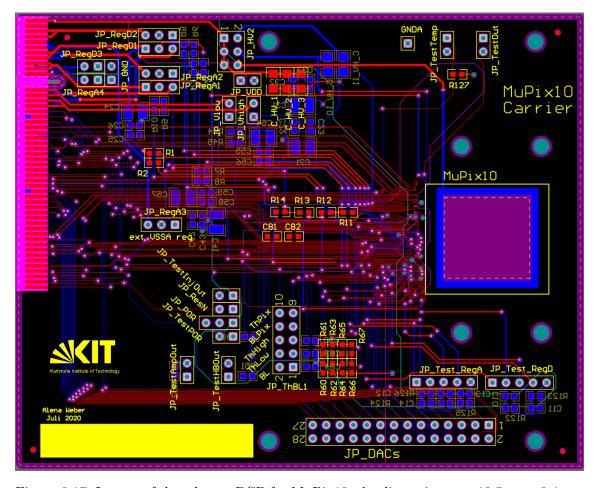

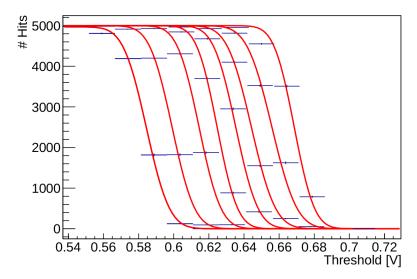

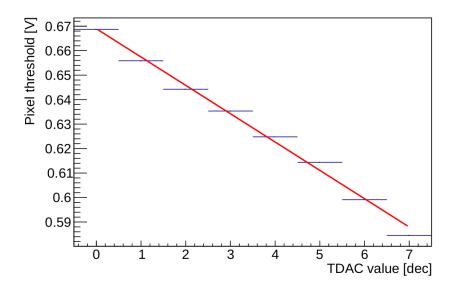

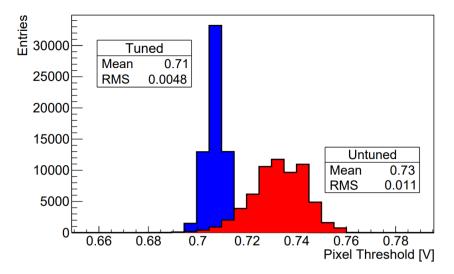

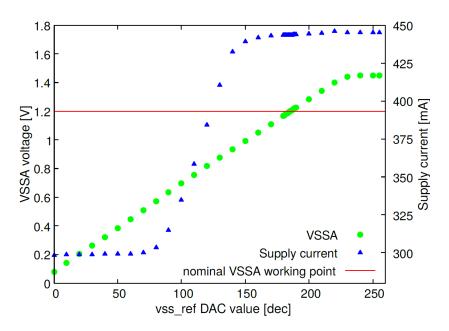

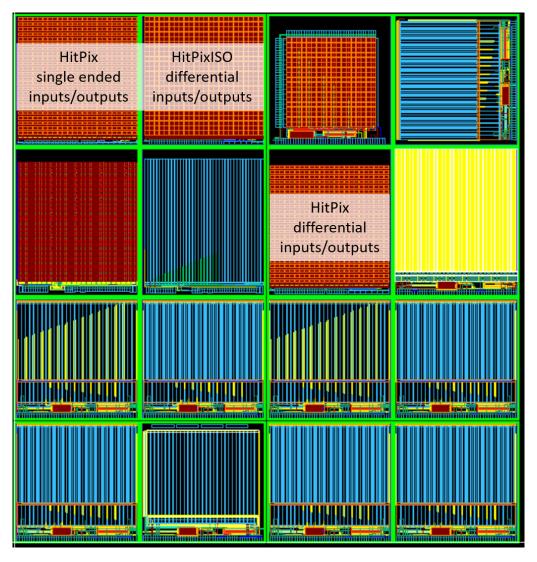

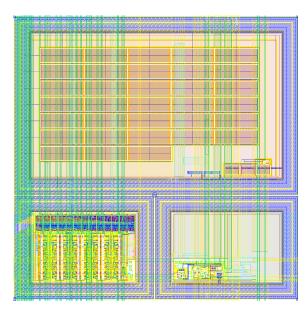

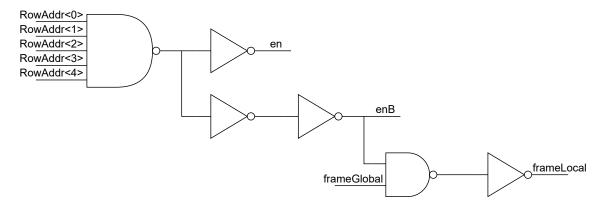

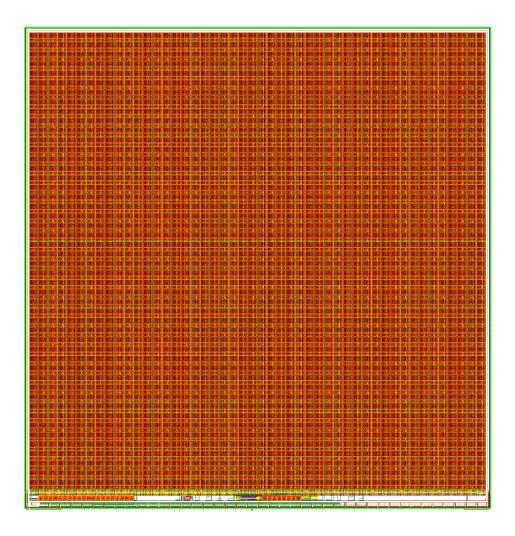

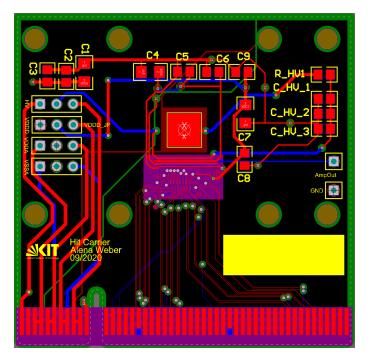

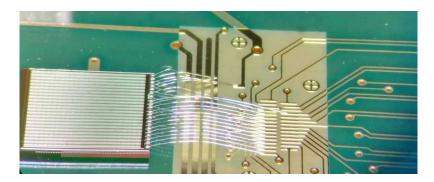

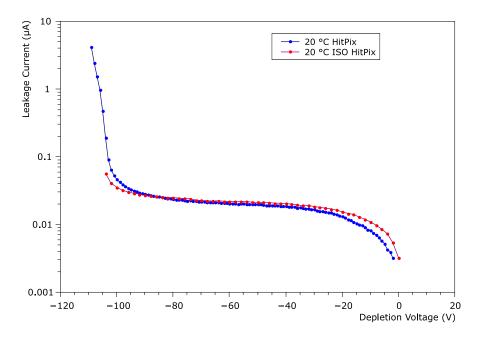

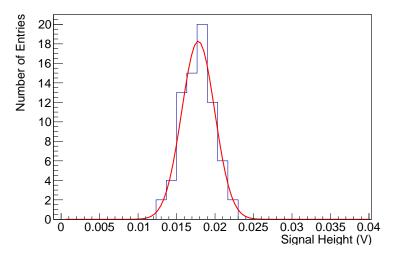

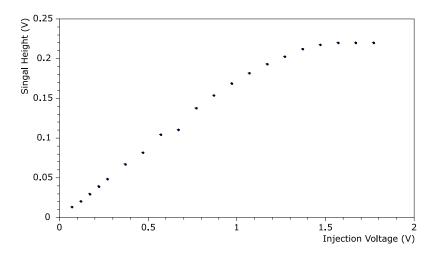

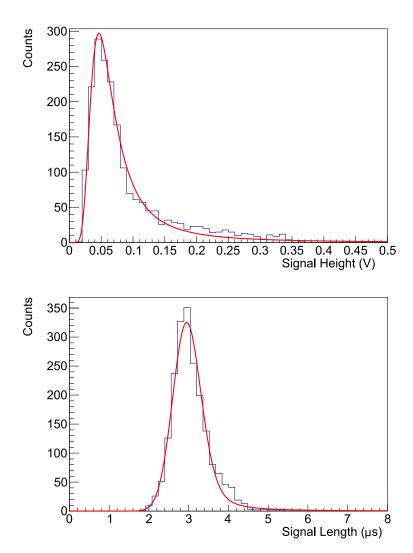

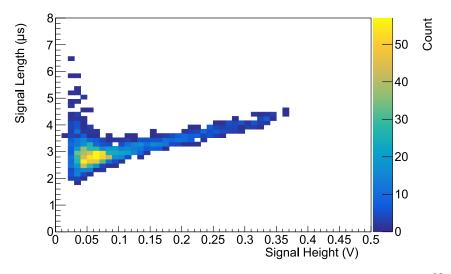

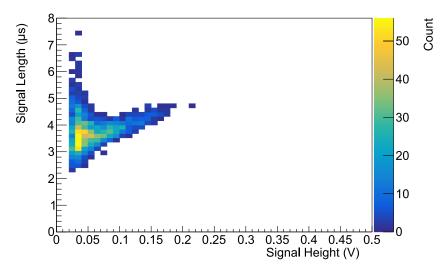

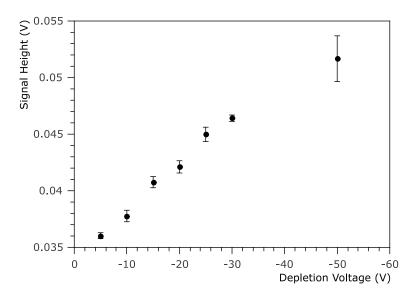

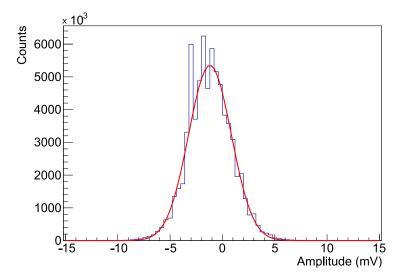

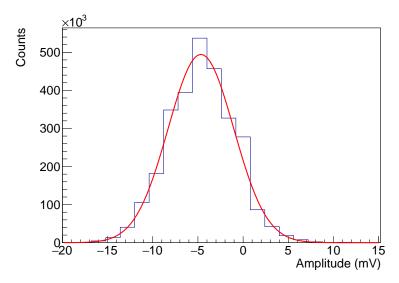

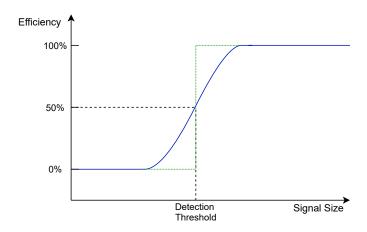

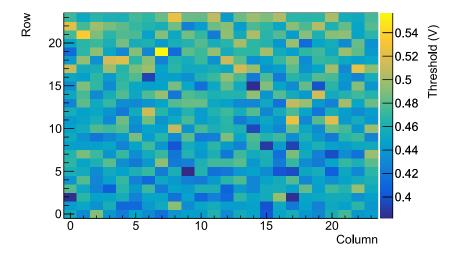

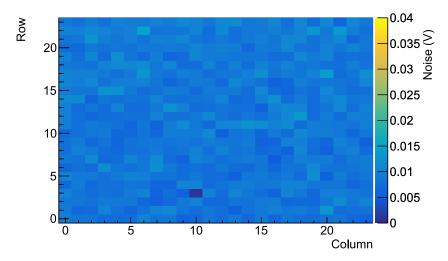

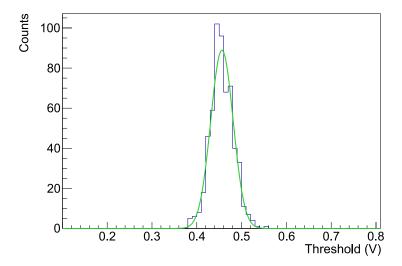

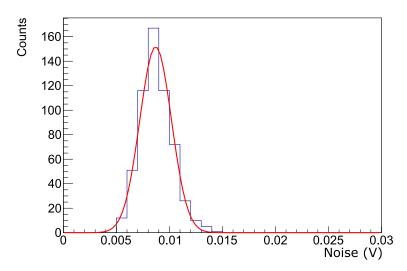

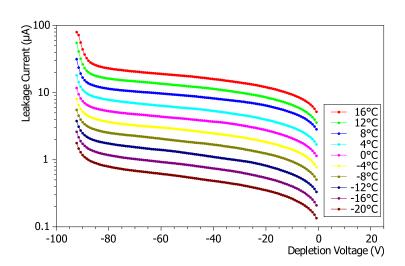

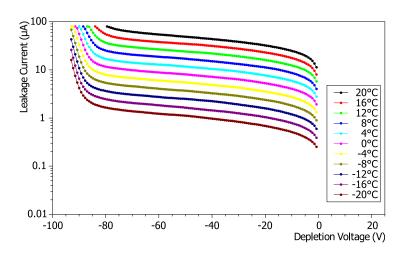

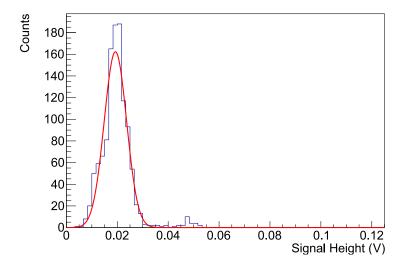

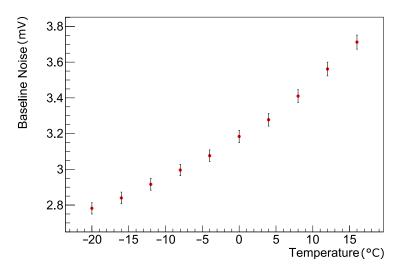

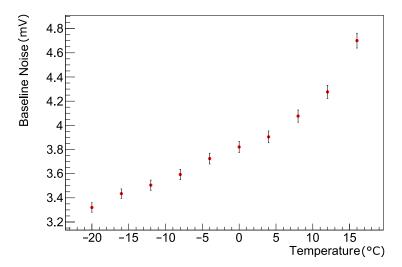

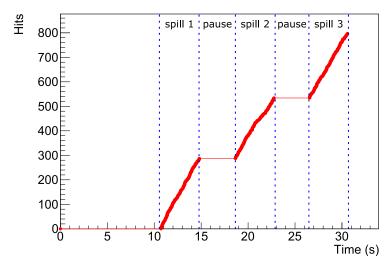

Another advantage is that HV-MAPS are cost-effective, the cost per square meter is in the order of 85 000 € [6]. This includes wafers, production costs and post-processing. With multiple beam tests and detailed characterisations of the MuPix chips, it was confirmed that they meet the Mu3e requirements [54] [55] [38] [56]. Integration tests of the tracking detector with MuPix10 chips are currently under way at PSI.