# Department of Physics and Astronomy University of Heidelberg

Master Thesis in Physics submitted by

Maurice Donner

born in Aachen (Germany)

2025

# Prototypes of monolithic pixel sensors based on a 65nm imaging process for high energy physics

This Master Thesis has been carried out by Maurice Donner at the Physikalisches Institut, University Heidelberg under the supervision of Prof. Dr. Silvia Masciocchi

## **Abstract**

The field of silicon imaging technology is advancing steadily. While consumer electronics will be its main driving factor, the vast applicability of silicon offers high energy physics a variety of highly efficient, high precision detector concepts. At CERN, the ALICE experiment is developing a new type of monolithic active pixel sensor, based on the Tower Partners Semiconductor Co., Ltd. (TPSCo) 65nm CMOS imaging process. This technology is foreseen to provide sensors to replace the innermost part of the currently installed Inner Tracking System 2 (ITS2) of the ALICE detector during the third Long Shutdown period 2026-2028 (LS3) of CERN's Large Hadron Collider (LHC).

To achieve a reduction in material budget, and limit power consumption, the innermost three layers of the Inner Tracking System 3 (ITS3) will be composed of wafer-scale stitched particle detectors. The development of this sensor started with the submission of a Multi Layer Reticle (MLR1) in 2021, and will soon conclude its second phase, the evaluation of the Engineering run 1 (ER1), in 2025. This thesis is concerned with test procedure of the first prototypes of this new sensor technology, namely the Analog Pixel Test Structure (APTS), and the Monolithic Stitched Sensor (MOSS). The basic readout and calibration procedure of the APTS is investigated, as well as the effect of electronic noise on the performance of the sensor. For MOSS, studies have been performed investigating single-event effects during two testbeam campaigns in March and April of 2024 at the heavy ion facility (HIF) at UCLouvain in Louvain-la-Neuve, and the cyclotron U-120M at the Nuclear Physics Institute (NIP) of the Czech Academy of Science. Additionally, the overall efficiency and operational margins of the first batch of MOSS has been studied at a third testbeam campaign at the Proton Synchrotron (PS) at CERN in July. These results are discussed with respect to the efficiency of MOSS sensors from the second batch. The results of this study contribute to a better understanding of the operational margin of the sensors, as well as their radiation hardness and the influence of design parameters on the performance of the sensor, and will be considered in the development of the next sensor generation.

# Zusammenfassung

Das Feld der Silizium-Bildgebungstechnologie entwickelt sich stetig weiter. Doch nicht nur die Unterhaltungselektronik, die zum größten Teil für besagte Entwicklung verantwortlich ist, profitiert von den vielfältigen Anwendungsmöglichkeiten von Silizium. Auch in der Hochenergiephysik wird von hochpräzisen und effizienten Detektorkonzepten basierend auf Siliziumsensoren Gebrauch gemacht. Am CERN entwickelt das ALICE-Experiment einen neuen Typ von monolithischen aktiven Pixel-Sensoren, basierend auf dem TPSCo 65nm CMOS-Prozess. Diese Technologie soll während der dritten Long Shutdown Phase 2026-2028 (LS3) des Large Hadron Collider (LHC) den inneren Teil des derzeitigen Inner Tracking System 2 (ITS2) des ALICE-Detektors ersetzen.

Im neuen Inner Tracking System 3 (ITS3) werden die innersten Schichten des derzeitig verbauten ALPIDE-Sensors durch Wafer-große Sensoren ersetzt, die zylindrisch um den Strahl herumgebogen sind. Vorteile dieses Entwurfs sind unter Anderem eine Reduktion des vorhan-

denen Materials (durch die intrinsische Stabilität der gebogenen Sensoren sind keine Trägermaterialien notwendig) und eine geringere Leistungsaufnahme im Vergleich zum ITS2. Die Entwicklung dieser Sensoren begann mit der MLR1 Testphase im Jahr 2021 und die zweite Phase wird voraussichtlich mit der Auswertung des Engineering Run 1 (ER1) im Jahr 2025 enden. In dieser Arbeit wird im Rahmen des ER1 über die Testprozedur der ersten Prototypen dieser neuen Sensortechnologie, dem APTS und dem MOSS, berichtet. Die grundlegende Auslese- und Kalibrierungsprozedur des APTS wird untersucht, sowie der Einfluss von elektronischen Störquellen auf die Leistung des Sensors charakterisiert. In zwei Testbeam-Kampagnen im März und April 2024 am Heavy Ion Facility (HIF) der UCLouvain in Louvainla-Neuve und am Zyklotron U-120M des Nuclear Physics Institute (NIP) der Czech Academy of Science wurden Single-Event-Effekte des MOSS Sensors untersucht, welche in dieser Arbeit präsentiert und diskutiert werden. Zusätzlich wurde die Detektoreffizienz des MOSS in einer weiteren Testbeam-Kampagne am Proton Synchrotron (PS) des CERN im Juli untersucht. Anhand dieser Studien wird die Betriebsmarge des MOSS Sensors bestimmt und zwischen verschiedenen Versionen des MOSS Sensors verglichen. Die Ergebnisse dieser Studie werden in die Entwicklung der nächsten Sensorgeneration einfließen und tragen zu einem besseren Verständnis der Strahlenhärte und des Einflusses von Designparametern auf die Leistung des Sensors bei.

CONTENTS CONTENTS

# **Contents**

| 1 | Intr | oduction                                     | 4 |

|---|------|----------------------------------------------|---|

| 2 | Sem  | niconductors                                 | 5 |

|   | 2.1  | A truly cylindrical silicon pixel sensor     | 5 |

|   | 2.2  | Working principle of semiconductors          | 6 |

|   |      | 2.2.1 The p-n junction                       | 8 |

|   |      | 2.2.2 Particle detection                     | 0 |

|   |      | 2.2.3 Applications in electronics            | 2 |

|   | 2.3  | The Analog Pixel Test Structure (APTS)       | 4 |

|   |      | 2.3.1 APTS chip architecture                 | 4 |

|   |      | 2.3.2 Readout                                | 7 |

|   | 2.4  | The Monolithic Stitched Sensor (MOSS)        | 8 |

|   |      | 2.4.1 Sensor design                          | 8 |

|   |      | 2.4.2 Readout                                | 0 |

|   |      | 2.4.3 MOSS Experimental Setup                | 1 |

|   | 2.5  | The BabyMOSS test system                     | 2 |

|   |      | 2.5.1 BabyMOSS Experimental Setup            | 2 |

| 3 | AP   | ΓS characterization and noise studies 2      | 3 |

|   | 3.1  | Gain calibration                             | 4 |

|   | 3.2  | Energy calibration                           | 5 |

|   | 3.3  | Electronic noise on the APTS                 | 9 |

|   |      | 3.3.1 Electronic noise                       | 0 |

|   |      | 3.3.2 APTS noise attenuation                 | 1 |

| 4 | МО   | SS and BabyMOSS studies 3                    | 4 |

|   | 4.1  | Laboratory tests and sensor scans            | 4 |

|   |      | 4.1.1 Fake-hit rate scan                     | 5 |

|   |      | 4.1.2 Threshold scan                         | 6 |

|   | 4.2  | Single event effects                         | 9 |

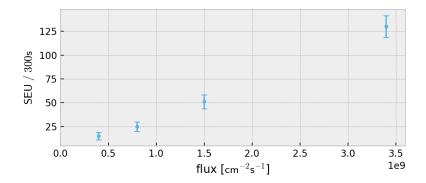

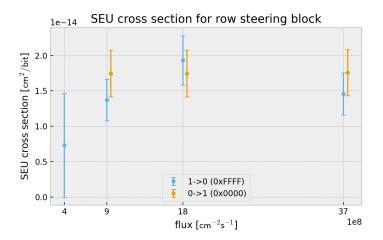

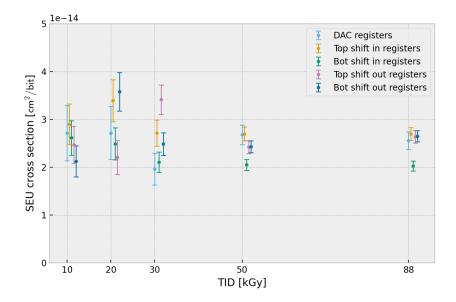

|   |      | 4.2.1 Single event upsets (SEUs)             | 0 |

|   |      | 4.2.2 The Cyclotron U-120M at the NPI of CAS | 1 |

|   |      | 4.2.3 Single event upset (SEU) studies       | 3 |

|   |      | 4.2.4 Single event latchups (SELs)           | 6 |

|   |      | 4.2.5 The Heavy-Ion Facility at UCLouvain    | 7 |

|   |      | 4.2.6 Single event latchup (SEL) studies     | 9 |

|   | 4.3  | Detection efficiency of the MOSS detector    | 0 |

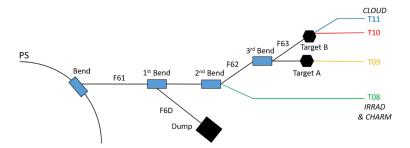

|   |      | 4.3.1 The Proton Synchrotron at CERN         | 1 |

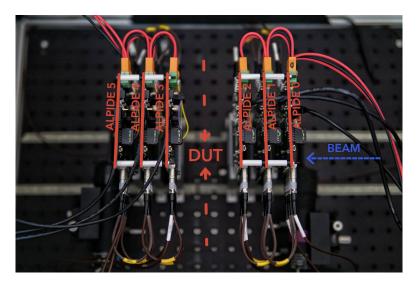

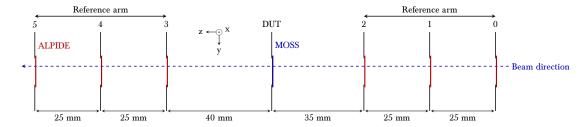

|   |      | 4.3.2 Beam telescope                         | 3 |

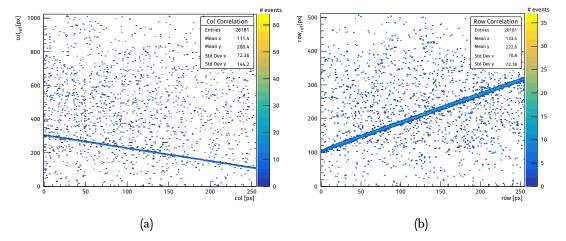

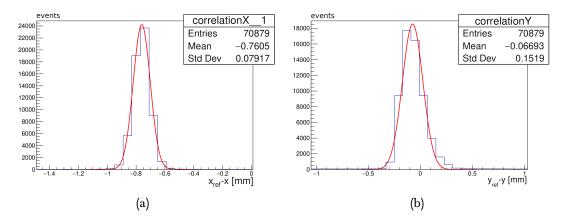

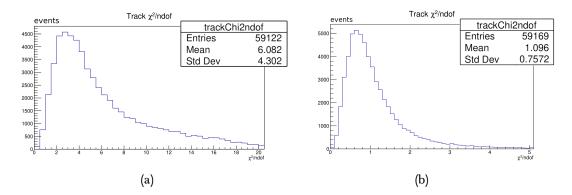

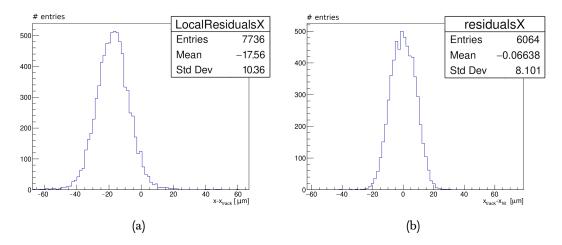

|   |      | 4.3.3 Testbeam data analysis                 | 5 |

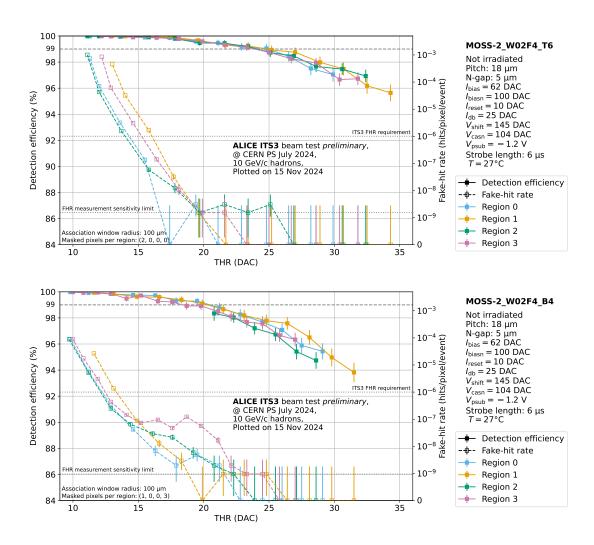

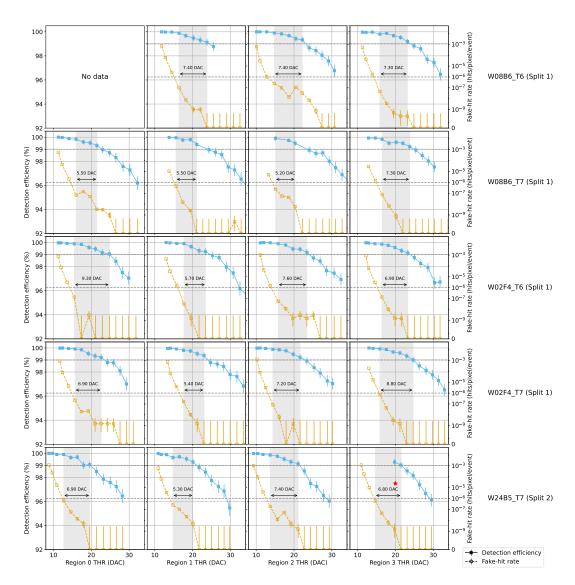

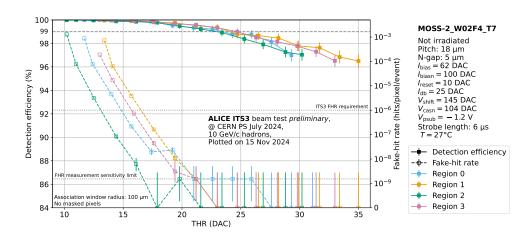

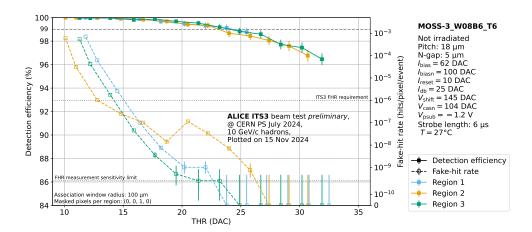

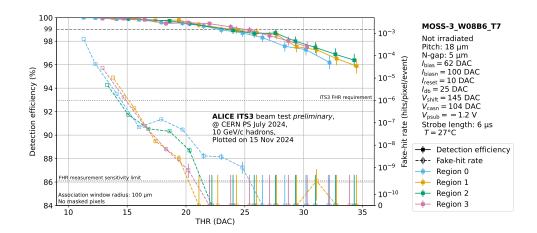

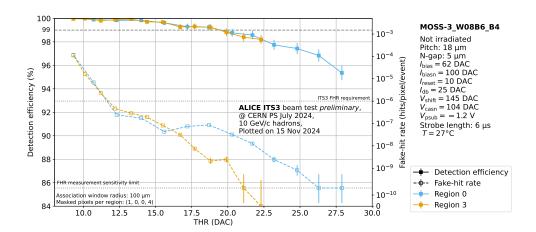

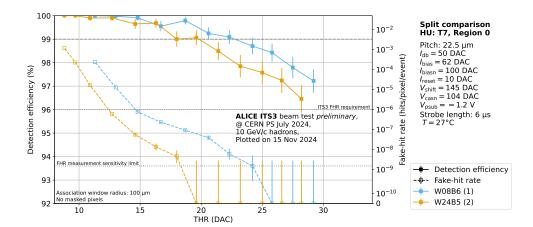

|   |      | 4.3.4 MOSS detection efficiency              | 8 |

CONTENTS CONTENTS

| 5 Con       | clusion and Summary | 63 |

|-------------|---------------------|----|

| Append      | lices               | 66 |

| A.1         | Acronyms            | 66 |

|             | References          |    |

| <b>A.</b> 3 | List of figures     | 75 |

| A.4         | List of tables      | 76 |

| <b>A</b> .5 | Additional figures  | 77 |

## 1 Introduction

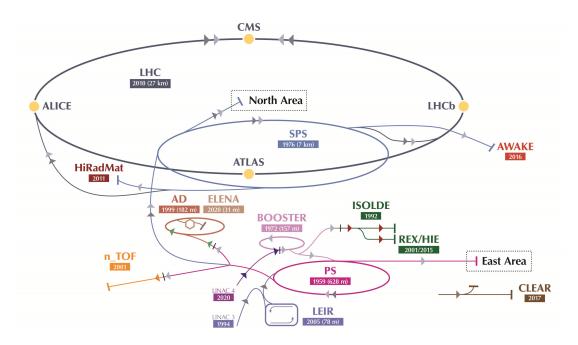

In July 2022 at CERN, the four big experiments at the Large Hadron Collider (LHC), A Large Ion Collider Experiment (ALICE), A Toroidal LHC Apparatus (ATLAS), Compact Muon Solenoid (CMS) and LHC-beauty (LHCb) entered a new period of data taking with Run 3. All of them previously performed upgrades to their detection and data selection systems, some of which consisted of the complete replacement of subsystems, to keep up with the high information density resulting from both the proton-proton and lead-lead collisions at a center-of-mass energy of up to 6.8 ATeV and with a heavy-ion collision rate more than ten times higher than in previous runs [1].

The ALICE experiment is dedicated to probing the physics of strongly interacting matter, in particular the properties of the Quark-gluon plasma (QGP). The QGP is a state of matter with such a high energy density, that quarks and gluons are no longer confined into hadrons, but instead form a collective medium that expands and flows like a relativistic fluid. In this plasma, the quarks and gluons that make up all nuclei are strongly coupled to- and interacting with another, while the hydrodynamic expansion accelerates them outwards, cooling the plasma in the process. It is theorised, that this state of matter is very similar to the contents of the universe only 10  $\mu$ s after the Big Bang [2]. In laboratory conditions, the LHC achieves this state by colliding heavy lead ions with an energy of up to  $\sqrt{s_{NN}} = 5.36\,\text{TeV}$  per nucleon pair. By studying the production and decay of outgoing particles from the QGP, ALICE contributes to the understanding of the fundamental interaction of subatomic matter and complex phenomena such as color confinement and chiral symmetry restoration. The experiment attempts to shed light on how matter is organized, with specific investigation of the strong nuclear force and its role in generating a big portion of the mass of ordinary matter.

The current innermost component of the ALICE detector, the Inner Tracking System (ITS)2, is made of seven layers of silicon-based Monolithic Active Pixel Sensor (MAPS), amounting to a total active area of  $10\,\mathrm{m}^2$ . The implemented sensor is the thoroughly researched and tested ALICE Pixel Detector (ALPIDE) sensor, which employs a 180 nm CMOS Imaging Process from TPSCo<sup>1</sup>. The current material budget (i.e. the detector thickness in terms of radiation length) of one layer of the ITS2 amounts to  $0.262\% X_0$  for the inner three layers and  $0.813\% X_0$  for the outer four layers [4], which has already been a huge milestone in high precision particle tracking. Following the path towards even higher spatial resolution and improved tracking performance, the material budget is one of the most important and difficult to overcome limitations, since it is directly related to the mean angular deflection of charged particles on their way through the different detector layers by multiple Coulomb scattering. It remains one of the main goals of many high-energy physics experiments to reduce the material budget of their detector systems built for particle tracking purposes.

<sup>&</sup>lt;sup>1</sup>Formerly: TowerJazz Panasonic Semiconductor Co., Ltd. (TPSCo) [3].

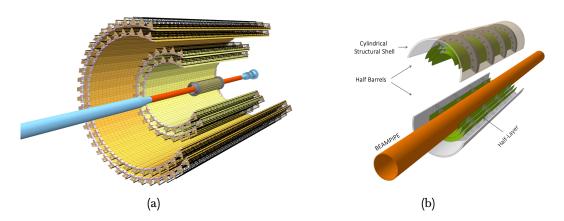

# 2 Semiconductors

Semiconductor-based detector technology dates all the way back to 1962 with the detection of a gamma-ray spectrum via a lithium-drifted p-i-n junction in Germanium [5]. In 1969, the first Charge-Coupled Device (CCD) was invented [6], solidifying a foundation for silicon as a material in particle detection. However, these devices were still difficult to manufacture, integrate with on-chip electronics and read out at high rates [7], making it simply too expensive to replace the large-area covering gas detectors. In the late 1980s the CMOS process became well-established, replacing the previously used NMOS logic as the dominant fabrication process, as well as the earlier transistor-transistor-logic (TTL). It uses complementary and symmetrical pairs of p-type and n-type metal-oxide-semiconductor field-effect transistors (MOSFETs) (see section 2.2), to construct integrated circuit chips, including microprocessors, microcontrollers, memory chips and other digital logic circuits. Profiting from the cheaper and more accessible technology, active-pixel sensors began making their way into high-energy particle physics applications. These devices had the special advantage of in-pixel amplification and reduced noise compared to earlier passive designs [8]. As demands for high resolution, high detection rate, and low material thickness devices in particle detection applications steadily rises, active-pixel sensors become more and more attractive as a replacement for previous detectors based on gas-chambers, or silicon strips. With new developments in commercially available silicon imaging technology (especially for consumer applications like photography), it is possible to build these devices with smaller and smaller features - and therefore with increasingly tight spacing. Each new generation semiconductor process receives its name by its minimum feature size in nanometers, either of the process's transistor gate length<sup>2</sup>, or its transistor density<sup>3</sup>. The currently installed ALPIDE in the AL-ICE ITS2 (Figure 2.1 (a)), is based on the TPSCo 180 nm imaging process [9], while the new generation of pixel sensors (foreseen to be installed in the ITS3 in 2026 [10]) is based on the TPSCo 65 nm technology node. The smaller feature size of this generation of silicon pixel sensors directly results in several advantages, such as smaller pixel sizes and the availability of large-scale silicon wafers, making it possible to fabricate pixel sensors with unprecedented spatial resolution, that cover a larger area than what was ever possible before. Within the ITS3, they will be thinned down to below 50 µm, and bend around the beam pipe, getting as close as 19 mm to the interaction point (compared to the previous 23 mm in the ITS2) [11].

#### 2.1 A truly cylindrical silicon pixel sensor

The layout of the ITS3 is shown in Figure 2.1 (b). In order to achieve a truly cylindrical layout, the ITS3 is foreseen to make use of a relatively recent technology in the CMOS imaging process called *stitching*. It describes the process of merging multiple design structures on a wafer together, creating a single CMOS image sensor. Its size is not bound by current manufacturing limitations, such as the maximum reticle field size of wafer steppers, but instead only by the wafer size, which in commercial applications can become as large as  $300 \times 300 \, \text{mm}^2$ . Due to the intrinsic stability of their cylindrical geometry, the new ITS3

<sup>&</sup>lt;sup>2</sup>The distance between the transistor's source and drain electrodes

$<sup>^3</sup>$ The exact naming of a process node is decided by the manufacturer, not an exact measurement of feature size.

Figure 2.1: (a) Layout of the ITS2 detector [4] (b) Layout of the ITS3 Inner Barrel [12]

layers do not have to be supported by a conventional aluminum frame, but are foreseen to be held in place by ultra-lightweight spacers made from carbon foam. The entire design is going to feature a very low power density across the pixels, which means all water cooling inside the detection volume of the ITS2 will be replaced by air cooling in ITS3. This will decrease the material budget down to  $0.07\%~X_0$  per layer [11]. This is a crucial step forward, as the current ITS2 material budget is the main limiting factor for the study of low transverse-momentum particles. Monte Carlo simulations have shown [12], that going from the ITS2 to the ITS3 will increase the capability of the detector to separate secondary vertices of heavy-flavour decays from the interaction point, by improving the reconstruction of their decay topologies and those of dileptons. This will all be crucial to provide a better understanding about the properties of the QGP formed in heavy-ion collisions. The general requirements for the ITS3 sensors are listed in Table 1. Current prototypes of  $1.4\,\mathrm{cm} \times 25.9\,\mathrm{cm}$  long pixel sensor strips have already been manufactured and are currently being tested at the European Organization for Nuclear Research (CERN). This prototype is called the MOSS, and will be discussed in Section 2.4.

#### 2.2 Working principle of semiconductors

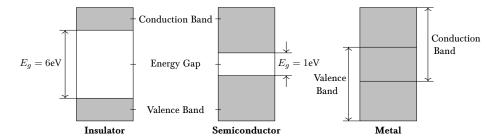

The semiconductors used in electronic devices are crystalline solids – highly ordered structures forming a crystal lattice extending in all directions. This lattice is made up of the nuclei of the crystal atoms (in this case: Si) and tightly bound *valence electrons*. Pauli's exclusion principle states, that the same energy state can not be occupied by more than one electron at a time, and there is only a limited number of energy states that fulfill the periodic boundary conditions of the crystal lattice. Together, these conditions determine, whether the crystal is electrically conductive or not. Valence electrons reside in the so-called *valence band*, while energetically higher electrons take up a spot in the *conduction band* (see Figure 2.2).

The latter is directly responsible for the electrical conductivity of the material. Since the kinetic energy of the electrons in the conduction band is higher than the potential energy of the free states in the valence band, the electrons in the conduction band are delocalised, and act as quasi-free charge carriers. Intrinsically, silicon is an insulator, i.e. there is a gap

| Particle Rate                                          |                                                      |

|--------------------------------------------------------|------------------------------------------------------|

| Pb-Pb average interaction rate                         | 50 kHz                                               |

| Pb-Pb peak interaction rate                            | 164 kHz                                              |

| Total particle flux (peak flux, Layer 0)               | $5.75\mathrm{MHz~cm^{-2}}$                           |

| Detection performance                                  |                                                      |

| Single point resolution                                | $\lesssim 5  \mu \mathrm{m}$                         |

| Pixel pitch                                            | $< 25  \mu m$                                        |

| Detection efficiency                                   | > 99 %                                               |

| Fake-hit occupancy (10 µs Frame Duration)              | $< 1 \times 10^{-6}  \mathrm{pixel^{-1} frame^{-1}}$ |

| Readout efficiency                                     |                                                      |

| Fraction of Pb-Pb interactions fully recorded, Layer 0 | > 99.9 %                                             |

| Fraction of incomplete Pb-Pb interactions, Layer $0$   | $< 1 \times 10^{-3}$                                 |

| Power budget                                           |                                                      |

| Power Dissipation Density, Active Region               | $< 40 \mathrm{mW} \mathrm{cm}^{-2}$                  |

| Power Dissipation Density, Peripheral Region           | $< 1000  \mathrm{mW \ cm^{-2}}$                      |

| Material parameters                                    |                                                      |

| Material Budget                                        | $0.07\%X_0\;{ m layer}^{-1}$                         |

| Silicon thickness                                      | $\leq 50  \mu m   layer^{-1}$                        |

| Radiation Load                                         |                                                      |

| NIEL                                                   | $1 \times 10^{13}  1 MeV  n_{eq}  cm^{-2}$           |

| TID                                                    | 10 kGy                                               |

| Environmental Conditions                               |                                                      |

| Target Operating Temperature                           | 15 °C to 30 °C                                       |

Table 1: General requirements for the ITS3 sensor [11].

in between the valence and conduction band (called band gap), where no energy states are available. At 0 K, all electrons reside in the valence band. By thermal excitation electrons can overcome this barrier and enter the conduction band. In this band, electrons move freely within the material, making it electrically conductive. Since the phenomenon of electrical conductivity of semiconductors is strongly dependent on the band gap, to control a material's electrical properties, one has to control and modify its band gap structure. This can be done by choosing different semiconductor alloys, or introducing impurities to the crystal (referred to as *doping*). In this way, additional energy states are created by introducing a dopant into the lattice. A dopant is typically an element with either one more or one less electron in its outermost electron shell than silicon. Atoms with excess electrons are called *donors*, while atoms with an electron deficit are called *acceptors*. Donors create energy states close to the conduction band, where electrons can easily be excited and delocalized. Acceptors cre-

Figure 2.2: Energy band structure of different types of solids

Figure 2.3: Silicon doping example with phosphorus (n-type) and boron (p-type)

ate extra states close to the valence band, attracting electrons from the neighboring valence bonds. Silicon doped with these elements forms what is called *n-type* and *p-type* semiconductors, respectively (See Figure 2.3). Equivalent to the movement of electrons in the conduction band, the vacancies left by excited electrons inside of the valence band can also propagate through the material – they appear to be moving and acting as positive charge carriers. This principle is why in semiconductor detectors, instead of electrons and ions, the free charge carriers are considered to be electrons and holes.

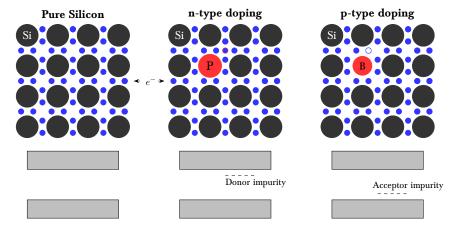

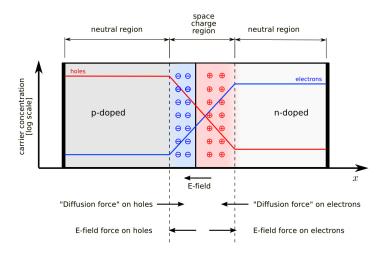

#### 2.2.1 The p-n junction

One important application of doping, which turns a regular semiconductor into an electronic device, is to bring differently doped materials into electrical contact, forming a p-n junction. The donor and acceptor doping concentrations  $N_D$  and  $N_A$  play an important role. When two semiconductors of different type (typically one p-type and one n-type, or an alternating combination thereof) are in contact, the difference in concentration of acceptors and donors will lead to a charge carrier diffusion against the concentration gradient. Electrons and holes recombine, creating what is called a depletion region around the junction. In this region, there are no free charge carriers. The recombination of electrons and holes results in the formation of an electric field E, arising from the positively charged donor ions and negatively charged

acceptor ions, which remain in the lattice. Any charge carrier in this region will experience the electric potential and be accelerated along the electric field lines towards either the p- or the n-side, counteracting the diffusion until an equilibrium is reached. The potential barrier, also called *junction potential* is given by [13]:

$$\Delta V = \frac{k_B T}{e} \ln \left( \frac{N_D N_A}{n_i^2} \right) \tag{2.1}$$

$k_B$ : Boltzmann constant =  $1.38 \times 10^{-23}$  J/K

T: medium temperature

e : elementary charge = 1.60  $\times$  10  $^{-19}\,\mathrm{C}$

$n_i$ : intrinsic charge carrier concentration

Figure 2.4: P-n junction of two semiconducters with opposite doping profiles [14]

Figure 2.4 illustrates this concept. By applying a voltage across the junction, this depletion region can be modified. For particle detection a *reverse-bias* voltage is typically applied, attracting even more electrons into the p-type and more holes into the n-type volume, effectively enlargening the depletion region. The reason for this, is that the depletion region represents the active detector volume – it is here, where incoming ionising radiation will leave traces of charge carriers, that will be accelerated by the electric field and ultimately collected and processed, resulting in the identification of a particle hit. Enlarging the depletion region means increasing the sensitive detection area of the sensor, since the depletion region will cover a larger fraction of the silicon volume. Furthermore, this increases the electric field strength, and therefore improves collection speed of the mobile charge carriers, leading to an increased time resolution.

If the reverse-bias voltage is too high, the junction will break down, and a current will start flowing. This is a result from the high electric fields liberating electrons out of the valence, and into the conduction band by quantum tunneling. These currents are usually tiny due to the relatively low probability of the tunneling process. However, if the electric field strength is high enough, these charge carriers are accelerated up to a point, where they themselves can free electron-hole pairs by colliding into them, creating an avalanche breakdown, potentially

causing permanent damage to the lattice. The voltage applied to thin, monolithic silicon pixel detectors therefore usually does not exceed around 5 V [15].

#### 2.2.2 Particle detection

Semiconductor detectors work on the principle of detection by ionisation. In the context of particle detection, ionisation is a process, in which a formerly neutral atom loses at least one electron, which will leave the atom electrically charged. When ionising radiation (such as X-rays, cosmic muons or some of the collision products at particle accelerators) enters matter, particles will electromagnetically interact and exchange momentum. As long as this momentum exchange is sufficiently high to overcome the specific ionisation threshold, it will cause the atoms to ionise. The reaction products of this interaction (usually a positively charged ion and a negatively charged electron) can be collected by applying an electric field across the traversed medium. This process can be used to measure the incident particles' energy loss and reconstruct its trajectory. To model the average energy loss by ionisation per unit path length of a traversing charged particle, the Bethe-Bloch equation [16] is used:

$$-\left\langle \frac{dE}{dx} \right\rangle = \frac{4\pi}{m_e c^2} \frac{N_A}{M_u} \left( \frac{e^2}{4\pi\varepsilon_0} \right)^2 \rho \frac{Z}{A} \frac{z^2}{\beta^2} \left[ \ln \left( \frac{2m_e c^2 \beta^2}{I(1-\beta^2)} \right) - \beta^2 \right]$$

(2.2)

with

$$\frac{4\pi}{m_ec^2}\frac{N_A}{M_u}\left(\frac{e^2}{4\pi\varepsilon_0}\right)^2=0.3071\,\mathrm{MeVcm^2/g}$$

$m_e$ : electron mass =  $9.109 \times 10^{-31}$  kg Z: atomic number of the absorbing material  $N_A$ : Avogadro's number =  $6.022 \times 10^{23}/\text{mol}$  A: atomic weight of the absorbing material  $M_u$ : Molar mass constant =  $1\,\text{g/mol}$  z: charge of the incident particle in units of e e: elementary charge =  $1.609 \times 10^{-19}\,\text{C}$  I: mean excitation potential  $\beta := v/c$  of the incident particle  $\beta := v/c$  of the incident particle  $\gamma := 1/\sqrt{1-\beta^2}$

The mean excitation energy describes the traversed material. It is usually inserted from accurate tables of I as a function of Z [17], however a very simplified approximation of the mean excitation energy has been given by Felix Bloch in 1933:

$$I \approx (10 \,\text{eV}) \cdot Z. \tag{2.3}$$

With the atomic number  $Z_{\rm Si}=14$  of silicon, this yields a mean excitation energy of 140 eV for silicon based semiconductor detectors. By modeling the energy loss of a traversing charged particle, it is possible to make assumptions about the number of liberated charge carriers, which is imperative for making design decisions before building a new detector. For example, according to Equation 2.2, a proton with 10 GeV momentum ( $\beta\gamma\approx 10$  loses about 550 eV/ $\mu$ m in silicon. For a 10  $\mu$ m thick sensor, this results in a mean energy loss of 5.5 keV. Considering a separation energy of 3.61 eV [18] for electron-hole pairs, this energy deposit corresponds to the liberation of approximately 1500 electron-hole pairs.

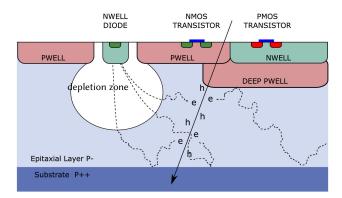

Typical MAPS are built from a highly doped p<sup>++4</sup>, a p<sup>-</sup> epitaxial layer, which functions as the active volume. They house p-type and n-type implants on top of the epitaxial layer, called PWELL and NWELL, respectively. The n-type implant acts as a collection diode, while the PWELLs shield the epitaxial layer from the on-chip circuitry, housed on top of the PWELLs (see Figure 2.5). When an ionizing particle traverses the depleted volume of the epitaxial

Figure 2.5: Geometrical cross-section of a MAPS pixel [19].

layer, it creates electron-hole pairs along its path, according to its mean energy loss (Equation 2.2). These pairs are initially assumed to be stationary, since their initial velocity is small compared to their drift velocity. Due to the higher concentration of carriers around the particle trajectory, they will then start diffusing isotropically<sup>5</sup>, until hitting one the p-type walls, recombining with a hole or entering the depletion region. Similarly to the p-n junction, the hole concentration difference between the p- epitaxial layer and the p++ substrate (or PWELLS) creates a potential difference, acting like a reflective wall to the electrons. Charge carrier recombination under the emission of a photon occurs only when an electron exactly matches the energy of a hole, and is therefore a rather rare process.

When electrons cross the boundary of the depletion region, the electric field will accelerate them towards the NWELL collection diode, where they will finally be collected. The charge carrier movement induces a current on the collection electrode according to the Shockley-Ramo theorem:

$$I_{\text{coll}} = E_v q v, \tag{2.4}$$

where q is the charge of the particle, v is its instantaneous velocity (or the drift velocity in silicon  $v_d \approx 5 \times 10^6$  cm/s [20]), and  $E_v$  the electric field component in the same direction. It is usually in the order of a few nA per electron.

$<sup>^4</sup>Light$  doping is denoted with a "-"-sign and refers to a donor concentration between  $1\times10^{14}\,cm^{-3}$  and  $1\times10^{16}\,cm^{-3}$ . Heavy doping is shown with a "+"-sign and usually refers to a concentration between  $1\times10^{18}\,cm^{-3}$  and  $1\times10^{20}\,cm^{-3}$ . Even higher concentrations are usually denoted by two "+"-signs.

<sup>&</sup>lt;sup>5</sup>Again, the small initial velocity of the electron-hole pairs is ignored.

The input capacitance is typically charged by a non-zero voltage  $V_{\text{reset}}$ . On charge collection, the capacitance is discharged by  $I_{\text{coll}}$ , causing a voltage drop of

$$\Delta V_{\text{signal}} = \frac{Q_e}{C_{\text{pixel}}}.$$

(2.5)

This voltage drop is then discriminated and compared to a user-defined threshold  $V_{\rm th}$  in the periphery. If  $V_{\rm signal} < V_{\rm th}$ , the sensor will register a particle hit. A reset current  $I_{\rm reset}$  drives the voltage on the collection diode and restores it back to  $V_{\rm reset}$ . The threshold value has to be tweaked in order to differentiate between noise on the collection diode, and an actual particle event, to ensure a low fake-hit rate (FHR) of the pixel.

Beyond this point, every MAPS will show slight differences in design paramters, such as pixel size, readout circuitry, collection diode geometry, epitaxial layer thickness, doping concentration etc. This is why a deeper look will now be taken into each of the prototypes that were investigated in this thesis.

#### 2.2.3 Applications in electronics

2.2

The broadest application for semiconductor devices is their usage within integrated circuits. A basic p-n-junction, as it is described in Section 2.2.1, forms a *diode*. A diode is the simplest form of an electronic semiconductor device, with the attribute of letting electrons flow mainly in one direction – from the n-type side to the p-type side.

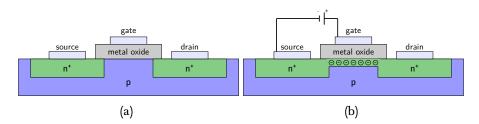

Figure 2.6: **(a)** Schematic cross section through an n-channel MOSFET in its off-state. No current can flow between the source and drain terminal. **(b)** When applying a voltage between the source and gate terminals, an n-channel with variable width will form, allowing electrons to flow from source to drain. The width of the n-channel determines the conductivity of the transistor, where higher gate voltages lead to wider channels and therefore higher conductivity.

A slightly more complex type of electronic device is the *transistor*. Transistors are the most frequently produced electronic devices, being used in any modern computer chip. The most widely used type of transistor is the MOSFET, which is fabricated by the controlled oxidation of silicon. They can be realized by combining two p-n junctions together into either a p-n-p (referred to as p-type metal-oxide-semiconductor (PMOS)) or an n-p-n (referred to as n-type metal-oxide-semiconductor (NMOS)) transistor. An example for a simple NMOS transistor is shown in Figure 2.6. In a logic circuit, its three terminals *source*, *gate* and *drain* are each

connected individually. The gate terminal is used to control current flowing between the source- and drain terminals. In its intrinsic state, the interface between n-type and p-type silicon will not allow any current to flow there (Figure 2.6 (a)). Applying any voltage between the source and the drain, will only enlarge the depletion region at either one of the n-type regions. If a positive voltage is applied between the source and the gate, electrons will be pulled towards the metal oxide insulator (Figure 2.6 (b)). Since these electrons cannot cross the insulator, this part of the transistor acts like a capacitor, trapping electrons between the two n-type materials. If the voltage is sufficiently high, the electrons form a channel between the source and the drain, through which current can flow. This type of transistor is also referred to as *enhancing*, since applying a voltage will increase its conductivity, as opposed to *depleting* transistors, where applying a voltage will increase their resistance instead. PMOS transistors function very similarly, with the polarity of the voltage between the source and the gate being reversed.

PMOS devices were the dominant semiconductor technology for integrated circuits between the late 1960s and early 1970s, but have been overtaken by NMOS devices shortly after. The reason for this is the difference in electron- and hole mobility. The electron mobility in an n-type channel of NMOS MOSFETs is about three times higher than the hole mobility in the p-type channel of PMOS MOSFETs. This allows for NMOS logic to achieve higher switching speeds, which is favourable in most applications, where their higher power consumption does not pose a problem. Logic consisting of complementary pairs of metal-oxide-semiconductor (MOS) transistors is called complementary metal-oxide-semiconductor (CMOS) logic. Since one transistor in the MOSFET pair of this combination is always off, it draws significantly less power than either PMOS or NMOS logic in its idle state, which is why CMOS technology has been the dominant MOSFET fabrication process for most integrated circuits since the 1980s.

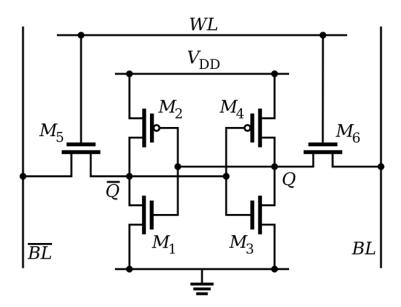

An imporant application for CMOS logic is the memory cell. Typically, it is made up of six MOSFETs and can be in one of two stable states, which are used to denote 0 and 1. An example memory cell is shown in Figure 2.7. As long as the two cross-coupled inverters formed by  $M_1-M_4$  are connected to the supply voltage  $V_{DD}$ , they will continue to reinforce each other and remain in their complementary state. When the word line (WL) is low, the access transistors  $M_5$  and  $M_6$  are turned off. If the PMOS transistor  $M_2$  is open, the potential on  $\overline{Q}$  is high, and Q is connected to ground. In principle<sup>6</sup>, the state can be read by asserting WL and measuring the voltage difference between BL and  $\overline{BL}$ . During a writing process, the bit lines have to be set to the desired state, and WL is pulsed, connecting Q and  $\overline{Q}$  to the bit lines, forcing their current logic state into the memory cell.

<sup>&</sup>lt;sup>6</sup>Because of parasitic capacitance between the bit lines the readout process is more complex, and requires precharging both bit lines before measuring the voltage drop that occurs when asserting the word line.

Figure 2.7: Typical 6T static random-access memory (SRAM) cell. Four transistors are used to form two cross-coupled inverters (M1 to M4) and two additional transistors are used for access during read and write operations (M5 and M6).

#### 2.3 The Analog Pixel Test Structure (APTS)

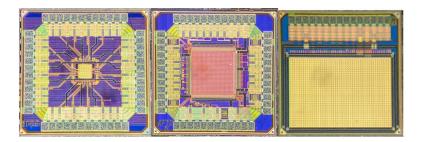

The APTS sensor is part of the Multi Layer Reticle 1 (MLR1), which was the first submission in the 65 nm TPSCo CMOS technology, dedicated to investigate its capabilities for the ITS3 upgrade. The MLR1 was produced in summer 2021, though the work around this thesis has only been carried out in summer 2023. Three major pixel sensors were designed for testing: The APTS, the CE65 and the DPTS. Each sensor was fabricated multiple times with varying pixel pitch, readout circuitry, implant geometry, and methods of amplification. A brief overview of the MLR1 sonsors is given in Figure 2.8. Since the APTS will be the main focus of this thesis, it will be presented in-depth in the following section. The DPTS features a matrix of  $32 \times 32$  pixels with a pitch of 15  $\mu$ m and a deep implant structure, with gaps in the low dose n-type implant. It is equipped with an amplifier and a discriminator, and provides time encoded digital readout. The CE65 is a larger sensor with a matrix of  $64 \times 32$  or  $48 \times 32$  pixels, with analog readout and a rolling shutter configuration. All three sensors have undergone an extensive characterization campaign, which was carried out both in laboratory and test beam environments [21].

#### 2.3.1 APTS chip architecture

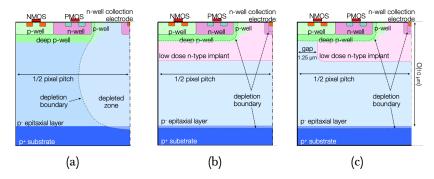

The APTS sensor features a matrix of  $6 \times 6$  pixels, with direct analogue readout of the inner  $4 \times 4$  submatrix. Its design purpose is the testing of the pixel cell and comparing process modifications. For this, the sensor was produced in three different flavours, as shown in Figure 2.9. For this thesis, only one kind of the APTS was used for testing. It has a pixel pitch

| Chip | # of dies / wafer | # of pixels                  | Pixel pitches: | 10 μm    | 15 μm    | 20 μm    | 25 μm        |

|------|-------------------|------------------------------|----------------|----------|----------|----------|--------------|

| APTS | 34                | $6 \times 6$                 |                | <b>✓</b> | <b>✓</b> | <b>✓</b> | $\checkmark$ |

| CE65 | 4                 | $64 \times 32, 48 \times 32$ |                | -        | <b>✓</b> | -        | <b>✓</b>     |

| DPTS | 3                 | $32 \times 32$               |                | -        | <b>✓</b> | -        | -            |

Figure 2.8: Photograph of the three main test sensors of the MLR1 run: (from left to right) the APTS, the Digital Pixel Test Structure (DPTS) and The Circuit Exploratoire 65 (CE65). All three chips measure  $1.5 \times 1.5 \text{ mm}^2$ . The table lists all different manufactured versions of each chip [11].

of 15 µm, a basic source follower structure for signal amplification, and an additional deep implant with gaps in between pixels, which results in reduced charge sharing when compared to other iterations of the chip [22]. This flavour of the APTS shows the most promising results in terms of signal charge collection, compared to the version without gaps [23]. The pixel pitch in the modified with gap version has no significant effect as charge sharing between individual pixels is strongly suppressed. In general, smaller pixel pitches have the advantage of a higher spatial resolution, with the drawback of higher power density, and therefore heat generation. Another important effect of the pixel pitch is the charge collection efficiency. Its dependence on the pixel pitch is only relevant for the standard flavour of the APTS, as there, charge sharing is not suppressed. Larger pixel pitches will increase the charge transport path and together with the expected smaller relative lateral extension of the depletion region, will result in lower charge collection efficiency towards larger pixel pitches. In the modified with gap version, the charge collection efficiency is close to 100 % for all four pixel pitches. This is because the field induced by the gap counteracts charge sharing. In fact, the smaller relative size of the gap increases the charge collection efficiency slightly for larger pixel pitches [22]. This trend is not infinitely scalable, as fully depleting large pixels becomes increasingly more difficult.

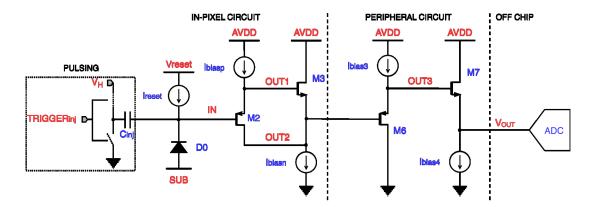

The on-pixel circuit layout of the relevant APTS sensor is shown in Figure 2.10. The sensor is controlled via a voltage Digital-to-Analog Converter (DAC)  $V_{\text{reset}}$  and five current DACs:  $I_{\text{reset}}$ ,  $I_{\text{bias}}$ ,  $I_{\text{bias}}$  and  $I_{\text{bias}}$ . Additionally, an external back bias voltage  $V_{\text{BB}}$  can be applied to the substrate, as well as the bulk of the NMOS transistors (PWELL) in each pixel, to increase the size of the depleted region. The source follower version of the APTS gets its name from its M2 transistor. It acts as a voltage buffer for the incoming signal from the

Figure 2.9: Three different sensor flavours: (a) standard, (b) additional low dose implant and (c) additional low dose implant with a gap at the pixel borders (referred to as *deep implant with gaps*) [22].

Figure 2.10: Schematics of the APTS pixel circuitry [22]

collection diode. A second source follower stage (M3) is used to further reduce the capacitive load on the collection diode. The signal is then transmitted to an off-chip ADC.

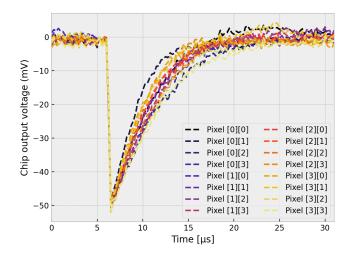

The collection diode is biased and reset using a constant current mechanism. In its initial state, the  $I_{\rm reset}$  current only compensates for leakage currents, and the voltage on the collection diode is sitting close to its reset potential  $V_{\rm reset}$ . After a particle hit, the current source delivers the constant current  $I_{\rm reset}$ , discharging the collection electrode and driving the gate potential of the M2 transistor back to  $V_{\rm reset}$ . For various test purposes, an injection capacitance  $C_{\rm inj}=242\,{\rm aF}$  is used to inject a variable charge pulse onto the signal line. The pulse height is controlled via the voltage DAC  $V_{\rm H}$ . Figure 2.11 provides a visualization of the signal obtained from injecting charge via the pulsing capacitance  $C_{\rm inj}$  for each of the 16 pixels. The reference voltage has been standardized to 0 V. Small fluctuations between pixels can arise due to noise and slight pixel variation during manufacturing, leading to different reset currents across the pixels. After about 10  $\mu$ s, all pixels have restored their initial state.

Figure 2.11: Signal shape distribution after charge injections across the 16 pixels of the APTS. The pixel coordinates are indicated as row and column.

#### 2.3.2 Readout

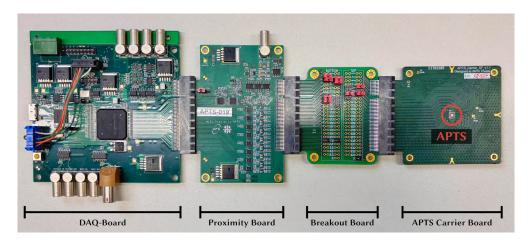

Figure 2.12: Experimental setup of the APTS featuring (from left to right): A Data Acquisition (DAQ) board, a proximity board, a breakout board (optional), and a carrier board, interfacing the sensor.

Figure 2.12 shows the main components of the APTS laboratory setup. The DAQ board is the primary interface between sensor and PC. It is responsible for reading and buffering data, as well as steering sensor (DAC) parameters via an integrated Field Programmable Gate Array (FPGA). Furthermore, it features voltage regulators including current monitoring circuitry, to supply the on-board chip circuitry and proximity card, as well as a temperature measurement circuit. A reverse bias voltage can be applied via an on-board LEMO connector. To trigger the sensor the DAQ board can either generate a trigger based on the chip output, or receive

an external trigger input via another dedicated LEMO connector. While data acquisition is in progress, a busy signal is generated to avoid multiple trigger inputs during the same data event. The board is designed to provide universal functionality to all MLR1 and Engineering Run 1 (ER1) sensors, as well as the well-established ALPIDE sensor.

To adapt to the specific chip type, a proximity card converts supply and steering voltage levels and bias currents from the DAQ board to the corresponding sensor standards. This is also, where the analog information, coming from the APTS is converted into digital information. For this, the proximity card contains Analog-to-Digital Converters (ADCs) to digitize the 16 analog outputs with a resolution of 16 bit and a sample rate of 4 mega-samples per second (MS/s) (corresponding to a sampling period of 250 ns). The breakout board is an optional interface which can be used in between any slot, to gain easy access to all of the 98 lines of the PCI express connector. The carrier board acts as an electronic interface to the sensor, which is wiredbonded and glued in its center. It is also equipped with additional electronic components, that act as a low pass filter which helps to reduce electronic noise. The filter behaviour of the carrier board specifically will be investigated in subsection 3.3.

The APTS sensor is one of the few test sensors of the ITS3 project, where full access to the analog domain is possible. To measure the pixel output voltage  $V_{\rm out}$ , a buffer has been implemented into the FPGA on the , that continuously stores the analog information of the sensor. When a read request signal is sent to the APTS, snapshot of 200 time frames of  $V_{\rm out}$  (corresponding to a measurement of 50  $\mu$ s) is sent to the digital endpoint of the sensor, and then read out via the on-board USB controller. This is long enough to contain the full rise (1  $\mu$ s) and decay ( $\approx$  10  $\mu$ s) of a signal originating from a particle event, such that a full analysis on the analog information of the pixel output can be performed.

#### 2.4 The Monolithic Stitched Sensor (MOSS)

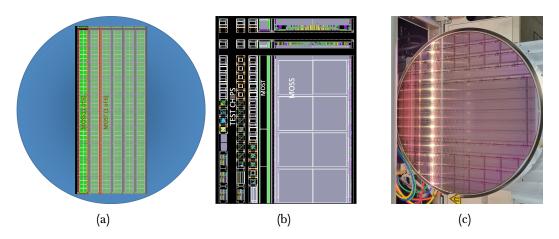

The following section is concerned with sensors of the ER1. The final goal is to replace flat single reticle sensors with wafer-scale stitched sensors. For this, two large stiched sensors, the MOSS and the Monolithic Stitched Sensor Timing (MOST) have been designed and submitted in 2022, together with many smaller test chiplets. The ER1 submission is shown in Figure 2.13. This work performed in the scope of this thesis solely focuses on the MOSS. 24 wafers have been produced in two splits, and all sensors are currently undergoing laboratory tests (further explained in Section 4.1). The sensors are named according to the wafer they originate from. For example, one of the sensors used from the first split, namely MOSS-2\_WO2F4, is named after its chip number 2 (from 1 to 6, directly corresponding to its position on the wafer), wafer WO2 and wafer suffix F4.

#### 2.4.1 Sensor design

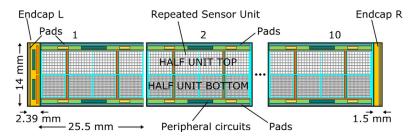

The MOSS is the first iteration of a wafer-scale pixel sensor, consisting of 10 repeated sensor units (RSUs), which is the largest individual sensor that can fit in the design reticle. Stitched

Figure 2.13: The ER1 submission: (a) conceptual drawing of the Engineering Run (ER) wafer, containing the two sensors MOSS and MOST, (b) the reticle, making up one repeated sensor unit and (c) A photo of the ER1 pad wafer.

together they form a sensor with an active area of nearly  $^7$   $1.4 \times 25.9\,\mathrm{cm}^2$ . Each RSU is composed of two half-units (HUs) labeled *top* and *bottom*, which themselves contain four matrices, reffered to as *regions*, with a pixel pitch of 22.5 µm for the top region ( $256 \times 256$  pixels), and a pixel pitch of  $18\,\mathrm{\mu m}$  for the bottom region ( $320 \times 320$  pixels). Some of the regions are made from slightly different front-end variants (see Table 2). Since both top and bottom regions feature almost the same pixel circuit, they differ only in component density – and therefore power density. The analog power density is  $7\,\mathrm{mW/cm^2}$  for the top matrix, and

Figure 2.14: Concept diagram of the MOSS chip.

$11\,\mathrm{mW/cm^2}$  for the bottom matrix [24]. Each HU is a fully standalone functional unit with independent periphery, readout and powering. This makes it possible to supply RSUs via pads from the long edge, or via pads from the end-caps, making use of the interconnecting metal lines, which traverse the entire sensor from left to right. Since each HU can be tested independently, this allowes studying their yield and its possible dependence on the density of circuits.

<sup>&</sup>lt;sup>7</sup>The actual active area is slightly smaller due to the reticle design, which also includes some dead area for readout periphery.

|        | Region 0 | Region 1                        | Region 2                                            | Region 3                                 |

|--------|----------|---------------------------------|-----------------------------------------------------|------------------------------------------|

| ТОР    | Standard | Larger input<br>transistor (MI) | Larger discrimina-<br>tor input transistor<br>(M11) | Larger common-<br>source transistor (M2) |

| BOTTOM | Standard | Standard                        | Standard                                            | Slightly different layout                |

Table 2: Different front-end variants for the eight regions on a MOSS RSU.

#### 2.4.2 Readout

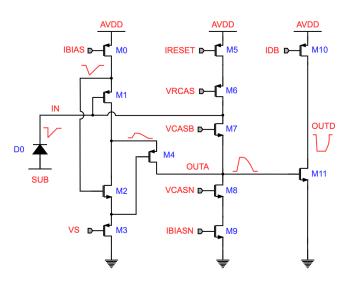

Figure 2.15: Simplified schematic of the MOSS analog pixel front-end

The analog in-pixel front-end of MOSS is adapted from the DPTS and is illustrated in Figure 2.15. It is mainly controlled via its four current DACs ( $I_{\rm BIAS}$ ,  $I_{\rm RESET}$ ,  $I_{\rm BIASN}$  and  $I_{\rm DB}$ ) and its three voltage DACs ( $V_{\rm S}$ ,  $V_{\rm VCASB}$  and  $V_{\rm CASN}$ ). Additionally, a pulsing voltage  $V_{\rm PULSEH}$  can be set (similarly to  $V_{\rm H}$  for the APTS) for injecting charge into the analogue in-pixel front end with an injection capacitance  $C_{\rm inj}=258\,{\rm aF}$  to investigate the sensor response. Also like with the APTS, an external bias voltage can be applied to the substrate in order to increase the size of the depletion region. If no back-bias voltage is applied, a shunt resistor (0  $\Omega$ ) is instead used to avoid potential buildup. The initial signal is first processed by the transistor network M1-M9, where its inverted and amplified. The  $I_{\rm RESET}$  current drives the signal line back to its operational potential of 1.2 V. At transistors M10 and M11 it is then discriminated against a threshold and sent to the periphery.

The MOSS features a synchronous serial protocol for communication. Both powering and communication via the long edge and the left end cap is possible. Its address space consists of 12 bits, giving access to all relevant functions and registers. This leaves 512 registers for each

region and 2048 registers for the periphery. Data is transferred for each half unit separately via a slow control interface. Readout happens as a stream of bytes and is sequential for each region. It is possible, however, to exclude single regions from readout, which is important for the case where one of them is not functional, which would prohibit readout of the entire HU. Due to bandwidth limitations of the test system each region is assigned a maximum packet size of 2 MiB for readout over the long edge. For the firsts tests, readout and powering will solely be done via the long edge, allowing for the simplest power distribution scheme and higher bandwidth.

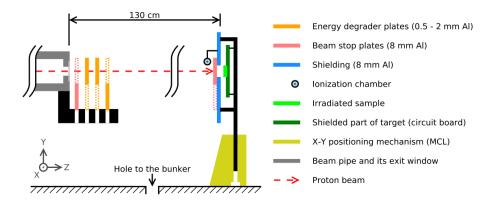

#### 2.4.3 MOSS Experimental Setup

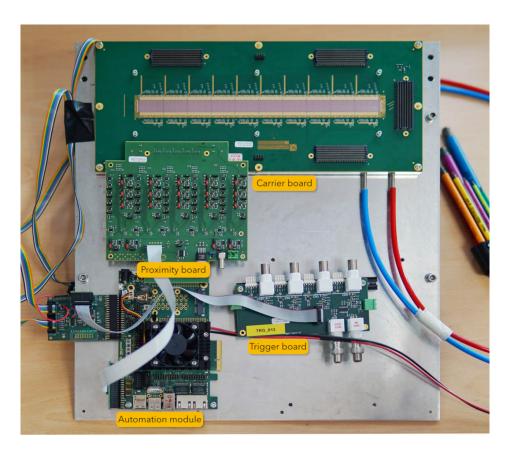

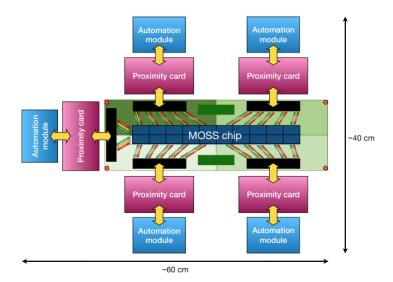

Figure 2.16: MOSS sensor on top of a carrier board, connected to a proximity card and an automation module. A trigger board is also connected supplying external trigger inputs which is used in conjunction with a scintillator trigger system during testbeam campaigns.

The MOSS test system consists of the sensor hosted on a carrier board, which features five individual 560-pin connectors along its perimeter for readout. Each slot connects to a proximity card, which itself is steered by an automation module (see Figure 2.16). Four of the five interfaces serve for the readout of the long edge, and therefore can only read out five of the HUs at once, while the side interface can read out the entire MOSS sensor at once over

Figure 2.17: Concept for the test system.

the short edge. So far, only the readout over the long edge has been tested, such that in a full-readout setting, there are a total of eight boards (four proximity-, and four automation boards) connected at the same time. While reading out all units at once is technically possible and has been tested in the laboratory, due to the sheer size of the sensor, only one of the interfaces is used during a standard beam test, to keep the size of the setup manageable and accessible. A conceptual illustration of the full test system is shown in Figure 2.17.

#### 2.5 The BabyMOSS test system

Since fitting a maximum of six individual MOSS onto a circular wafer leaves a lot the wafer surface area unused, both its top the bottom sections are utilised for the production of a smaller scale test system – the *BabyMOSS*. In this way, for each six MOSS in production, 23 BabyMOSS are also fabricated, which can be used to study basic functionality and performance of the individual regions of the chip. Several institutes outside of CERN are involved in this effort, and participate in a wide research programme consisting of (but not limited to) power and readout tests, efficiency and noise studies, irradiation studies, etc. Since both MOSS and BabyMOSS carry the same design architecture and analog front-end.

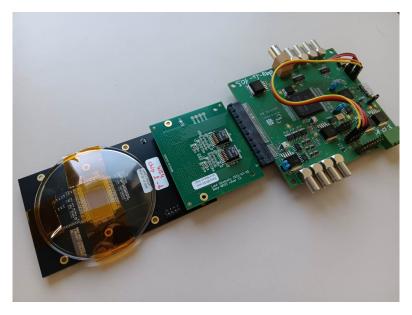

#### 2.5.1 BabyMOSS Experimental Setup

While the MOSS is operated within its own DAQ infrastructure, an important advantage of the BabyMOSS is its ability to be operated with the same DAQ board as the APTS. Aside from its portability, this makes BabyMOSS the perfect prototype to be distributed amongst all the various institutes outside of CERN, which regularly participate in and contribute to the ITS3 research and development efforts. Figure 2.18 shows the BabyMOSS test system. The leftmost component is the BabyMOSS carrier card. It interfaces the sensor, and contains four

negative temperature coefficient thermistor (NTC) temperature sensors<sup>8</sup>, situated close to the BabyMOSS. The middle component is the raiser board. Its purpose is to convert supply and steering voltage levels and bias currents from the DAQ board to the BabyMOSS standard. It also contains test points for the analog and digital domain on the chip, that can be used to supply voltage to the NTC. Finally, on the right side, the same DAQ-board as used for the APTS is connected.

Figure 2.18: BabyMOSS test system featuring (from left to right) the BabyMOSS carrier card interfacing the sensor, a raiser board, and a DAQ-board.

Sensor tests performed with this test system include, but are not limited to: Fake-hit rate tests, threshold tests, single-event effect studies and irradiation studies. More on these tests can be found in section 4.

# 3 APTS characterization and noise studies

In the following chapter, an explanation of the basic operation and analysis procedure of the APTS is provided. The sensor performance is investigated under different conditions concerning the influence of electronic noise in the environment. There are several important steps to be performed before the data can be correctly evaluated. This includes a full gainand energy calibration of the test system, translating arbitrary readout values into physical quantities. Both the gain- and the energy calibration are explained in more detail below.

<sup>&</sup>lt;sup>8</sup>An NTC acts as a temperature dependent resistor. To measure a temperature, a reference voltage is applied to the NTC, and the current is measured. Higher temperatures reduce its resistance, resulting in higher current flow.

3.1 Gain calibration 3 APTS

#### 3.1 Gain calibration

| Parameter          | Min. | Тур. | Max.  | Unit |

|--------------------|------|------|-------|------|

| Operating Temp.    | -40  | 27   | 85    | °C   |

| Power Voltage AVDD |      | 1.2  |       | V    |

| IBIASP             |      | 80   | 100   | uA   |

| IBIASN             |      | -800 | -1000 | uA   |

| IRESET             | 0.1  | 1    | 1     | uA   |

| IBIAS3             |      | 800  | 1000  | uA   |

| IBIAS4             |      | -6   | -8    | mA   |

| VRESET             | 200  | 500  | 800   | mV   |

Table 3: Recommended operating conditions for the APTS

In its running state, the APTS continuously measures and stores the value of its pixel output voltage once every 250 ns. When an ionizing particle deposits enough energy in the epitaxial layer of the sensor, the collected charge overcomes the user-defined threshold and a snapshot of 200 time frames of the signal, (corresponding to  $50 \,\mu s$ ) will be stored inside of a multi-event buffer, where it can then finally be read out via USB. At this time, the signal amplitude is

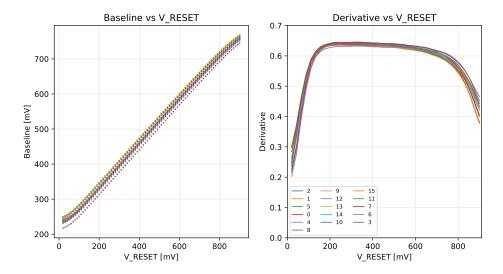

Figure 3.1: Gain calibration plots for all 16 pixels: Mapping the VRESET parameter in DAC unit to the  $V_{\rm reset}$  voltage in mV (left), and the function derivative (right), which helps to determine the linear regime.

sampled in so called *DAC units*, providing a partly discretised approximation of the real pixel voltage. This unit can take values from 0 to  $2^{16} - 1$  (16-Bit), which covers the entire dynamic range of the sensor. To translate it into a physical quantity (i.e. voltage), a *gain calibration* of

the sensor needs to be performed. During a gain calibration scan, the source voltage on the readout transistor M0 (see Figure 2.10) is repeatedly measured while the VRESET parameter is steadily increased. VRESET determines the baseline voltage to which the pixel will return to after charge injection. The result is then used to convert from DAC to mV. Around the nominal working point (see Table 3) the relation between the baseline voltage and VRESET is approximately linear, making it possible to convert between them with a single calibration factor. Only in this linear regime, it is ensured that the calibration factor can accurately describe the gain, and the sensor should only be operated here, otherwise the error of the energy calibration could increase significantly.

An example gain calibration curve is shown in Figure 3.1. Not only is the gain calibration necessary to quantify the signal, but it also gives an insight on sensor-to-sensor and pixel-to-pixel variation, which can arise from slight production differences or pixel damage.

### 3.2 Energy calibration

Figure 3.2: Experimental setup of an Fe-55 measurement for the energy calibration of the APTS.

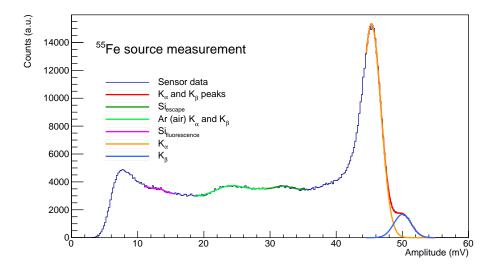

For the final calibration of the APTS, the pixel signal amplitude is related to the energy deposit in the epitaxial layer in an energy calibration. For this, a reproducible particle event with a well-known energy has to be utilised. One example for this are X-Rays from the K-line of an  $^{55}\text{Fe}$  decay. When  $^{55}\text{Fe}$  decays into  $^{55}\text{Mn}$  via the capture of one of its inner shell electrons, the vacancy is filled with an electron of its outer shells, resulting in the emission of X-Rays with characteristic energies (see Table 4). Due to the high photoelectric absorbtion coefficient of silicon for 6 keV X-rays of  $\mu=1.46\times10^2\,\text{cm}^2/\text{g}$  [25], most of these photons are fully absorbed within the sensor. The resulting energy deposit will lead to the production of around 1630 (in the case of  $K_\alpha{}^9$ ) and 1800 (in the case of  $K_\beta$ ) electron-hole pairs [18], which lies comfortably within the dynamic range of the sensor. This knowledge can be used to identify a relationship between the signal peak position and energy deposit inside the pixel. To verify

<sup>&</sup>lt;sup>9</sup>The  $K_{\alpha}$  line actually shows a substructure of two lines:  $K_{\alpha_1}$  and  $K_{\alpha_2}$ . This is due to the spin characteristics of the L-shell electrons. These lines are very similar, and are therefore often treated as mono-energetic, which is sufficient for an experiment with an energy resolution similar to the APTS

Figure 3.3: <sup>55</sup>Fe-Spectrum measured with the APTS without back-bias voltage applied. The spectrum is filled with the seed signals of the 4 central pixels. The background consists mostly from Auger electrons and bremsstrahlung.

the linearity of this relationship, the position of the silicon escape-, silicon fluorescence, and argon  $K_{\alpha}$  peaks are also added to the curve. A fluorescence X-ray is emitted, when a K-shell electron of a silicon atom is liberated by the incoming photon, followed by the transition of an L-shell electron into the vacancy. If this X-ray escapes the sensor, the detected energy will decrease by 1.74 keV, resulting in the silicon escape peak at an energy of around 4.16 keV. The argon X-Rays result from photon-electron interactions with atmospheric argon.

| Name                          | Energy       | Unit |

|-------------------------------|--------------|------|

| $^{55}$ Fe K $_{lpha_1}$      | 5.89875 [26] | keV  |

| 55 <b>F. K</b>                | 5.88765 [26] | keV  |

| $^{55}$ Fe K $_{eta}$         | 6.49045 [26] | keV  |

| $^{-40}$ Ar K $_{lpha_1}$     | 2.95778 [27] | keV  |

| $^{40}$ Ar K $_{lpha_2}$      | 2.95571 [27] | keV  |

| <sup>28</sup> Si Fluorescence | 1.74 [28]    | keV  |

| <sup>28</sup> Si Escape       | 4.16         | keV  |

Table 4: Characteristic X-Rays of various elements used in the APTS energy calibration.

An example of an <sup>55</sup>Fe energy spectrum taken for the seed signal with a cluster size of up to four can be found in Figure 3.3. A cluster is defined as a three by three matrix of pixels centered around the pixel with the highest signal amplitude (the *seed* pixel), which have collected enough charge to overcome the threshold. For the analysis, only those clusters are

considered, which have a seed pixel in the center 4 pixels of the APTS matrix (in order to have access to all pixels in the cluster). The amplitudes of individual pixel signals of a cluster are then summed and included in the spectrum. All five peaks can generally be approximated with a Gaussian:

$$A \cdot \exp\left(\frac{-\left(x-\mu\right)^2}{2\sigma^2}\right) \tag{3.1}$$

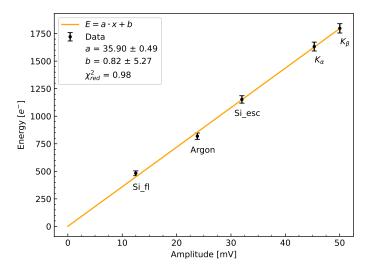

Figure 3.4: **(b)** The energy calibration of the APTS shows the amplitude of the seed pixel signal as a function of the photon energy.

However, since the peaks of K  $_{\alpha}$  and K  $_{\beta}$  are so close together, actually the sum of two Gaussians is used as a fit function. For the fluorescence and escape peaks, a linear polynomial is added to consider the relatively large background, which results from Bremsstrahlung and Auger electrons originating from the K or L shell:

$$A \cdot \exp\left(\frac{-\left(x-\mu\right)^2}{2\sigma^2}\right) + ax + b \tag{3.2}$$

The mean energies then contribute to the energy calibration (Figure 3.4). For each data point, a poisson error is assumed, since the number of charge carriers produced in each particle event follows a poisson distribution. The numerical fit uncertainty is negligibly small. Using this fit, an energy conversion factor can be calculated, which for the sensor operation without back-bias computes to

$$a = 35.9 \pm 0.5 \,\mathrm{e}^{-}/\mathrm{mV}.$$

(3.3)

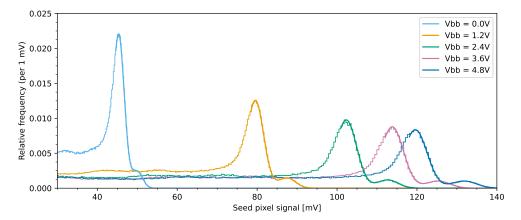

Figure 3.5: Seed signal amplitude distribution for different reverse bias voltages

Figure 3.5 shows an example for an energy calibration for different reverse bias voltages applied across the collection diode. The amplitude increases with increasing bias voltage. This is due to the increased size of the depletion region and the resulting reduced pixel input capacitance. The junction capacitance is similar to a parallel plate capacitor:

$$C = \frac{Q}{V} = \frac{n_{e^-} \cdot q_{e^-}}{V_{\text{Mn-K}_{\alpha}}}$$

(3.4)

where  $n_{\rm e^-}$  is 1632 electrons<sup>10</sup>,  $q_e^-$  the elementary charge and  $V_{\rm Mn-K_{\alpha}}$  comes from the respective fit parameters (i.e. the peak position  $\mu_{\rm Mn-K_{\alpha}}$ ) for different back-bias voltages. From this, we get a sensor capacitance for each back-bias voltage:

| Back-bias voltage [V] | Capacitance [fF] | Electron conversion factor [electron/mV] |

|-----------------------|------------------|------------------------------------------|

| 0.0                   | 5.76             | 36.0                                     |

| 1.2                   | 3.28             | 20.5                                     |

| 2.4                   | 2.55             | 15.9                                     |

| 3.6                   | 2.29             | 14.3                                     |

| 4.8                   | 2.18             | 13.6                                     |

Table 5: Measured sensor capacitance for different back-bias voltage settings

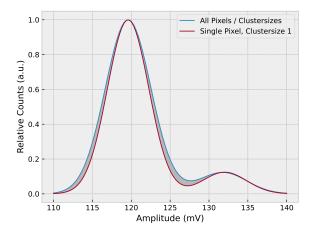

Operating with a higher back-bias and therefore reduced capacitance reduces the noise level significantly, allowing lower thresholds, and an improved signal-to-noise ratio (SNR). From the width of the  $K_{\alpha}$  peak, the operational energy resolution can be obtained:

$$R_E = \frac{\text{FWHM (Mn-K}_{\alpha})}{V_{\text{Mn-K}_{\alpha}}} \approx \frac{2.355\sigma}{\mu}$$

(3.5)

$<sup>^{10}\</sup>mbox{Based}$  on an electron- hole pair separation energy of 3.61 eV for silicon at 300 K [18]

For the APTS, this value computes to 7.4% for a bias voltage of 0 V and  $\approx$  6% for all voltages of 1.2 V or higher. To increase the energy resolution, a cut can be performed on the cluster size, such that only events with a cluster size of one are considered. Apart from this cut, each pixel can be evaluated individually for its energy resolution, such that pixel-to-pixel variation does not lead to an increased width, when their counts are summed up. This improves the energy resolution to 7.2% for 0V and 5.2% for all voltages of 1.2 V or higher. This is because the seed signal for events of cluster size of one generally have a higher SNR than the signal for events with cluster size > 1. This leads to a reduced fake-hit rate, and finally a slightly better pronounced peak in comparison.

Figure 3.6: Qualitative comparison of the Mn- $K_{\alpha}$  and  $-K_{\beta}$  peaks using different analysis methods: The blue curve corresponds to the summing of all signals within a cluster, while the red curve shows the response of a single pixel, filtering all events with a cluster size higher than 1. For visual clarity, only the final fit function is shown in this graph.

The best achievable energy resolution for this sensor has been found to be 4% in [22], using a much lower reset current, a temperature-controlled environment and a high-sampling-rate oscilloscope.

#### 3.3 Electronic noise on the APTS

One goal of this thesis is to investigate the effect of external electronic noise on the APTS performance. In order to understand the following section, a brief introduction to the analysis of electronic noise is given.

#### 3.3.1 Electronic noise

The most important factor to quantify a detectors performance in regard to electronic noise is its signal-to-noise ratio (SNR). It describes the ability of a data acquisition system to distinguish a useful information signal suffering from undesired random disturbances. These disturbances are a result of unwanted energy from various sources, some of which is unavoidable, like thermal noise, and some of which can be attenuated, like noise stemming from electronic devices.

To calculate the SNR, both, signal and noise power must be measured at the same or equivalent points in an electronic circuit with the same bandwidth:

$$SNR = \frac{P_{\text{signal}}}{P_{\text{noise}}} \tag{3.6}$$

This notation of signal power is not the same as the conventional notion of power in physics, but one can convert between the two by taking into account the characteristic impedance of the signal transmission line. However since this quantity is unknown to us, and will cancel out for each individual measurement, it suffices to simply look at the signal power in terms of its root mean square (RMS) amplitude:

$$P_{\text{signal}} = V_{\text{RMS}}^2 \tag{3.7}$$

The SNR then equates to

$$SNR = \frac{V_{RMS, Signal}^2}{V_{RMS, Noise}^2}.$$

(3.8)

Since this definition is rather general, it can only describe the ratio of the RMS voltage of the desired signal to the RMS voltage of the noise, that is also present (i.e. for a known bandwidth and center frequency). If the signal can be represented by constant value (for example a maximum amplitude s), and the noise fluctuates around a mean voltage of 0, this equation then simplifies to

$$SNR = \frac{s^2}{\sigma_N^2}. (3.9)$$

Signals measured with the APTS, are simply an array of values, each describing a single voltage measurement within a 250 ns time frame. The noise standard deviation is calculated from a subset of 50 time frames before the signal reaches its maximum amplitude. This subset contains values only associated with the baseline noise, and its duration is chosen as such, that it is comparable to the duration the voltage needs to return to baseline from the maximum signal amplitude under normal oprating conditions (as seen in Figure 2.11).

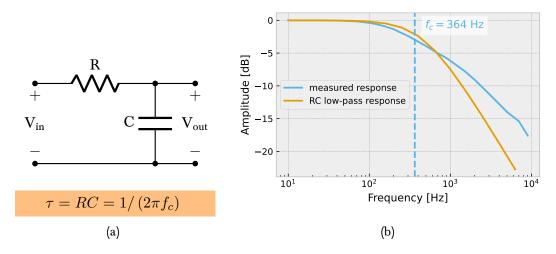

Figure 3.7: (a) Schematics and characterization of a simple RC low-pass filter. (b) Frequency Response of the capacitor network on the APTS carrier card next to the frequency response of a simple low-pass filter with the same time constant.

#### 3.3.2 APTS noise attenuation

The APTS carrier board contains a network of capacitors, which decouple the analog domain of the chip from ground, while additionally acting as a low-pass filter. This has been chosen to reduce electronic noise on the signal line. A low-pass filter can be characterized by its time constant  $\tau$  and cutoff frequency  $f_c$ . For a first order RC low-pass filter, the time constant and cutoff frequency are related in the following way:

$$\tau = RC = \frac{1}{2\pi f_c} \iff f_c = \frac{1}{2\pi RC} = \frac{1}{2\pi \tau} \tag{3.10}$$

To measure the frequency response of a filter network, a constant amplitude sinusoid is applied at the input node, which is then stepped through a range of frequencies, and compared to the amplitude of the signal at the output node. For this measurement a sine signal was injected to the LEMO input connector responsible for applying  $V_{\rm BB}$  (i.e. into the PWELL), and the amplitude has been measured at PWELL test point on the APTS carrier card. To measure the time constant of the APTS filter network, a square wave of 1 kHz was injected into the PWELL. The time constant can then simply be obtained by measuring the time the signal needs to reach 1/e=63.2% of its peak value at the test point. Both the positive and negative voltage domain has been measured, and yielded near identical results. Only signals with an amplitude of up to  $100\,{\rm mV_{pp}}$  have been injected, in order not to create high positive currents on the PWELL, which could potentially cause irreversible damage to the pixels.

The time constant of the APTS filter is measured to be around  $340.3 \pm 13.0 \,\mu s$ . Its frequency response is slightly less steep than the frequency response of a first order RC low-pass filter with the same time constant (see Figure 3.7). The actual cutoff frequency, i.e. the frequency at which the injected signal is reduced to  $-3 \, dB = 1/\sqrt{2}$  was measured to be around 364 Hz.

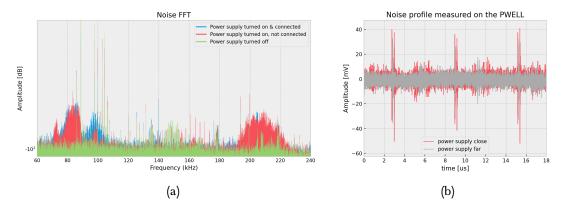

Figure 3.8: (a) Fast Fourier-Transform of the measured PWELL-noise profile. When turning on the power supply, two new bands at  $\approx 80$  and 200 kHz become apparent. When connected, another band at 100 kHz appears. (b) Comparison of the noise profile measured on the PWELL between a best-case and a worst-case scenario.

All measurements were obtained by using the automatic measurement functionality of a Tektronix MDO3024 oscilloscope. For the frequency response, each point was measured for a few seconds, until the reading on the oscilloscope stabilised. The time constant error results from the oscilloscope's calculated standard deviation of the mean.

A direct product of the APTS filter is the chip's indifference to various noise sources in the environment. During this study, one of the biggest unavoidable noise sources has been identified to be the HAMEG power supply, providing DC power to the DAQ-board, as well as a DC voltage between 0 and  $4.8\,\mathrm{V}$  for the reverse bias. When turned on, the power supplies' electronic components will produce a  $100-200\,\mathrm{kHz}$  switching noise, which is visible on the PWELL (see Figure 3.8). For this, the power supply does not need to be connected to the DAQ-board, but instead a big portion of the noise is actually transmitted through the air due to electromagnetic radiation being picked up by the APTS electronic lines. Since the power supply is needed to operate the APTS, its influence can not be completely avoided. However, to test the effect of the power supply noise, a best-case and a worst-case scenario have been simulated, by varying the distance between the power supply and the carrier board. Compared to the best-case (where the power supply is well isolated from the system), in the worst case (where the setup sits right next to the power supply) the noise power measured on the PWELL is increased by around 40% (See Figure 3.8 (b)).

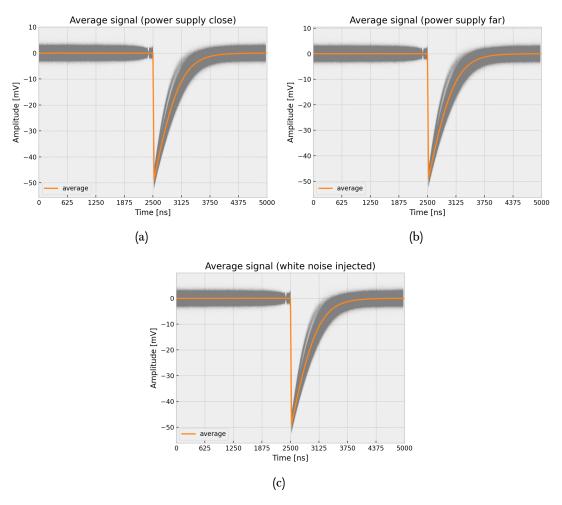

To test whether this noise has any influence on the APTS performance, 1000 signals have been injected to the pixel front end via the injection capacitance. The resulting signals have been recorded and overlayed in an amplitude-over-time diagram. From all these samples, the baseline noise  $\sigma_N$  as well as the SNR is calculated and averaged over all pixels and events. Visually, there was no difference between any of the three measurements. In general, the variation between signals is an order 100 higher than the differences between the average

signal of each measurement, which is only around 0.1 mV. The consequent wave forms of this test are shown in Figure 3.9. From the 1000 signal injections we calculate the average SNR to be  $1239\pm71$ . Simulating a worst-case scenario, where the noisy power supply is sitting right next to the circuit board, yields a similar signal-to noise ratio of  $1246\pm72$ . To test the filter capabilities, a  $100\,\mathrm{mV_{pp}}$  signal consisting of white noise was injected directly into the PWELL via an external function generator. This also had no significant effect on the signal, yielding a SNR of  $1243\pm71$ . The error on the SNR is calculated from the standard deviation of the mean of the 1000 samples.

Figure 3.9: Comparison between the APTS signal injection. (a) APTS signal where the power supply is isolated as well as possible (minimum operation noise). (b) APTS position right next to the power supply, where the RF pickup is strongest. (c)  $100\,\mathrm{mV_{pp}}$  of white noise is injected onto the PWELL.

# 4 MOSS and BabyMOSS studies

The following sections will describe the work performed within the scope of this thesis, with focus on the specific contributions to the MOSS and BabyMOSS characterization campaign. Any work described in the following was performed in collaboration and with guidance from CERN, and under the supervision of the ALICE ITS3 upgrade project. The results of this work have been presented at various internal meetings and parts of them will be published in the near future within technical reports, conference proceedings, or journal articles.

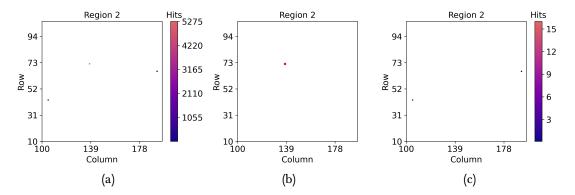

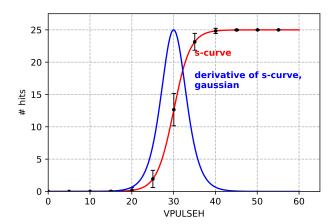

## 4.1 Laboratory tests and sensor scans

The MOSS and BabyMOSS sensors all undergo the same initial characterization process, where the chips are tested for power draw<sup>11</sup>, functional defects, readout defects etc. Since in the scope of this thesis these scans have mainly been performed with the BabyMOSS test system, they will also be described in the following section with the BabyMOSS in mind. For the MOSS, they are equivalent with the only difference being the jkreadout system, and the scan order and complexity, since for each MOSS ten RSUs have to be characterized. The basic testing pipeline for each sensor consists of eight scans:

- A power-on scan, where both half units of the sensor are powered on and the reset current is established. The scan monitors three supply currents AVDD, DVDD and IOVDD for the analogue domain, the digital domain, and the readout, respectively. In case of a physical defect of the sensor, these can hint to a low-impedance path. If they overcome a threshold of 100 mA (which is enough to ensure functionality of the chip, without heating up any of the components), the sensor is turned off and the scan returns as failed. The sensor can then be put aside for some further investigation of the issue.

- Should the power-on scan succeed, a **register scan**, followed by a **shift register scan** are performed. These two scans write various patterns into all registers and attempt to read them back. In this way, memory defects can be identified.

- Next, a DAC scan follows, where the various on-chip bias DACs are tested. These

voltage and current DACs, places in the periphery, steer the chip's in-pixel front-end

response. The DAC scan will verify that each DAC is working by sweeping through

all avaliable values. This scan is mainly done to verify the linear behaviour of the

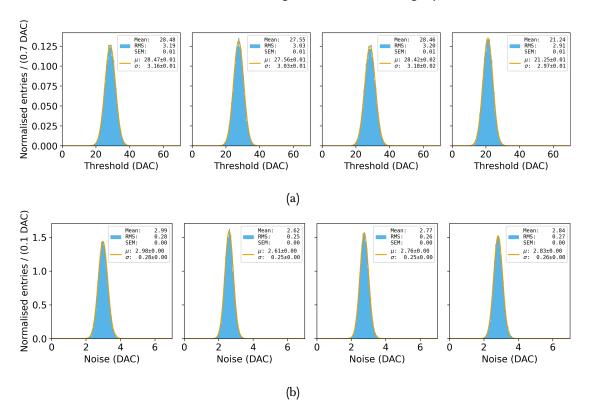

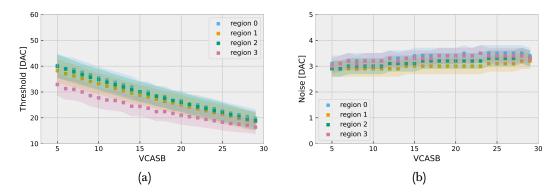

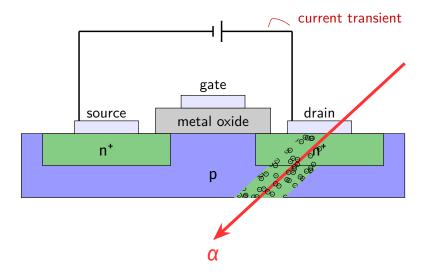

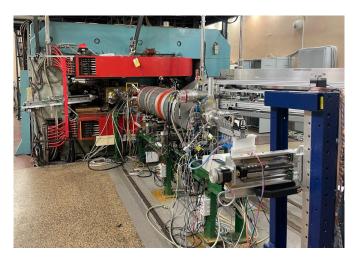

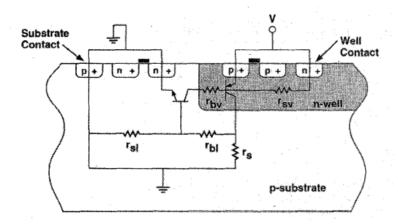

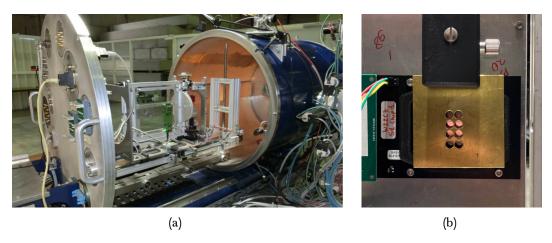

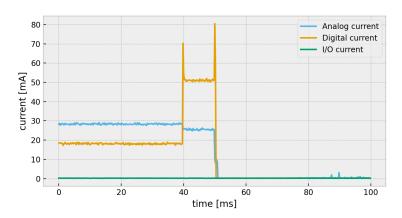

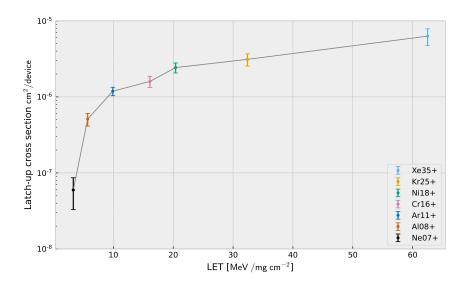

transistors, and check for any supply current anomalies.