# Department of Physics and Astronomy

University of Heidelberg

Master thesis

in Physics

submitted by

Benjamin Weinläder

born in Heidelberg

2020

# Development of a Monolithic Pixel Sensor with sub-nanosecond Time Resolution in BiCMOS

This Master thesis has been carried out by Benjamin Weinläder

at the

Physikalischen Institut Heidelberg

under the supervision of

Prof. André Schöning

#### Abstract:

In the field of particle physics, High Voltage Monolithic Active Pixel Sensors (HV-MAPS) are promising candidates to fulfil the high demands on spatial and time resolution of modern detectors. The Mu3e experiment with its development of the MuPix sensor has strongly driven this technology in recent years. As an example of the latest successes, the MuPix8 can be mentioned, which reached a time resolution of  $\sigma_t = 6.8 \, \text{ns}$ , using a 180 nm HV-CMOS technology.

The combination of HV-MAPS with a BiCMOS technology opens up further possibilities, especially for the improvement of time resolution, which was proven in the scope of the TT-PET project at the university of Geneva.

Based on this experience, this thesis aims to improve the time resolution of HV-MAPS to the sub-nanosecond regime, while maintaining a preferable small power consumption. Thereto, the advantages of the 130 nm BiCMOS process SG13S by IHP are utilised and studied.

Within the thesis, the pixel front end electronics, up to the digitisation of a hit signal is designed, with a special focus on the analogue sensor pixel and the charge sensitive amplifier. A characterisation of the pixel layout with Cadence® Virtuoso® resulted in a simulated ToA Jitter of  $\sigma_{ToA} = 86.12\,\mathrm{ps}$  for a signal, corresponding to a MIP. Further, a noise of  $ENC = 205\,\mathrm{e^-}$  was measured for the  $25\times25\,\mu\mathrm{m}^2$  large pixel. After the digitisation of the signal a ToA Jitter of  $\sigma_{ToA} = 435\,\mathrm{ps}$  is simulated for the whole pixel front end electronics.

#### Zusammenfassung:

Im Bereich der Teilchen Physik sind die Hochspannungsbetriebenen-Monolithischen Aktiven Pixel Sensoren (HV-MAPS) vielversprechende Kandidaten, die die hohen Anforderungen moderner Detektoren an die räumliche und zeitliche Auflösung erreichen können. In den letzten Jahren wurde diese Technologie vor allem durch das Mu3e Experiment und die zugehörige Entwicklung des MuPix-Sensors vorangetrieben. Nennenswert ist der letzte Erfolg, der MuPix8, mit dem eine Zeitauflösung von  $\sigma_t = 6.8\,\mathrm{ns}$  in einem 180 nm HV-CMOS Prozess erreicht wurde.

Eine Kombination von HV-MAPS mit einer BiCMOS Technologie bietet weitere Vorteile, vor allem kann die Zeitauflösung signifikant verbessert werden, wie im Rahmen des TT-PET Projekts an der Universität Genf gezeigt wurde.

Basierend auf dieser Erfahrung ist das Ziel dieser Arbeit, die Zeitauflösung von HV-MAPS in den Sub-Nanosekunden Bereich zu verbessern, während der Stromverbrauch möglichst klein gehalten wird. Es werden dazu die Vorzüge des 130 nm BiCMOS Prozesses SG13S von IHP genutzt und untersucht.

Die Pixel Frontend Elektronik bis zur Digitalisierung des Signals wird designt, dabei wird ein besonderes Augenmerk auf das analoge Sensorpixel und den Ladungsverstärker gelegt. Aus einer Charakterisierung mittels Cadence® Virtuoso® ergibt sich für das analoge Pixel ein simulierter Eingangszeit-Jitter von  $\sigma_{ToA}=86.12\,\mathrm{ps}$  für ein MIP-ähnliches Signal. Des weiteren wurde ein Rauschen von  $ENC=205\,\mathrm{e^-}$  für das  $25\times25\,\mu\mathrm{m}^2$  große Pixel gemessen. Nach der Digitalisierung des Signals wird ein simulierter ToA Jitter von  $\sigma_{ToA}=435\,\mathrm{ps}$  für die gesamte Pixel Frontend Elektronik gemessen.

# Contents

| 1 | Intr              | oduction                               | 9        |

|---|-------------------|----------------------------------------|----------|

|   | 1.1               | State of Research                      | 10       |

|   |                   | 1.1.1 The Mu3e Experiment              | 10       |

|   |                   |                                        | 12       |

|   |                   |                                        | 13       |

|   |                   | <i>V</i>                               |          |

| 2 |                   | <b>J</b>                               | .5       |

|   | 2.1               | Definition of Semiconductors           | 15       |

|   | 2.2               | 1 1                                    | 18       |

|   | 2.3               | Doped Semiconductors                   | 20       |

|   | 2.4               | pn-Junction                            | 20       |

|   |                   | 2.4.1 pn-Junction in Equilibrium       | 20       |

|   |                   | 2.4.2 pn-Junction with External Fields | 22       |

| 3 | Trai              | nsistor 2                              | 25       |

| • | 3.1               |                                        | 25       |

|   | 3.2               | - ·-                                   | -<br>28  |

|   | 0.2               |                                        | 31       |

|   | 3.3               | ¥                                      | 32       |

|   | 0.0               |                                        | 32       |

|   |                   |                                        | 34       |

| 4 | Eloc              | ctrical Devices and Circuits           | 35       |

| 4 | 4.1               |                                        | 35       |

|   | $\frac{4.1}{4.2}$ |                                        | งย<br>36 |

|   | 4.2               | 9                                      |          |

|   |                   | 0 0                                    | 37       |

|   | 4.9               | 1                                      | 39       |

|   | 4.3               |                                        | 10       |

|   | 4.4               |                                        | 11       |

|   | 4.5               | 1                                      | 11       |

|   | 4.6               | Pixel Front End Electronics            | 13       |

| 5 | Sim               | ulation tools 4                        | -5       |

|   | 5.1               | Cadence                                | 15       |

|   |                   | 5.1.1 Schematic Editor                 | 15       |

|   |                   | 5.1.2 Layout Suite                     | 15       |

|   |                   | 5.1.3 Analog Design Environment        | 16       |

|   | 5.2   | 0                                       | 17<br>17   |

|---|-------|-----------------------------------------|------------|

| _ | c:    |                                         |            |

| 6 | _     |                                         | 9          |

|   | 6.1   |                                         | 19         |

|   | 6.2   | 0                                       | 50         |

|   | 6.3   |                                         | 51         |

|   | 6.4   | Measured Quantities                     | 53         |

| 7 | Layo  | out 5                                   | 55         |

|   | 7.1   | Layout Requirements                     | 55         |

|   | 7.2   | Optimisation Process                    | 56         |

|   |       | 7.2.1 Workbench                         | 56         |

|   |       |                                         | 58         |

|   |       | <u> </u>                                | 58         |

|   |       | <del>-</del>                            | 31         |

|   |       |                                         | 32         |

|   |       |                                         | 33         |

|   | 7.3   | 1                                       | 35         |

|   | 1.0   | 0                                       | 35         |

|   |       |                                         | 36         |

|   |       | v                                       | 39<br>39   |

|   | 7.4   | · · ·                                   | 70         |

|   | 1.4   |                                         | 70         |

|   |       | G                                       | 70<br>71   |

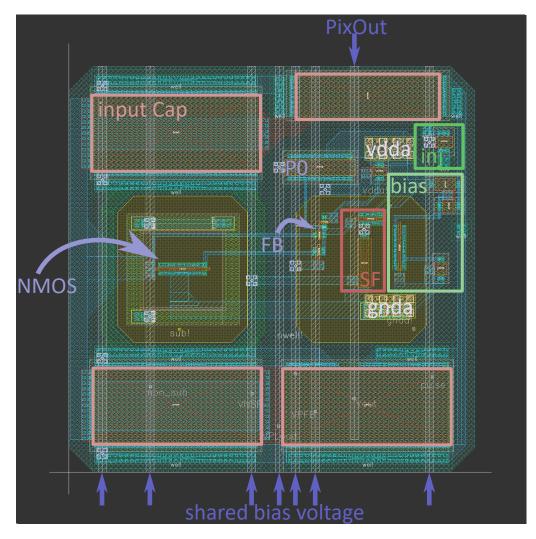

|   |       | 1.4.2 Layout Architecture               | 1 1        |

| 8 | Cha   | racterisation 7                         | <b>7</b> 3 |

|   | 8.1   | Characterisation of the Analogue Pixel  | 73         |

|   |       | 8.1.1 Transfer Function                 | 73         |

|   |       | 8.1.2 Transient Response                | 74         |

|   |       | 8.1.3 Noise Analysis                    | 76         |

|   |       |                                         | 79         |

|   |       | 8.1.5 The Detector Capacity             |            |

|   | 8.2   | Characterisation of the Pixel Front End |            |

|   | ·-    |                                         | 33         |

|   |       |                                         | 35         |

| 9 | Disc  | ussion and Summary                      | )1         |

| 9 | 9.1   | ·                                       | 93         |

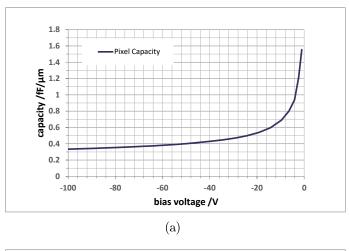

| Д | MııF  | Pix10 Pixel Capacity                    | 1          |

|   |       |                                         | , ,        |

| В |       |                                         | Ш          |

| C | Bibli | iography I                              | Ш          |

## 1 Introduction

In the modern physic, new phenomena are searched that can be described by theories well beyond established theories as the Standard Model (SM) of particle physics. Apart from the elaboration of these new theories, an essential part is to verify or falsify them in experiments, thus pushing the known boundaries further. In general, there are two approaches for modern high energy experiments: The first possibility, on the energy frontier, is to search for heavy resonances or new particles. In order to increase the probability to find such events in a moderate time scale, these experiments tend to increase the frequency at which is measured. This reflects in an increase of the luminosity of the associated particle collider. Collisions occur almost simultaneously, resulting in a signal pile-up. Here, a good example are the experiments located at the Large Hadron Collider (LHC) and in particular the planned upgrades. Another approach for high energy experiments are specialised precision experiments, which search for dedicated properties of particles or their rare decay channels. Deviations from the SM expectation can lead to new physics. The planned Mu3e experiment [1] with the search for the muon decay  $\mu^+ \to e^+e^-e^+$  can be mentioned as an example.

Regardless of the nature of the experiment, they set high demands on the spatial and time resolution. Either to achieve the necessary sensitivity or to distinguish single events, despite signal pile-up. Hence, the sensor technology, prevalently implemented as silicon tracking detectors, has to be adapted to the high requirements of new experiments.

A promising candidate is the implementation of High-Voltage Monolithic Active Pixel Sensors (HV-MAPS). Here, the Mu3e experiment with its development of the MuPix sensor has strongly driven this technology in recent years. The combination of HV-MAPS with the Bipolar Complementary Metal Oxide Semiconductor (BiC-MOS) technology adds additional advantages. This was proven at the university of Geneva, in the scope of the TT-PET project [2]. Due to the combination of the technologies a significant improvement of the time resolution was achieved.

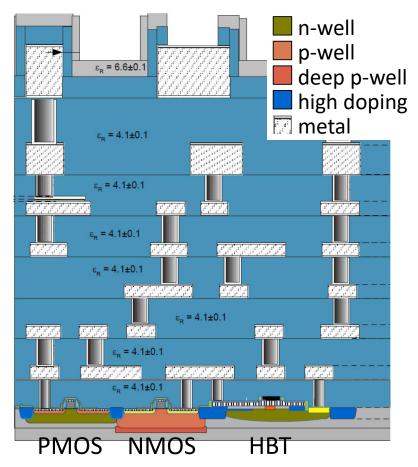

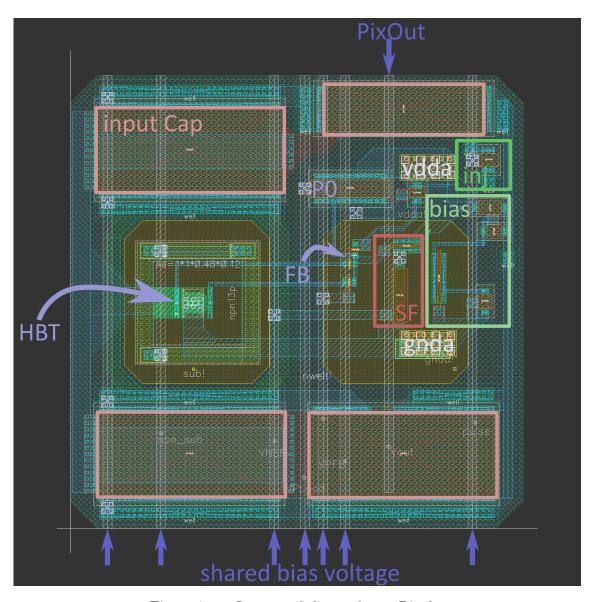

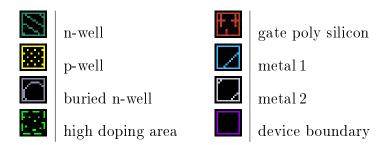

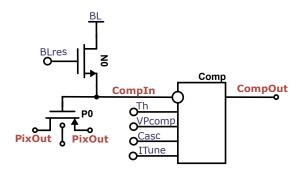

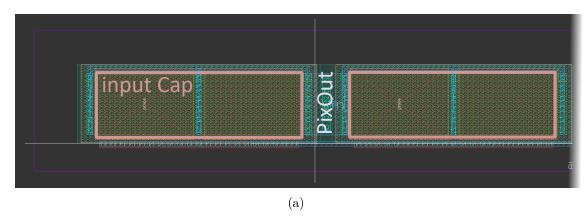

This thesis studies the improvements, which can be made by using the BiCMOS process SG13S [3] by IHP for the development of HV-MAPS. This process includes a heterojunction bipolar transistor (HBT) with a transient frequency of 240 GHz, besides 130 nm large standard Complementary Metal Oxide Semiconductor (CMOS) devises. The ambition is to design the analogue sensor pixel within the chip matrix and to optimise it for a time resolution in the sub-nanosecond regime. Based on the experience gained with the MuPix a starting point is chosen, e.g. for various circuitries and the power consumption. Therefore, several requirements are based on those of the Mu3e experiment. The performance of the optimised pixel and the

subsequent circuits up to the digitisation of the signal are studied. It is aimed to operate the resulting small pixel layout in a preferably large matrix with a low power consumption. The design process and the following characterisation is done with the software Cadence<sup>®</sup> Virtuoso<sup>®</sup>.

A possible fully functional sensor, including a time resolution of a couple tens of picoseconds and a large pixel matrix offers a huge potential for many experiments. Such sensor would approach the time performance of scintillators, while the pixel matrix would also collect spatial information. In that sense, it would meet with the requirements of the phase II of the Mu3e experiment, enabling a precise time measurement on the pixel detector, without the need of additional timing detectors.

#### 1.1 State of Research

A starting point for this study was chosen according to experience from the development of the MuPix sensor. In addition, the work of other research groups was also included, whereby the idea to implement HV-MAPS in a BiCMOS process has already been realised by the TT-PET project. Here, the current state of research will be presented.

## 1.1.1 The Mu3e Experiment

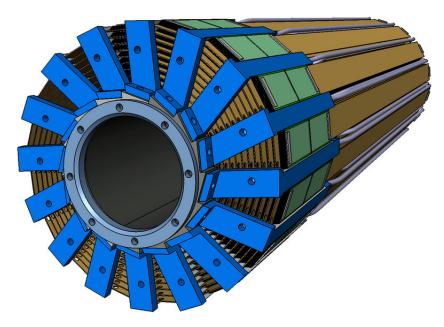

The Mu3e experiment [1, 4] at the Paul Scherrer Institut (PSI) is a precision experiment, which aims to search for the lepton flavour violating decay  $\mu^+ \to e^+e^-e^+$ . In two experimental phases, muons are stopped in a fixed target and their decay products are observed, with the detector presented in figure 1.1. In phase I a sensitivity of the branching ratio of  $2 \times 10^{-15}$  is targeted, which will be increased to  $10^{-16}$  in the second phase. Therefore, in phase II the muon decay rate is increased to approximately  $2 \times 10^9$ . Simultaneously, the detector will be adapted to the high muon intensity.

Figure 1.1: Schematic presentation of the Mu3e phase I detector, with an indicated decay  $\mu^+ \to e^+e^-e^+$ .

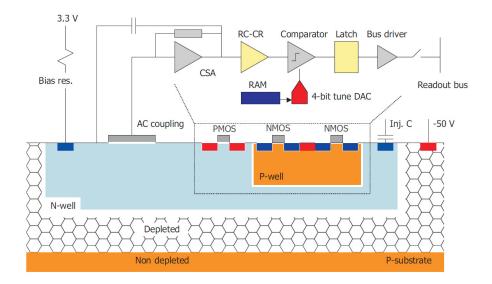

Figure 1.2: Conceptional illustration of an HV-MAPS.

In order to guarantee a successful measurement, several requirements are postulated for the detector system. This includes high constrains for the spatial and time resolution, as it is necessary to distinguish between several possible background signals and the searched decay. Moreover, the spatial resolution is limited by the multiple Coulomb scattering, due to the low energy of the decay particles. For this reason, it is essential to build the detector with a low material budget.

The MuPix sensor is being developed to meet these requirements. As an HV-MAPS it offers various advantages compared to hybrid pixel sensors, which are classically used for silicon pixel tracker. HV-MAPS combines the readout electronics and the sensor diode in a single die, reducing the used material. The electronics is implemented in a state of the art 180 nm high-voltage CMOS process, which is commercially available and thus reduces the cost of the sensor.

The particle detection of the chip is realised as a diode, embedded in the silicon p-typed substrate. As indicated in figure 1.2, the anode of the diode is implemented by a deep n-well, below the readout electronics of the pixel. A more detailed discussion of the detection process is given in section 4.1. As explained there, another feature of the HV-MAPS is the fast charge collection via drift, reinforced by the high voltage. Further, the high voltage increases the detection volume of the sensor diode, as it results in a large depletion zone.

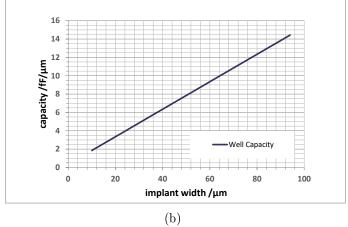

The MuPix sensor, specially developed for the Mu3e experiment, has gone through several iterations. The latest version, the MuPix10 is a fully integrated large prototype with a chip size of  $20.66 \times 23.18 \,\mathrm{mm^2}$ . Thereby, its active matrix contains  $256 \times 250 \,\mathrm{pixels}$ , each of a size of  $80 \times 80 \,\mu\mathrm{m^2}$ . This results in a pixel capacity of approximately 70 fF, calculated from TCAD simulations presented in figure A.1. Based on the geometry of the pixel, the sensor has a spatial resolution of approximately  $23 \,\mu\mathrm{m}$ , given by  $1/\sqrt{12}$  of the pixel size. For the time resolution a value

below 20 ns is targeted. In measurements with previous iterations like the MuPix8 this specification could be met, with a measured time resolution of 6.8 ns [5]. Further, due to the limited cooling power of the detector, the chip should not exceed a power consumption of  $350 \,\mathrm{mW/cm^2}$ . Depending on it settings, the MuPix8 sensor typically reaches a power consumption of  $250 \,\mathrm{mW/cm^2}$ . With regard to its geometry this translate in a power consumption per channel of approximately  $16 \,\mu\mathrm{W/ch}$  [6].

Additional to the MuPix sensor, it is foreseen to have a dedicated time measurement. This is realised by a layer of scintillating fibres [7] and tiles [8], as it can be seen in figure 1.1. These provide a time resolution below 500 ps and 100 ps respectively. If these timing requirements are fulfilled by an updated version of the MuPix, it would be possible to run phase II of the experiment only with pixel sensors.

## 1.1.2 The TT-PET Project

The aim of the Thin Time-of-flight Positron Emission Tomography (TT-PET) project [2] is to develop a PET scanner with an improved spatial resolution, based on the time-of-flight measurement. According to the basic principle of PET, the ring detector, shown in figure 1.3, measures two gamma rays travelling in opposite directions. The silicon sensor therefore measures the electron shower, emerging from the photons stopped in a lead layer. The additional information from the time difference of both signals, can be used to reconstruct their vertex. Therefore, the project requires a time resolution of 30 ps, which translates into a spatial resolution of approximately 1 mm. Due to a structure of several layers of sensors, the spatial resolution is conserved, even when the origin is not located in the detector centre.

Figure 1.3: CAD drawing of the TT-PET detector [9].

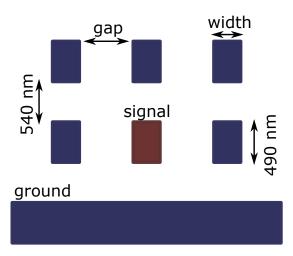

For this project an HV-MAPS is developed, with the idea to implement its front end electronics in a BiCMOS process. Due to the excellent timing and noise performance of the bipolar transistor, it is possible to achieve the required time resolution. Both, timing and noise behaviour of the transistor are explained in more detail later, e.g. in section 3.2.1 and 6.3 respectively. Based on this, a demonstrator chip [10] was produced, using the BiCMOS process SG13S by IHP. It was designed to test the main features of the final TT-PET chip. Thereto, it comprises an active matrix with  $10 \times 3$  pixels, each of a size of  $470 \times 470 \,\mu\text{m}^2$  and a spacing of  $30 \,\mu\text{m}$ . This results in a simulated pixel capacity of 750 fF. Signals are read out in a simple architecture, reducing the complexity of the readout logic.

For the demonstrator chip a time resolution of 110 ps was measured in a high-power mode with a power consumption of  $375 \,\mu\text{W/ch}$ . The front end noise of the sensor pixel was estimated to be  $350 \, \text{e}^-$ .

## 1.1.3 Hexagonal Prototype

Based on this excellent result from the TT-PET demonstrator chip, a prototype chip [11] is produced at the university of Geneva. It is a proof of concept with the intention to achieve a time resolution below 100 ps.

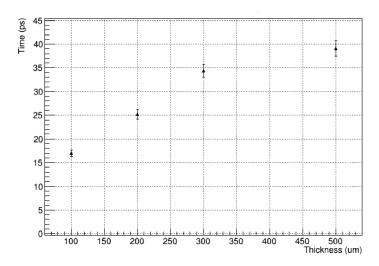

The HV-MAPS is produced in the SG13G2 [12] process by IHP and contains two matrices with hexagonal pixels, either with a side of  $130\,\mu\mathrm{m}$  or  $65\,\mu\mathrm{m}$ . Due to the smaller pixel size and the consequently lower detector capacity of  $220\,\mathrm{fF}$  or  $70\,\mathrm{fF}$ , it was possible to reduce the electric noise of the chip. This results in a measured time resolution of  $55\,\mathrm{ps}$  for the large pixels and  $46\,\mathrm{ps}$  for the small pixels. The estimated noise charge are  $160\,\mathrm{e^-}$  and  $90\,\mathrm{e^-}$  respectively.

## 2 Semiconductor Physics

The main scope of this thesis is to create and discuss circuits on chip-level. Therefore, it is essential to understand the basics of semiconductors physics, starting with the definition of a semiconductor and the behaviour of charge carriers inside the semiconductor.

#### 2.1 Definition of Semiconductors

The physics of condensed matter [13, 14, 15] distinguish between isolators, conductors and semiconductors. Naturally, the simplest definition of these three classes can be done via the conductivity. In this sense, the conductivity of a metal is infinite large, while it goes to zero for insulators. The conductivity of a semi conductor should be located somewhere in between, whereby the borders between the classes blur and are therefore not well defined.

A more elaborate way uses the electronic band structure of solid materials to define semiconductors and further describe their basic behaviour. In order to establish the electronic band model, it is necessary to make some assumptions: the lattice of the solid crystal is expressed by a periodic potential, whereby the positive atomic nuclei are taken into account as a small perturbation. Further, the One-Electron Approximation should be true, meaning there is no interaction between single electrons. It is therefore sufficient to solve the Schrödinger Equation

$$\mathcal{H}\Psi(\mathbf{r}) = \left[ -\frac{\hbar^2}{2m} \nabla^2 + V(\mathbf{r}) \right] \Psi(\mathbf{r}) = E\Psi(\mathbf{r})$$

(2.1)

once for a single electron. By summing up all N possible electronic states, considering the Pauli Principle, the solution for the entire solid follows.

Starting with the periodic potential  $V(\mathbf{r})$ : It fulfils the translation symmetry  $V(\mathbf{r}) = V(\mathbf{r} + \mathbf{R})$ , whereby  $\mathbf{R}$  is an arbitrary lattice vector between two nuclei. Calculations are done in the reciprocal space, hence the potential is expressed dependent on the reciprocal lattice vector  $\mathbf{G}$ , using the Fourier series.

$$V(\mathbf{r}) = \sum_{\mathbf{G}} V_{\mathbf{G}} e^{i\mathbf{G}\mathbf{r}} \tag{2.2}$$

For the electron, the general ansatz of a linear combination of plain waves is used. A more precise description of the electrons was done by Felix Bloch [16]. He found that the plain waves had to be modulated by a lattice periodic function, in order to move in the periodic crystal without scattering.

$$\Psi_{\mathbf{k}}(\mathbf{r}) = u_{\mathbf{k}}(\mathbf{r})e^{i\mathbf{k}\mathbf{r}}, \quad u_{\mathbf{k}}(\mathbf{r}) = u_{\mathbf{k}}(\mathbf{r} \pm \mathbf{R})$$

(2.3)

Only deviation of the perfect periodicity will lead to scattering.

Further, by explicitly solving the Schrödinger Equation 2.1 it can been shown that the momentum of the electron k is directly connected to k + G. Hence, the equation:

$$\Psi_{k+G} = \Psi_k \tag{2.4}$$

holds, meaning, the momentum is not unique but can differ by a reciprocal lattice vector G. It is therefore sufficient to indicate the solution for the first Brillouin zone to solve the whole system. This method is called reduction to the first Brillouin zone and it also applies to the eigenvalues.

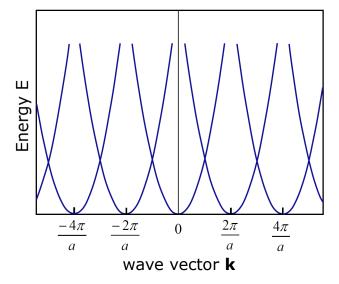

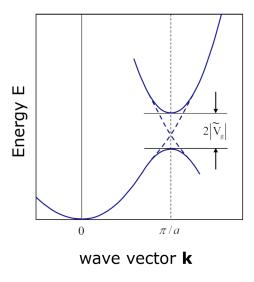

- (a) Representation of the energy eigenvalues according to equation 2.5.

- (b) The eigenvalues reduced to the first Brillouin zone.

Figure 2.1: Eigenvalues of a one-dimensional system in the empty lattice approximation (adapted from [13]).

A first simple solution for the eigenvalues can be found using the approach of the empty lattice approximation, whereby the potential  $V_{\mathbf{G}} \approx 0$  of the lattice is assumed to be small. However, the periodic nature of the lattice will remain. This leads to the following parabolic expression for the energy eigenvalues:

$$E_{\mathbf{k}} = \frac{\hbar^2 \mathbf{k}^2}{2m} = E_{\mathbf{k}+\mathbf{G}} = \frac{\hbar^2}{2m} |\mathbf{k} + \mathbf{G}|^2$$

(2.5)

In figure 2.1 these eigenvalues in a one-dimensional system are presented. Furthermore, the reduction to the first Brillouin zone 2.1(b) is shown, which in principle corresponds to folding back the eigenvalue function.

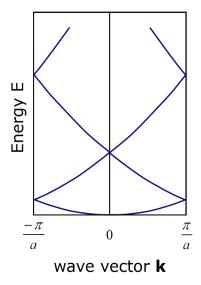

Introducing the potential  $V_G$  again as a small perturbation leads to the nearly free electron approximation. Due to the influence of the atomic nuclei, a splitting of

the eigenvalue function occurs at crossing points, which is indicated in figure 2.2(a). Thus, individual energy bands are formed, which are separated from each other by gaps  $E_g$ . Within these gaps no energy states are allowed, while there is a discreet function describing the bands. It should be noted that the bands are not a consequence of lattice periodicity, but of interactions between atoms.

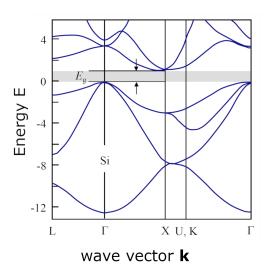

- (a) Influence on the eigenvalues of the potential  $V_G$  in the nearly free electron approximation. The dashed line indicates the solution for the emtpty lattice approach.

- (b) Band structur of a silicon crystal given in eV. Marked is the energy gap  $E_G$  of the indirect semiconductor.

Figure 2.2: Illustration of the band structur in a simplified theory and for silicon (adapted from [13]).

The energy eigenvalues in the system are occupied until all electrons are distributed, with the electrons satisfying the Fermi-Dirac statistic. Accordingly, a state can only be occupied by two electrons with different spin. The energy of the highest occupied state at  $T=0\,\mathrm{K}$  is given by the so-called Fermi energy:

$$E_F = \frac{\hbar^2}{2m} (3\pi^2 n)^{2/3} \tag{2.6}$$

whereby n is the density of electrons. The highest fully occupied band is called the valence band, the first band not occupied is the conduction band. In the following the upper edge of the valence band is referred to as  $E_V$  and the lower edge of the conduction band as  $E_C$ .

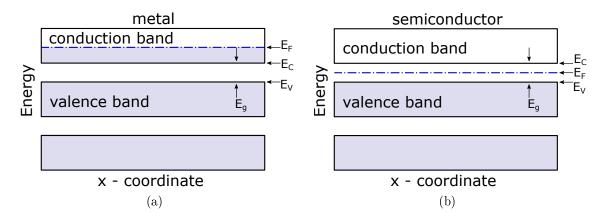

With this, a semiconductor can be defined as material, where the Fermi energy is located between the valence and the conduction band. In contrast, the Fermi energy of a metal, is located inside the conduction band. Since every state below the Fermi energy is occupied at  $T = 0 \,\mathrm{K}$  and there is a state for every momentum direction,

Figure 2.3: Representation of the valence- and conduction band for a metal-like material (a) and a semiconductor (b). Also indicated is the location of the Fermi energy  $E_F$  for both cases (adapted from [13]).

the full bands do not contribute to conduction effects. To be more precise, for every electron with a specific momentum and energy there is another electron within the same band, with the contrary momentum and the same energy. Thus, on average, no macroscopic current can flow. In order to obtain conduction, electrons need to be excited into higher states - the conduction band. For a metal-like material, electrons already occupy part of the conduction band. But since the conduction band is not fully filled in the case of metal, a current can flow at T=0. For a semiconductor, an energy equal the energy gap  $E_g$  is required to achieve conductivity. The energy gap of insulators is often that large, the required energy is similar to the energy to cause a phase transition of the material.

Semiconductors per se can be further classified into direct and indirect semi-conductors, whereby the difference here is given by the minimal band gap  $E_G = \min(E_C - E_V)$ . Figure 2.2(b), a realistic presentation of the band structure of silicon, is a good example for an indirect semiconductor. As indicated there, the minimal gap is between the valence band at the  $\Gamma$ - point and the X-point of the conduction band, whereby the points refer to different orientations in the reciprocal space. For the indirect transition at  $E_G$ , an additional momentum k is necessary. Contrary to this, for direct semiconductors a direct transmission is possible.

## 2.2 Transport Properties of Semiconductors

In order to understand the mechanism of conduction in a semiconductor, its transport properties should be discussed. Again the band structure plays an important role. As mentioned above, the Fermi energy is located between the valence and the conduction band. Therefore, the valence band is fully occupied at  $T=0\,\mathrm{K}$ , while the conduction band is empty. This means the semiconductor is an insulator in first place. However, if energy is added to the system, the Fermi function f(E,T), which

describes the occupation probability of the energy eigenstates, softens at the Fermi edge. In this case electrons are excited into the conduction band, where they can move freely and contribute to a current. The number of excited electrons can be described by the following equation:

$$n = \frac{1}{V} \int_{E_C}^{\infty} D_C(E) f(E, T) dE = 2 \left( \frac{m_e^* k_B T}{2\pi \hbar^2} \right)^{3/2} e^{-(E_C - E_F)/k_B T}$$

(2.7)

$$D_C = \frac{V}{2\pi^2} \left(\frac{2m_e^*}{\hbar^2}\right)^{3/2} \sqrt{E - E_C}$$

(2.8)

whereby  $D_C$  is the density of states of the electrons in the conduction band, assuming again the nearly free electron approximation with a parabolic eigenfunction. Further, the concept of the effective mass tensor

$$\left(\frac{1}{m_e^*}\right)_{ij} = \frac{1}{\hbar^2} \frac{\partial^2 E(\mathbf{k})}{\partial k_i \partial k_j} \tag{2.9}$$

is used, which is a mathematical way to introduce the dispersions relation or rather the interaction between the electrons and the atomic nuclei into the equation.

Due to the transition of electrons into the conduction band, empty states are left in the valence band. These empty states are called holes and act similar to the excited electrons, meaning they can move in the k- space like a free electron by giving nearby electrons the possibility to change their state. The most important properties are  $\mathbf{k}_p = -\mathbf{k}_n$ ,  $E_p(\mathbf{k}) = -E_n(\mathbf{k})$  and  $m_p^* = -m_n^*$ . Externally, the holes appear like positively charged particles, and accordingly they tend to move towards the upper edge of the valence band and also contribute to the charge transportation. In the following holes will be referred to with the index p, while electron depending values are referred to with n.

Hence, the conductivity of the semiconductor

$$\sigma = e(n\mu_n + p\mu_p) \tag{2.10}$$

is given by the density of free electrons n and holes p multiplied by there mobility  $\mu_i$  with i=n,p. For the latter applies  $\mu_i=e\tau_i/m_i^*$ , which is referable to the classic model of Drude [17]. The mobility of both, electrons and holes is defined by the relaxation time  $\tau_i$  characterising the friction or in other words the mean scattering time. Typically, electrons scatter at defects or vacancies in the lattice and at phonons. Since holes are free electronic states, so their motion is in fact due to electron motion, their scattering rates are of the same order of magnitude.

In silicon the mobilities at room temperature are  $\mu_n(Si) = 1900 \,\mathrm{cm^2/Vs}$  and  $\mu_p(Si) = 480 \,\mathrm{cm^2/Vs}$ . Other semiconductors, such as germanium, have significantly higher mobilities  $\mu_n(Ge) = 3800 \,\mathrm{cm^2/Vs}$  and  $\mu_p(Ge) = 1800 \,\mathrm{cm^2/Vs}$ .

When the semiconductor is brought into an external electric field, the free electrons drift along the field lines. Thereby, the drift velocity  $v_D = \mu \mathcal{E}$  is defined by

the mobility of the semiconductor and the external field  $\mathcal{E}$ . For very large electric fields the model of Drude no longer holds and the mobility becomes dependent on the electric field. The drift velocity saturates at  $v_D = \mathcal{O}(10^5)\,\mathrm{m/s}$  in the case of silicon.

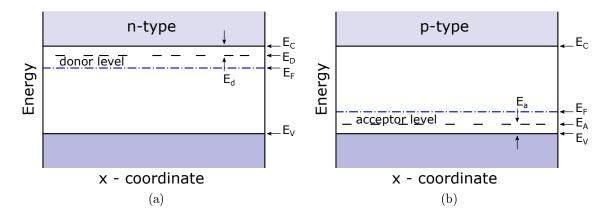

## 2.3 Doped Semiconductors

In the previous description, only intrinsic semiconductors were considered. Their conductivity is usually too low for useful electrical applications. Thus, in the following a process is described, by which the conductivity of semiconductors can be further modified, the so-called doping. During doping, dopant atoms are introduced into the lattice of the semiconductor, providing additional energy levels between valence and conduction band. These dopant atoms are typically atoms containing one electron more (donors) or one electron less (acceptors) in the outer electron shell. If, for example, a donor is introduced into the semiconductor, it has an additional electron which is not needed for covalent bonding to the neighbouring atoms. In order to release this electron from the donor and lift it as a free electron into the conduction band, a comparably small amount of energy is sufficient. As indicated in figure 2.4(a), the energy level of the donor is located closely to the edge of the conducting band. This type of doping is hereinafter referred to as n-type. Accordingly, in a p-type semiconductor, the acceptor offers a free state that can be occupied very easily by an electron, creating a hole in the valence band. In this sense, doping can be used to modify the number of free electrons or holes in the semiconductor, hence modifying its conductivity. The actual number of charge carriers is highly dependent on the temperature. At  $T = 0 \,\mathrm{K}$  the doping impurities have no influence, whereas this influence becomes significant when the thermal energy reaches up to  $E_d$ . Additionally, the added n- or p-typed charge carriers effect the position of the Fermi energy and shift it in the direction of the donor or respectively acceptor energy.

## 2.4 pn-Junction

When differently doped semiconductors are combined, a pn-junction [13, 15] is created, which will be discussed in the following. To simplify the system an abrupt transition from p- to n-type semiconductor is assumed. Despite this simplification, the upcoming chapters will show that the description of the junction is helpful to characterize different electrical components.

## 2.4.1 pn-Junction in Equilibrium

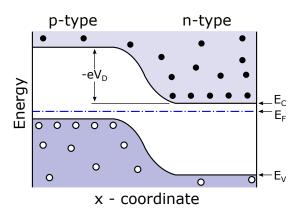

As mentioned above and indicated in figure 2.4, the Fermi Energy is effected by doping. Further, it should be noted that in a single system only a unified Fermi level  $E_F$  can exist.

Figure 2.4: Energy levels for an n-type (a) and p-type (b) semiconductor. The Fermi Energy  $E_F$  is also represented. Here room temperature was assumed, since  $E_F$  varies with additional charge carriers and respectively the temperature (adapted from [13]).

If differently doped semiconductors are brought together, a common Fermi level must be formed. To achieve an equalization of the different Fermi energies, charge carriers diffuse from one side of the semiconductor to the other. Electrons diffuse from the n-type side, while the additional holes migrate from the p-type side. A diffusion voltage  $V_D$  is created by the dopant ions left behind, which causes the bands to bend. At the same time, the voltage results in a drift of charge carriers in the opposite direction. Both currents, diffusion- and drift current, cancel each other, forming the new equilibrium state.

The diffusion voltage can be calculated, using the concentration of donor  $n_D$  and acceptor  $n_A$  atoms:

$$eV_D = k_B T \ln\left(\frac{n_D n_A}{n_i^2}\right) \tag{2.11}$$

Here, the law of mass action  $n_i^2 = n \cdot p$  applies for the density of charge carriers n and p.

In the junction area, the so-called depletion zone is formed, in which the number of free charge carriers is reduced significantly. The reason is that charges which have diffused into the differently doped side recombine with the dopant atoms. Most of the other charge carriers are expelled by the prevailing electrical fields. The depth of the depletion zone in the n-type side is given by following equation:

$$d_n = \sqrt{\frac{2\epsilon_r \epsilon_0 V_D}{e} \frac{n_A/n_D}{n_A + n_D}} \tag{2.12}$$

The depth on the p-side can be derived by interchanging the concentrations of doping atoms accordingly.

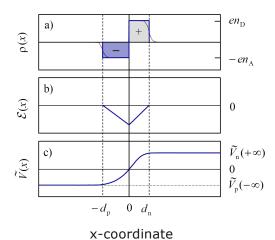

- (a) Schematic picture of the band structure of a pn-junction in equilibrium (adapted from [13]).

- (b) Representation of the space charge  $\rho(x)$  and the resulting electrical field  $\mathcal{E}(x)$  and potential  $\tilde{V}(x)$ . Further, the depth of the depletion zone  $d_{n/p}$  is indicated [13].

Figure 2.5: Pictures illustrating the principle of a pn-junction in equilibrium.

Since in this area no free carriers exist, the whole charge is dominated by the dopant atoms. The depletion zone is charged negatively in the p-doped side and positively in the n-doped side. As indicated in Figure 2.5(b) a box function is assumed. This space charge results in an electrical field  $\mathcal{E}(x)$  and again in the bend potential curve  $\tilde{V}(x)$ , obeying the Poisson equations.

## 2.4.2 pn-Junction with External Fields

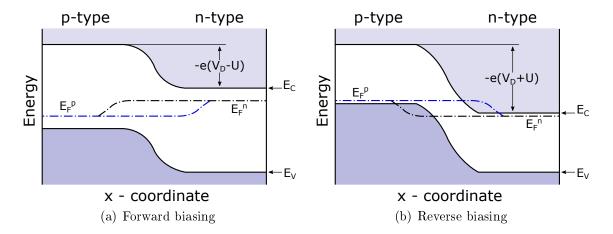

By applying an external voltage to the pn-junction, the state of equilibrium is disturbed, which results in new effects. Thereby, a distinction is made between the forward and the reversed bias mode.

In the forward biasing case a positive potential is connected to the p-type semi-conductor. As shown in figure 2.6(a) the potential energy of the electrons on the p-side is reduced by U. Thereby, the potential step is reduced. This disturbs the equilibrium and the two currents that flow in the pn-junction no longer cancel each other out. Simultaneously, it is no longer possible to form a unified Fermi level due to the different charges in the space-charge zones. The same applies in the case of an applied reverse bias voltage (figure 2.6(b)), with the exception of an increase of the potential step.

The two types of currents within the junction are influenced by the change in band structure. As already mentioned, they are out of balance due to the bias voltage. The reason is that the diffusion current is highly dependent on the height of the

Figure 2.6: Band structure of a pn-Junction with an external voltage U (adapted from [13]).

barrier, which is reduced by  $V_D - U$ :

$$j_{diff}(U) \sim e^{-e(V_D - U)/k_b T} \sim j_{diff}(0) e^{eU/k_B T}$$

(2.13)

whereas the drift current is independent:

$$j_{drift}(U) \approx j_{drift}(0) = j_{diff}(0) \tag{2.14}$$

These equations apply likewise to electrons and holes. Hence, the total current is given by the following equation:

$$j(U) = (j^n + j^p)_{diff}(U) - (j^n + j^p)_{drift}(U) = j_0 \left(e^{eU/k_B T} - 1\right)$$

(2.15)

which shows the highly non-linear characteristic of a biased diode.

Furthermore, the influence of the bias voltage on the depletion zone should be discussed, whereby  $U < V_D$  applies in the following. In equation 2.12 the potential  $V_D$  must be exchanged by  $V_D - U$ , in order to take the change of the potential step into account. Thus the equation changes as follows:

$$d_n(U) = d_n(0)\sqrt{1 - \frac{U}{V_D}}, \quad d_p(U) = d_p(0)\sqrt{1 - \frac{U}{V_D}}$$

(2.16)

Meaning, the depletion zone increases in the reversed biased mode with increasing voltage U.

Since in the pn-junction charge is separated by the depletion zone it can also be seen as a capacitor. Its capacity therefore has to change with the depth of the depletion zone and is dependant on the impurity density  $n_D$ .

$$C = \frac{\mathrm{d}Q}{\mathrm{d}U} = e n_D A \left( \frac{\mathrm{d}}{\mathrm{d}U} d_n(U) \right) = \frac{A}{2} \sqrt{\frac{n_A n_D}{n_A + n_D} \frac{2e \epsilon_r \epsilon_0}{(V_D - U)}}$$

(2.17)

Here A describes the cross section area of the pn-junction.

## 3 Transistor

The most important technical application for semiconductors are transistors, which are essential for modern electronics. In principle, transistors can be used to control and amplify currents or voltages. In its simplest application it acts as a switch. Among others it can be distinguished between two main types of transistors, described in the following chapters.

## 3.1 MOSFET

First, the metal-oxide-semiconductor field-effect transistor (MOSFET) [13, 18] will be discussed, of which the structure is slightly more complicated, but the MOSFET is much more common nowadays. The MOSFET has three main terminals and one additional terminal, with the latter one connects the bulk and is often shared between many transistors. The transistor is controlled by the main terminals, which are the gate, source and drain pin. A voltage applied to the gate controls the resistance between drain and source, and thus the current  $I_{DS}$  flowing between them. Thereby, a special feature is that the gate connection is insulated by an oxide layer, so in an ideal picture no current can flow into the gate. Meaning, the current is truly controlled by an electric field, which leads to its name.

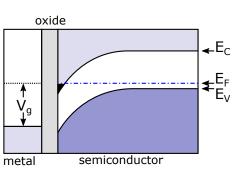

In order to understand the functionality of the MOSFET, a stack of semiconductor, oxide and metal (see figure 3.1(a)) can be discussed, which represents the behaviour at the gate. By applying a positive potential  $V_g$  on the gate, holes from the p-typed semiconductor are repelled and the concentration of free holes is reduced. Similar to the pn-junction, the immobile dopant atoms create a space-charge zone at the boundary surface. Then, as a result, the bands are bend. With the edge of the conduction band approaching the Fermi level, the number of free electrons increase significantly. A conductive area is created, which is isolated from the rest of the semiconductor by the depletion zone. Since electrons are the main type of charge carriers here, this area is called inversion layer. For high voltages  $V_g$  the edge of the conduction band is below the Fermi energy, hence the conducting channel has metallic properties.

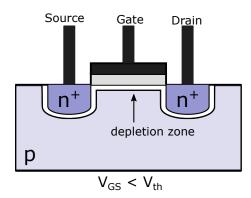

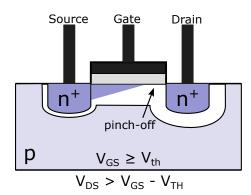

A more realistic layer structure of a MOSFET is presented in figure 3.1(b) to 3.1(d), whereby the voltage  $V_{GS}$  and  $V_{DS}$  are increased respectively. Furthermore, the pictures represent different modes, starting with the sub-threshold mode in figure 3.1(b). As the name indicates, the gate-source voltage  $V_{GS}$  is below the threshold voltage  $V_{th}$  in this mode.  $V_{th}$  marks the point, where the channel starts to form. Without the inversion layer the conductivity between drain and source pin is low

(a) Representation of the influence of a gate voltage on the semiconductor band structure. The boundary layer of metal, oxide and semiconductor is shown, with an external potential  $V_g$  applied to the metal side (adapted from [13]).

(b) Schematic layer structure of an n-type MOSFET in sub-threshold mode. For simplification source and bulk share the same potential (adapted from [19]).

(c) MOSFET in linear mode, with the n-channel displayed (adapted from [19]).

(d) MOSFET in the saturation mode after pinch-off (adapted from [19]).

Figure 3.1: Illustrations describing the functionality of the MOSFET and its different operating modes.

and only thermal excitation can cause a small current  $I_D$  [20]:

$$I_D = I_0 e^{\frac{q(V_{GS} - V_{th})}{nk_B T}} \left( 1 - e^{-\frac{qV_{DS}}{k_B T}} \right), \quad I_0 \sim \frac{W}{L}$$

(3.1)

here n is the slope factor and is given by  $n = 1 + C_{dep}/C_{Ox}$ , with the capacity of the depletion zone and the oxide respectively. The parameter W and L describe the width and the length of the transistor gate. Using equation 3.1 another important parameter can be derived:

$$g_m = \frac{\partial I_D}{\partial V_q} \tag{3.2}$$

The transconductance  $g_m$  is defined as an inverse resistivity and is often used to describe the current gain of a MOS-transistor.

Increasing the gate-source voltage above the threshold voltage, the MOSFET enters the linear mode, as long  $V_{DS} < V_{GS} - V_{th}$  holds. The transistor acts as a voltage controlled resistor in this region, resulting in a linear dependency between  $I_D$  and  $V_{GS}$ :

$$I_D = \mu_n C_{Ox} \frac{W}{L} \left( (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right)$$

(3.3)

With  $\mu_n$  being the mobility of electrons.

The last mode, the saturation mode, is reached when  $V_{DS} > V_{GS} - V_{th}$  applies, which implies an increase in voltage  $V_{DS}$ . Thereby, the voltage between gate and substrate is decreased in the vicinity of the drain connection, to the extent that the threshold voltage is undercut and accordingly the inversion layer is removed. This effect is called pinch-off and is visible in figure 3.1(d). Due to the pinch-off the current cannot rise further. Ideally the current should be independent from  $V_{DS}$ , however, with short transistors the channel lengths modulation becomes effective. With increasing  $V_{DS}$  the point of the pinch-off is shifted to the source, reducing the effective length of the channel. Thus, the resistance of the channel drops and the current can increase. Thereby, the area between the remaining channel and the drain is depleted. Meaning there are no free charge carriers available, but the large electric fields enable a drift of electrons. The channel length modulation is considered in the equation by  $\lambda$ :

$$I_D = \frac{\mu_n C_{Ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^2 (1 + \lambda V_{DS})$$

(3.4)

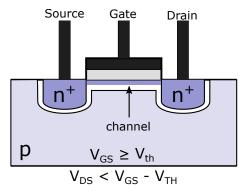

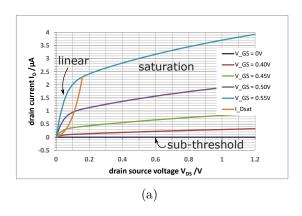

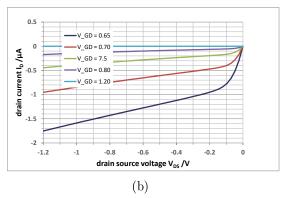

The total current characteristic, including all modes, is represented in figure 3.2(a) Up to this point, a p-typed substrate was assumed, resulting in an enriched electron conducting channel. These type of transistor is called n-type metal-oxide-semiconductor (NMOS). Accordingly there is also a p-type metal-oxide-semiconductor (PMOS), which conducts holes in the channel. In order to obtain a PMOS, the structure from figure 3.1(b) needs to be inverted, meaning the strong doped  $n^+$  regions

Figure 3.2: Current characteristic of an NMOS (a) and PMOS (b) transistor with indicated operation modes. Both transistors have a size of  $L=130\,\mathrm{nm}$  and  $W=150\,\mathrm{nm}$ .

must be  $p^+$  and the p-type substrate must be n-typed. Besides, the functionality remains the same as with NMOS, only the changed sign of the charge carriers must be taken into account. The current characteristic of the PMOS is shown in figure 3.2(b).

The combination of both types of MOSFET, p- and n-channel device, is called Complementary Metal Oxide Semiconductor (CMOS) topology. In the digital technology, both transistor form an input gate. Depending on a high or low voltage input either one of the transistors is turned of, due to the complementary behaviour of the transistor types. This results in the great advantage of CMOS logic that a current can only flow, while the state is switched. Hence, the power consumption is reduced significantly.

## 3.2 Bipolar Junction Transistor

A second type of transistor, which will be discussed in the following, is the bipolar junction transistor (BJT) [13, 15, 20]. In principle the bipolar transistor is a combination of two back-to-back pn-junction. Accordingly, there are pnp- and npn-transistors, while in the following the npn-typed bipolar transistor is discussed. Certainly, all results and properties also hold for the pnp-transistor, if the change of main charge carriers is taken into account.

The BJT has three terminals, namely the collector, emitter and base. But in contrast to the MOSFET, the bipolar transistor uses a control current applied to the base to regulate a current between collector and emitter. Another difference to the MOSFET is that here both types of charge carriers contribute to the current transport. Nevertheless, in the npn-BJT electrons are the predominant charge carriers.

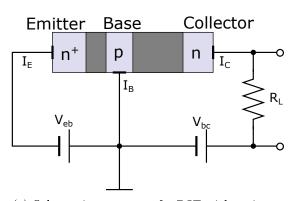

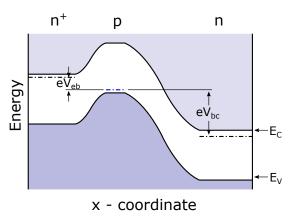

The bipolar transistor works as follows: The np-junction from emitter to the base is biased by  $V_{be}$  in forward direction, as it is indicated in figure 3.3(a). Thus,

- (a) Schematic structure of a BJT with an interconnection plan. Indicated is also the depletion zones between the different semiconductor areas (adapted from [15]).

- (b) Band structure of the BJT with connected bias voltage  $V_{eb}$  and  $V_{bc}$  (adapted from [15]).

Figure 3.3: Illustrations, which describe the function principle of the BJT.

electrons can move from the emitter into the base. The emitter is  $n^+$  doped to further increase the number of free electrons. Electrons, which reached the area of the base can recombine with the large number of holes located in the p-doped domain. To operate the transistor efficiently, it is therefore necessary to keep the width of the base as small as possible, at least in the order of the recombination length. The adjacent pn-junction, base to collector, is reverse biased by the  $V_{bc}$  voltage. If electrons that diffuse in the base region randomly enter the extended depletion zone of this junction, they are drawn off towards the collector by the strong electric fields. This behaviour can be traced back easily with the help of Figure 3.3(b). Furthermore, the figure illustrates that the resulting current does not significantly depend on the voltage  $V_{bc}$ . In contrast, the voltage  $V_{eb}$  has a direct influence on the number of electrons present and thus on the current.

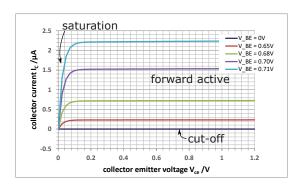

For the BJT again different operation modi can be distinguished: Starting with the cut-off region, which is reached when for the potentials at the terminals  $V_b < V_e$  and  $V_b < V_c$  holds. In an ideal picture, in this region no current  $I_C$  should flow, since both junctions are reverse biased. In contrast, equation 2.15 indicates that a junction with reverse bias still transmits a latching current  $I \sim -j_0$ . Nevertheless, for most applications the current  $I_C$  is negligibly small in this working mode.

In the case of  $V_e < V_b < V_c$ , the forward active mode is reached. This mode was used to explain the function principle of the BJT above. Here, the collector current can be approximated by the characteristic linear current amplification  $I_C = \beta I_B$ . Additionally,  $I_E \approx I_C$  can be assumed in good approximation. In order to be able to compare the bipolar transistor to the MOSFET, it is helpful to define its transconductance  $g_m$ .

$$g_m = \frac{\partial I_C}{\partial V_{be}} \tag{3.5}$$

Figure 3.4: Current characteristic of a bipolar transistor with indicated operation modes.

In the saturation mode, with  $V_b > V_e$  and  $V_b > V_c$ , both junctions are active. The region of the base is saturated with more electrons than needed for the current transmission. Thus, the current  $I_C$  becomes independent of  $I_B$ .

The total current curve, for all operation points (shown in figure 3.4), is described by the Ebers-Moll equation[21]:

$$I_E = I_S \left[ \left( e^{\frac{eV_{be}}{k_B T}} - e^{\frac{eV_{bc}}{k_B T}} \right) + \frac{1}{\beta} \left( e^{\frac{eV_{be}}{k_B T}} - 1 \right) \right]$$

(3.6)

whereby  $I_S$  describes the saturated latch current.

A similar effect as the channel length modulation of the MOSFET also occurs in the BJT. The change in voltage  $V_{bc}$  between base and collector, leads to a change in the size of the depletion zone between the two regions. Hence, the width of the base is reduce with increasing  $V_{bc}$ . As mentioned above, the width of the base has a significant influence on recombination of electrons and also on the current. This effect is called Early effect [22] and can be described in the forward active region by the following approximation:

$$I_C = I_S e^{\frac{eV_{be}}{k_B T}} \left( 1 + \frac{V_{ce}}{V_{Earlu}} \right) \tag{3.7}$$

Here, the Early voltage  $V_{Early}$  is a transistor dependent factor, describing the linear dependency on  $V_{CE}$ .

The advantages of the BJT are the high current gain  $\beta$  and corresponding transconductance  $g_m$ , as well as their typically high cut-off frequency. The cut-off frequency is defined as the frequency, where the gain of the transistor is reduced by 3 dB. Hence, with these attributes a BJT is suitable for high frequency applications. Regardless, the development of the CMOS technology is more advanced, leading to high density circuits with less power consumption. For analogue circuits many applications combine bipolar transistors with the CMOS topology. Such technologies are called Bipolar CMOS (BiCMOS), with the goal to benefit from advantages of both types of transistors [23].

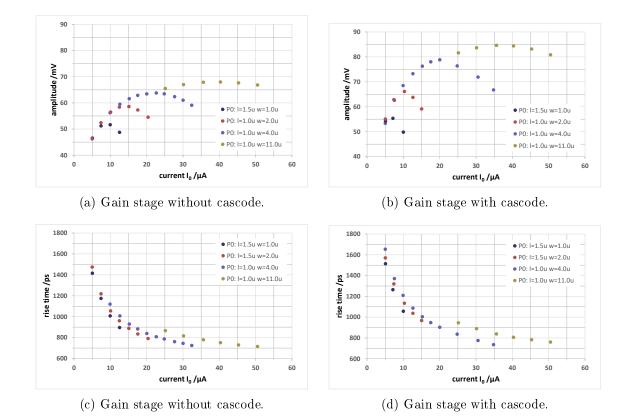

## 3.2.1 Heterojunction Bipolar Transistor

The heterojunction bipolar transistor (HBT) [24, 25] is a special design of a BJT that is intended to further increase the performance of the transistor. It uses the properties of heterostructures, which are layers of different semiconductors, to improve current amplification and transit time. When different semiconductors are brought together, their band structure is deformed, due to the varying energy gap of the single semiconductors. Thereby, its electrical properties and behaviour are changed.

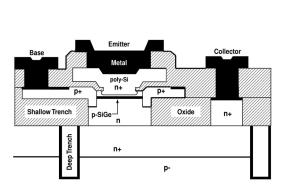

- (a) Schematic structure of a SiGe HBT [26].

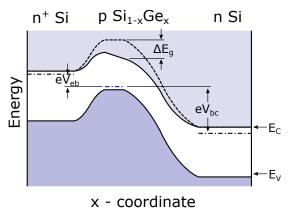

- (b) Band structure of an HBT. For comparison, the band structure of the BJT is indicated by a dashed line (adapted from [25]).

Figure 3.5: Illustrations describing the HBT and its features.

In the following, the special case of a silicon-germanium HBT will be picked out, although other semiconductor combinations are also possible. A typical structure of a SiGe HBT is shown in figure 3.5(a). As shown there, the base region consists of an alloy of p-doped  $Si_{1-x}Ge_x$ , while emitter and collector are still pure  $n^+$ - and n-typed silicon, respectively. It is particularly important for the base region that the germanium content increases towards the collector. Since the band gap of germanium is smaller than that of silicon, this gradient in concentration causes a reduction of the band gap along the base. This gradient is indicated in figure 3.5(b). It acts like a build in electrical field, changing the transport properties of the electrons in this region. In a normal BJT the electrons diffuse in the base region and enter the depletion zone between base and collector randomly. Due to the curvature of the band structure in HBT, a drift current is introduced into the base, which drives the electrons into the depletion zone. Meaning, the transit time  $\tau_B$  of the electrons in the base is reduced significantly.

If again the current amplification  $\beta = I_C/I_B$  is considered, it can be shown that this is proportional to  $\tau_{Bp}/\tau_t$ .  $\tau_{Bp}$  defines the part of the base current which results from the recombination of holes in the base. The total transit time of the electrons is described by  $\tau_t$  which decreases respectively with  $\tau_B$ . Consequently, higher current

gains can be achieved in the HBT, as well as a higher transit frequency  $f_t = 1/\tau_t$ . According to its definition the transit frequency indicates the maximum switching speed of the transistor. Besides, it marks the frequency, where the current gain becomes unity.

In addition, germanium has a higher mobility, thus reducing the base resistance. This allows for a much higher oscillation frequency  $f_{max}$ , because it is bound to the RC-element of base resistance  $R_B$  and base-collector capacity  $C_{BC}$  as follows [24]:

$$f_{max} \approx \sqrt{\frac{f_t}{8\pi R_B C_{BC}}} \tag{3.8}$$

The maximum oscillation frequency is further defined by the power gain, which is unity at the point of  $f_{max}$ .

#### 3.3 Noise Sources in a Transistor

To operate a transistor efficiently in a circuit, it is necessary to understand its noise behaviour [23, 18, 27].

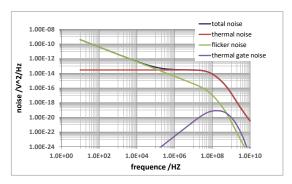

(a) NMOS with minimum length  $l=130\,\mathrm{nm}$  and width  $w=150\,\mathrm{nm}$ .

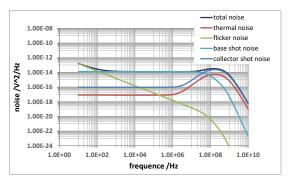

(b) Bipolar transistor.

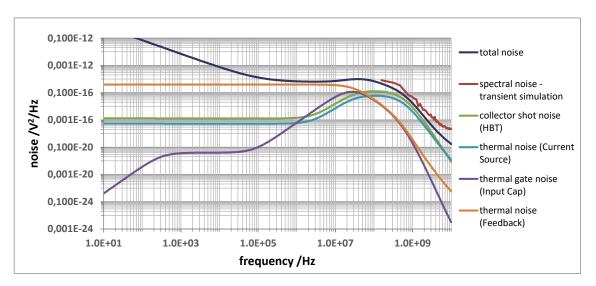

Figure 3.6: Simulated Noise of an NMOS (a) and bipolar transistor (b). Shown are the total noise as well as different components in a range from 10 Hz to 10 GHz.

#### 3.3.1 Noise of a MOSFET

For the MOSFET, there are mainly two types of noise, whereby thermal noise will be discussed first.

The reason for thermal noise are thermal fluctuations in the velocity distribution of the charge carriers. Since, in a simple picture, the channel of a MOS-transistor is an adjustable resistor, thermal voltage noise is a significant factor. A characteristic of thermal noise is its independence of frequency, which is the reason why it is also

called white noise. Its noise frequency spectrum can be expressed by the following equation:

$$\frac{\mathrm{d}\langle v_{therm}^2 \rangle}{\mathrm{d}f} = 4k_B T \gamma \frac{1}{g_m} \tag{3.9}$$

It should be noted, this equals the typical thermal noise of a resistor with the resistance  $\gamma/g_m$ . The additional coefficient  $\gamma$  takes into account that the channel thickness decreases towards the drain pin depending on  $V_{DS}$ . This indicates a change in the factor depending on the operation mode and thus channel structure. In the saturation mode typically  $\gamma = 2/3$  is used.

As shown in the simulation in figure 3.6(a), the characteristic of frequency independence applies over a wide frequency range. Only the natural bandwidth of the MOSFET influences the thermal noise at  $f > f_c$ , where  $f_c$  is the cut-off frequency of the transistor, given by the limited transition time of the charge carriers in the channel.

The thermal fluctuation of the charge carriers in the channel also result in a noise at the gate terminal. Due to the capacitive coupling via the oxide capacitance  $C_{Ox}$ , it shows a  $f^2$  dependency and is induced as a gate current. In the following this type of noise will be referred to as gate induced thermal noise [28].

$$\frac{\mathrm{d}\langle i_{gate}^2 \rangle}{\mathrm{d}f} \approx 4k_B T \, \gamma g_m \left(\frac{f}{f_t}\right)^2 \tag{3.10}$$

Here, the transit frequency of the MOSFET can be approximated by  $f_t \approx g_m/(2\pi C_{GS})$  and furthermore the fraction  $(f/f_t)^2$  indicates that this type of noise is only relevant for very high frequencies. The gate induced thermal noise is also presented in figure 3.6(a). However, it only makes a negligible contribution to the overall noise, since a MOS transistor is simulated with minimal size and therefore the capacitive coupling is negligible. Yet the  $f^2$  dependency is clearly visible.

The second main type of noise in a MOSFET is the so called flicker or 1/f noise. It is often described by the following model: Moving charge carriers in the semiconductor can be trapped by impurities and defects in the atomic lattice. While bound, the shortly fixed charge influences the potential and thereby the behaviour of the transistor. Typically, according to a characteristic time constant  $\tau$ , the charge is released again. The release time strongly depends on the energy of the binding state. This noise source is particularly prominent in MOSFETs because the conducting channel is located directly at the boundary between semiconductor and oxide. Accordingly, electrons are trapped in the defects that are often present there, since in general lattices at interfaces are less impeccable. The superposition of a large number of traps with different  $\tau$  causes the 1/f noise, whose spectral noise distribution, described as gate noise voltage, is given by:

$$\frac{\mathrm{d}\langle v_{1/f}^2 \rangle}{\mathrm{d}f} = \frac{K_f}{C_{Ox}WL} \frac{1}{f} \tag{3.11}$$

Whereby the parameter  $K_f$  is a production process related constant.

#### 3.3.2 Noise of a BJT

The noise sources in a BJT differ from those in a MOSFET. Although both flicker and thermal noise occur in almost every component, they play a minor role in bipolar transistors, as it is indicated in figure 3.6(b). Thermal noise is always associated with a resistivity, which in the case of the BJT would be the resistance of the base. This resistance is typically very low and even lower in HBTs. As described in the previous section, flicker noise is pronounced in the MOSFET, because the current flow is located at the boundary between oxide and semiconductor. This is not the case for the BJT nor the HBT. In both cases the current flows inside the semiconducting substrate, where less traps are located.

A major type of noise sources in the BJT is the so-called shot noise. While equation 3.6 describes an average current through the transistor, the actual process in which electrons overcome the pn-junction occurs randomly. This results in fluctuations in the current flow. Shot noise thus describes the discrete nature of individual charge carriers and always occurs when these have to pass a potential barrier. In the BJT one can distinguish between two types of shot noise. The one, in the case of a npn-structure, which is associated with electrons passing the emitter-base junction generating the collector current [29]:

$$\frac{\mathrm{d}\langle v_{shC}^2 \rangle}{\mathrm{d}f} = 2qI_C \left(\frac{R_B}{\beta} + \frac{k_B T}{qI_C}\right)^2 \tag{3.12}$$

and the one, which originating from holes passing from the base to the emitter above the same junction:

$$\frac{\mathrm{d}\langle v_{shB}^2\rangle}{\mathrm{d}f} = 2qI_B R_B^2 \tag{3.13}$$

Accordingly, shot noise is a source of white noise, whereby equations 3.12 and 3.13 only hold below the cut-off frequency.

# 4 Electrical Devices and Circuits

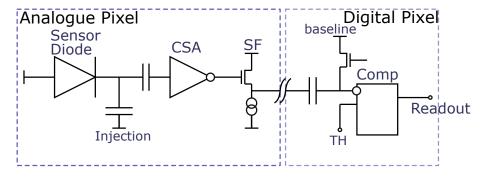

In the following chapter, the individual circuits of the front-end electronics of an HV-MAPS are described in sequence. Starting with the charge collection in the sensor diode and the core part, the charge sensitive amplifier. From there, along the signal line, the source follower and the comparator are described. These circuits together form the pixel front end electronics.

#### 4.1 Diode as a Sensor

One application of the diode can also be found outside of its typical electrical usage. In the scope of particle physics and consequently also the Mu3e experiment, the reversed biased diode is frequently used for particle detection [30]. The operation principle is based on the interaction between charged particles, whereby here only the detection of electrons and positrons is considered.

An electron or positron passing material will deposit part of its energy on the way through, due to the electromagnetic interaction between the particle and the material. The leading contributor to the energy loss is ionization. Thereby, the mean energy loss can be described by the Berger-Seltzer-formula [31]:

$$\left\langle \frac{dE}{dx} \right\rangle = \rho \frac{0.13536}{\beta^2} \frac{Z}{A} \cdot \left( B_0(T) - \log(\frac{I}{m_e c^2}) - \delta \right) \tag{4.1}$$

Here  $B_0(T)$  describes the stopping power, dependent on the material and momentum and I the material dependent mean excitation energy. Moreover, there are the material density  $\rho$ , the ratio of protons and nucleons Z/A and the density correction  $\delta$ .

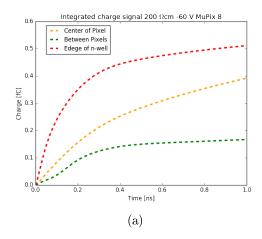

In a semiconductor the deposited energy creates electron-hole-pairs, whereby the average activation energy for a pair is approximately 3.6 eV [32] in silicon. Accordingly, electron hole pairs will be created along the path of the traversing particle. Due to the electric field present in the reversed biased diode, the pair get separated and the single charge carriers drift along the field lines. Hence, holes drift to the p-side and electrons to the n-side of the junction. As the electric field is only present inside the depletion zone, only charge inside this volume is collected. Pairs created in the remaining not depleted substrate are not separated and most probably recombine after a specific decay time.

It should be noted that the charge is mirrored in the electrodes. Therefore, the collection starts as soon as the pairs are separated and continues till all charge carriers reached the electrodes. The mean time of this process can be calculated,

using again the Drude model:

$$v_D = \mu \mathcal{E} \tag{4.2}$$

as discussed in section 2.2. Thus, the collection time of holes is larger, as their mobility  $\mu$  is smaller.

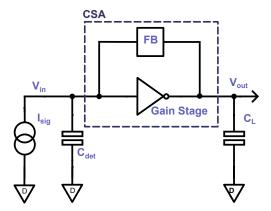

## 4.2 Charge Sensitive Amplifier

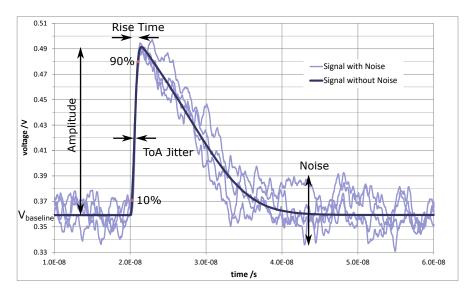

The most important circuity, in the scope of this thesis is the amplifier, or to be more precise, the charge sensitive amplifier (CSA) [23, 18, 27]. Later this circuit will be optimised in terms of the rise time (defined in section 6.4) of an amplified signal and its noise behaviour. Therefore, it is crucial to understand its operation principal and the expected noise.

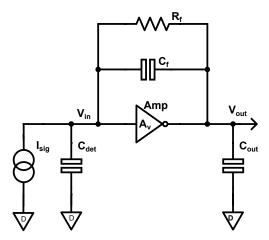

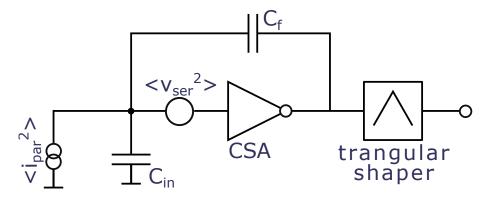

Figure 4.1: Principle of a charge sensitive amplifier.

In general, an amplifier is defined by its open loop gain  $A_v$ , which is the pure gain, given by the ratio of the output and the input voltage. In order to influence the voltage gain, typically a feedback circuit is introduced. It connects the output and input node of the amplifier. In this case the gain is referred to as closed loop gain. By using a capacitance as a feedback, the input current is integrated, forming a CSA.

A basic schema of the CSA is shown in figure 4.1. Starting within an ideal picture, the CSA consists of an ideal amplifier with an infinite inverse voltage gain  $-A_v$  and an infinite input impedance. In addition, a feedback capacity  $C_f$  and a feedback resistance  $R_f$  are used. The purpose of  $R_f$  is to bring the circuit to its operation point. Hence, the feedback resistance can be assumed to be very high and it does not contribute to the rising edge of a signal. But the falling edge is shaped by the resistance to decay with the time constant  $\tau = C_f R_f$ . On the input side of the CSA an ideal current source and a capacity  $C_{det}$  are connected. These represent a signal

coming from a sensor diode.  $C_{out}$  is a load capacity, modelling the circuit connected subsequently.

For an infinite voltage gain  $A_v$  the input node of the CSA is a virtual ground, meaning the voltage is fixed by the amplifier and can not change. Charge  $Q_s$ , induced by the current source, can therefore only flow to the feedback capacity  $C_f$ . There the charge causes a voltage drop and defines the output voltage  $V_{out} = -Q_s/C_f$  accordingly.

For a finite voltage gain  $A_v = V_{out}/V_{in}$ , the assumption of a virtual ground is not accurate. In this case an effective input capacitance  $C_{eff} = (1 + A_v)C_f$  can be defined. The virtual increase of the feedback capacity is called the Miller effect[33] and occurs because on the side of the output node,  $C_f$  sees a large signal with inverted phase. The signal charge is distributed between the effective capacitance and all other capacitances  $C_{in} = C_{det} + C_{amp,in} + C_{para}$  at the input side of the amplifier. These are the capacity of the sensor diode  $C_{det}$ , the real input capacity of the amplifier  $C_{amp,in}$  and possible parasitic capacities  $C_{para}$ . Hence, the signal amplitude at the output is reduced according to [27]:

$$V_{out} = -\frac{Q_s}{C_f} \frac{1}{1 + 1/A_v + C_{in}/(A_v C_f)}$$

(4.3)

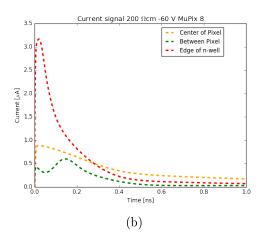

### 4.2.1 Single Gain Stage

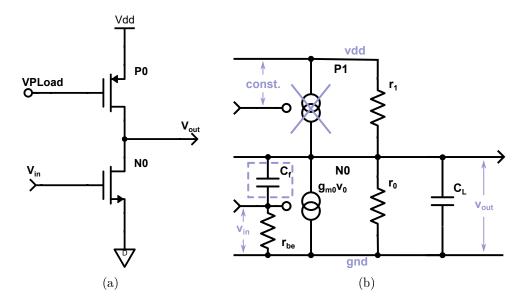

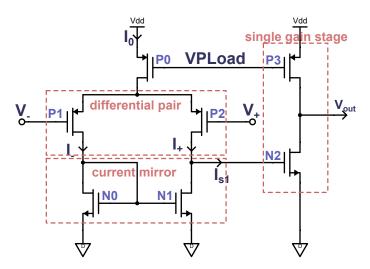

Previously the amplifier was considered a black box with a certain gain. In the following, actual amplifier circuits are discussed, starting with the single gain stage [34]. This type of amplifier is the simplest design, consisting of only two transistors, as shown in figure 4.2(a). In this case the NMOS transistor is the input transistor, connected in the common-source configuration and amplifying the signal accordingly to its transconductance  $g_m$ . The second transistor, a PMOS, acts as a current source for the circuit. There are several options to build up a single gain stage: Also possible is to use an npn-BJT as an input transistor or exchange the functionalities of the N- and PMOS in the circuit.

In order to understand the behaviour of the circuit, it is helpful to investigate its small signal model. For this purpose, the operation point of the circuit is fixed and only small variations in voltage v and current i are observed. In this approximation the electrical components of the circuit can be expressed linearly. Hence, a transistor is represented by a voltage controlled ideal current source and the transistor's output resistance. Accordingly, for the MOSFET applies  $i_d = g_m v_{gs}$  and the channel resistance is given by  $r_{ds}$ . Similar holds for a BJT, with a current  $i_c = g_m v_{be}$  and resistance  $r_{ce}$ . Additionally, the base current needs to be taken into account in the case of the BJT. Therefore, an additional resistance  $r_{be}$  is used.

In the following, all equations, if not marked otherwise, are given independently of the type of transistor used. For this reason, output resistance and current are labelled  $r_n$  and  $i_n = g_{mn}v_n$  respectively, where n is given by the transistor number in the corresponding circuit.

Figure 4.2: Represented is the circuit of a single gain stage with an NMOS input (a) and the corresponding small signal model (b). Additionally, a load capacity  $C_L$ , a feedback capacity  $C_f$  and the base resistance  $r_{be}$  are included in (b). Latter only exists in the case of a BJT input.

The small signal model for a single gain stage is represented in figure 4.2(b), including a load capacity  $C_L$ . As indicated there, the current source representing P0 can be neglected, because its gate-source voltage does not change in the small signal picture.

By using Kirchhoff's first law the circuit, initially without the feedback capacity  $C_f$ , in figure 4.2(b) can be solved for its transfer function [34]:

$$H(s) = \frac{V_{out}}{V_{in}} = -\frac{g_{m0}r_0}{1 + s r_0 C_L}, \quad \text{for } r_1 >> r_0$$

(4.4)

Whereby  $s = i\omega$  is the complex frequency, with the imaginary unit i and the angular frequency  $\omega$ . The transfer function models the output  $V_{out}$  of the amplifier for all possible input signals  $V_{in}$ . Based on the transfer function the dc-gain  $H(0) = A_v = -g_{m0}r_0$ , the cut-off frequency  $\omega_t = 1/(C_L r_0)$  and the unity gain bandwidth  $GBW = A_v \omega_t = g_{m0}/C_L$  can be derived. Latter is the product of the gain and the bandwidth, describing the point at which the gain of the amplifier equals one. Meaning it is an indicator for the maximum speed of the amplifier. In this sense, it is comparable to the transit frequency of a single transistor.

Assuming the input transistor is operated in the saturation mode, its transconductance is given by

$$g_{m,NMOS} \approx \sqrt{2\mu_n C_{ox} I_D W/L}$$

(4.5)

for the case of an NMOS and

$$g_{m,BJT} = qI_C/k_BT (4.6)$$

for a BJT input. Hence,  $g_m$  scales in both cases with the current inside the transistor, while the BJT benefits more from an increasing current. This behaviour also reflects in the unity gain bandwidth. On the other hand the output resistance is in both cases proportional to  $r_n \sim 1/I$ . Accordingly, the dc-gain does not benefit from a larger current, in the case of a MOSFET it will even decrease.

In order to operate the single gain stage as a CSA, a feedback capacity is necessary. Therefore, the influence of this capacity can be studied, using the small signal model with additional  $C_f$ . For the transfer function then applies:

$$H(s) = \frac{sC_f r_0 - g_{m0} r_0}{1 + s r_0 (C_L + C_f)}, \quad \text{for } r_1 >> r_0$$

(4.7)

Hence, the feedback capacity reduces the unity gain bandwidth  $GBW = g_{m0}/(C_L + C_f)$ . Note that  $C_f$  is increased by the Miller effect, as discussed above, and is replaced by the effective capacity  $C_{eff} = (1 + A_v)C_f$ . This results in a significant limitation at high frequencies.

### 4.2.2 Cascode Amplifier

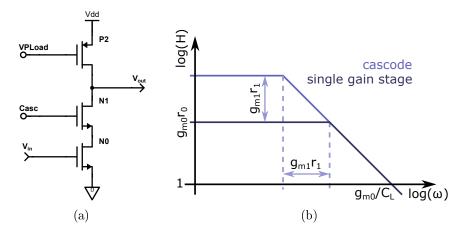

The cascode [34] is a concept to increase the gain of the amplifier further. Thereto, a second transistor is introduced between the output node and the input transistor, as shown in figure 4.3(a). Again it is possible to use various types of transistors to build up the cascode circuit.

Figure 4.3: Shown is the circuit of a single gain stage with additional cascode transistor (a). On the right side (b), the influence of the cascode on the transfer function is indicated [34].

The cascode adds mainly two advantages to the circuit. First, it acts as a second stage of amplification, which can be proven by investigating the small signal behaviour. The transfer function is given by [34]:

$$H(s) \approx -\frac{g_{m0}r_0 \times g_{m1}r_1}{1 + s \, r_0 q_{m1} r_1 C_L}, \quad \text{for } g_{mn}r_n >> 1$$

(4.8)

Whereby variables marked with the index 1 indicate the cascode transistor.

For the dc-gain, equation 4.8 yields to  $A_v = g_{m0}r_{ds0} \times g_{m1}r_{ds1}$ , which is a significant increase in comparison to the single gain stage. However, the unity gain bandwidth is not influenced by the additional transistor, which can be seen in figure 4.3(b).

The cascode adds a second advantage, not covered by the small signal model. The cascode transistor fixes the drain voltage of the input transistor to a nearly constant value, making it independent from changes at the output node. Hence, parasitic feedback capacities in a real input transistor are not affected by the Miller effect. This is unfortunately not true for the feedback capacity in the CSA, which is still located between the input and output node.

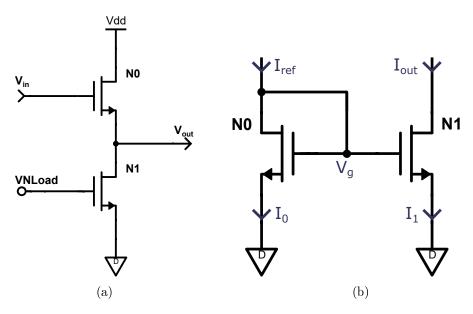

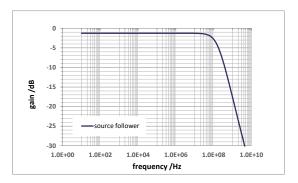

### 4.3 Source Follower

The output impedance of the CSA is approximately given by the resistance of the current source, which is typically very high. Therefore, the CSA is suited best to drive high impedance loads, in order to minimize power loss. For the case of a small load impedance, thus an additional circuit is necessary to match the impedance between CSA and its load. For this purpose, the so-called source follower [34, 35] circuit is suitable. Its consist of two transistors, whereby one is operated in the common-drain configuration and the second acts as a current source. The related circuit of the source follower is represented in figure 4.4(a).

Figure 4.4: Display of a source follower (a) and a current mirror (b) circuit. Both circuits are build up with NMOS transistors.

Essential parameters of the circuit can be calculated within the approximation of the small signal model. The output impedance is given by  $r_{out} = r_1/(g_{m0}r_1 + 1) \rightarrow 1/g_{m0}$  for  $g_{m0}r_1 >> 1$ . Typically, the transistor N0 is operated in the saturation

region, leading to the equation  $g_m \sim \sqrt{I_D W/L}$ . Hence, the output impedance can be adjusted by varying the size of the input transistor and the current flowing inside. Besides, the input is a MOSFET, so in first approximation no input current flows and the input impedance approach infinity. The case of a bipolar transistor as an input will be not discussed.

The dc-gain of the circuit can be again derived from the transfer function:

$$H(s) \approx \frac{g_{m0}r_0}{1 + g_{m0}r_0 + sr_0C_L}, \quad \text{for } r_1 >> r_0$$

(4.9)

It is  $A_v = \frac{g_{m0}r_0}{1+g_{m0}r_0} \to 1$  for  $g_{m0}r_0 >> 1$ . In summary, the circuit is used to transfer the impedance from a high to a low value without internal loss. Of course this is only true in the first approximation. Effects such as the Body effect [35] cause the gain to fall below unity, leading to losses. The Body effect always occurs when there is a difference between the source and the substrate potential. It results in a shifting of the threshold voltage of the transistor, due to the increase of the depletion zone at the source terminal with increasing source-substrate voltage. In the source follower this effect occurs when a signal is transferred, yield to a non-linearity in the signal response of the circuit.

### 4.4 Current Mirror

The current mirror is not a circuit for processing a signal but an assistance, used inside other circuits. Nevertheless, it will be explained shortly. Like the name already indicates, the purpose is to mirror a current from one branch into another. In that sense, it is often used to distribute supply currents without power losses.

On the reference side of the circuit a diode connected transistor is used, as it is shown in figure 4.4(b). By connecting the gate and the drain terminal of the transistor, it is fixed in saturation mode, since  $V_{DS} > V_{GS} - V_{th}$  is always fulfilled for  $V_{DS} = V_{GS}$ . Additionally,  $V_{GS}$  will automatically adjust such that the reference current  $I_{ref}$  can flow through the transistor, due to the diode connection.

The gate potentials of the transistors in the reference and the working branch are shared. Hence both transistors are operated with the same voltage  $V_{GS}$  and their current is given by equation 3.4. Thus, the ratio of the currents  $I_1/I_0$  in both branches is determined by the ratios of the lengths  $L_0/L_1$  and the widths  $W_1/W_0$ , whereby differences occur only because of the channel length modulation.

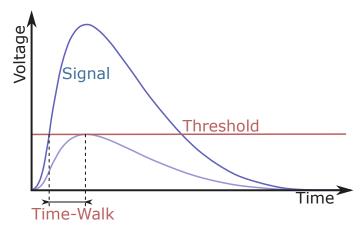

## 4.5 Comparator

An application example for the current mirror within another circuit is the comparator [34]. It is essential circuitry to convert analogue signals into digital signals, by comparing two input signals.

Figure 4.5: Circuit diagram of a comparator, marked are the different parts and bias voltages.

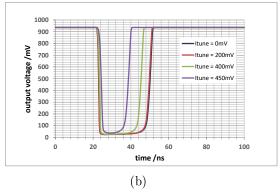

A comparator circuit is shown in figure 4.5, consisting of a differential pair, a current mirror and a single gain stage as output stage. Also possible is a source follower as output stage. The input signals are  $V_+$  and  $V_-$ , connected to the differential pair.

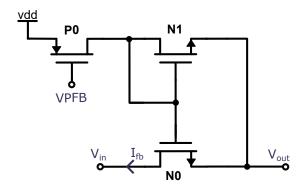

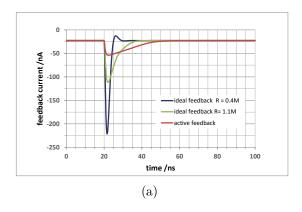

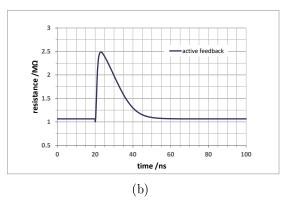

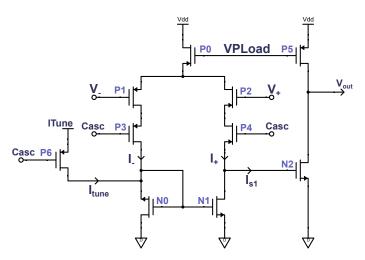

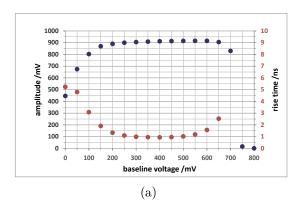

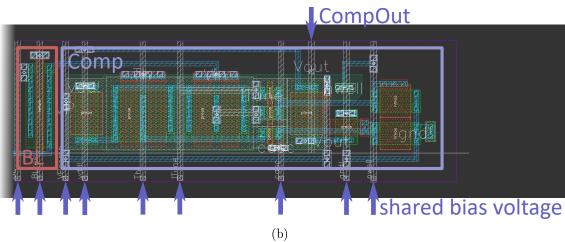

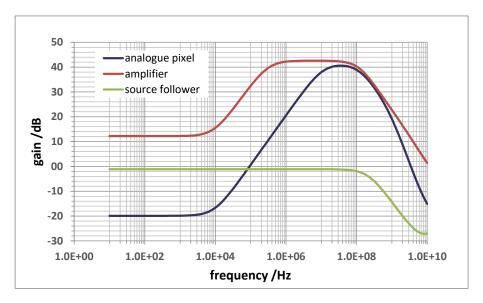

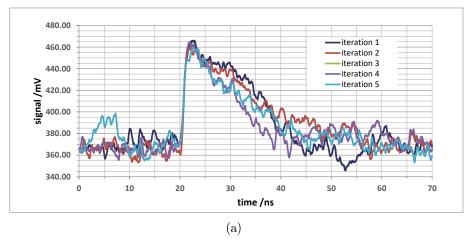

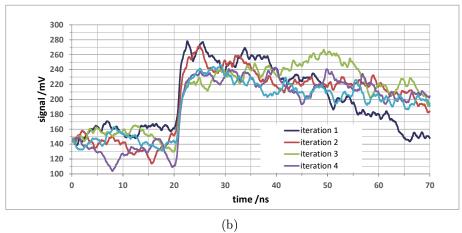

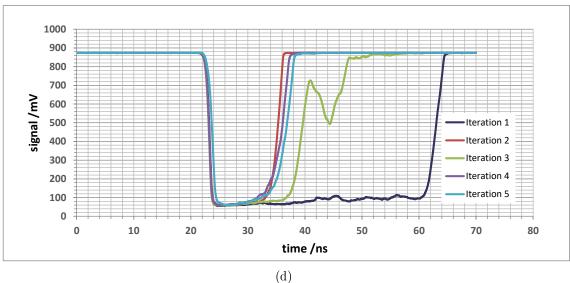

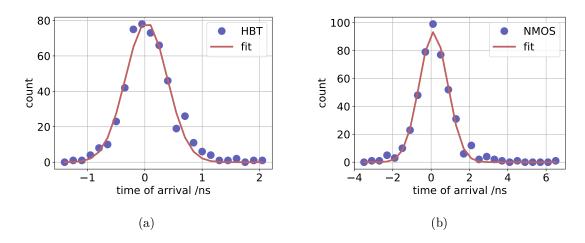

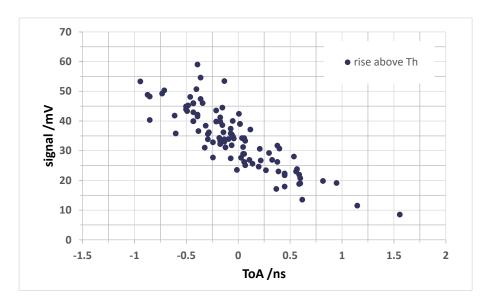

To start with, equal input potentials  $V_+ = V_-$  are assumed. Both transistors of the differential pair see the same gate-source voltage and therefore conduct the same current. In this case the equation  $I_+ = I_- = I_0/2$  holds, whereby  $I_0$  is determined by P0, which acts as a current source. The output current of the fist stage, flowing into the gain stage is  $I_{s1} = I_+ - I_- = 0$ , since the current mirror only allows for a current flow of  $I_+$  in the output branch. The potential at this fist stage output node depends on the actual voltage level of  $V_+$  and  $V_-$ . The comparator can only work if the input voltage is sufficiently low, otherwise the differential pair will switch-off. Similar, it hast to be sufficiently high, hence the transistors are not saturated.