Dissertation submitted to the Combined Faculties for the Natural Sciences and for Mathematics of the Ruperto-Carola University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

> Put forward by Dottore in Fisica Massimiliano De Gaspari born in Mirano, Italy Oral examination: July 25, 2012

ii

# Systems-on-Chip (SoC) for applications in High-Energy Physics

Referees: Prof. Dr. Johanna Stachel Prof. Dr. Peter Fischer iv

### Zusammenfassung

#### Systems on Chip (SoC) für Hochenergiephysik-Anwendungen

In Hinblick auf die Time Projection Chamber (TPC) für den geplanten Linear Collider (LCTPC) wurde ein neuer, anwendungsspezifischer integrierter Schaltkreis für das Front-End entwickelt: der 16-Kanal Super-Altro Prototyp. Aufgrund der geringen verfügbaren Fläche von 1×4mm<sup>2</sup> pro Kanal wurde der Chip als kompaktes integriertes System realisiert, welches der Vorverstärkung der analogen Eingangssignale, der Impulsformung, der 10bit Analog-Digital-Wandlung, sowie der digitalen Signalverarbeitung dient. Geeignete Designtechniken wurden verwendet, um die Kopplung zwischen Analog- und Digitalteilen des Systems zu verringern. Der Schaltkreis ist für das Bunch-Train-Regime des Linear Colliders optimiert; die Stromaufnahme ist durch die Verwendung von Power-Pulsing stark reduziert worden. Die durchgeführten Tests zeigen ein Rauschen von lediglich 316 Elektronen,

sowie die Funktionalität der Power-Pulsing Technik. Der Super-Altro kann sowohl für das Auslesen von Gasdetektoren mit Drahtkammern, als auch mit GEMs oder MicroMegas, eingesetzt werden.

Diese Dissertation behandelt unter anderem auch Analog-Digital-Wandler (ADC), geeignet für Front-End Systeme in der Hochenergiephysik. Simulationen zeigen die Realisierbarkeit von 12-bit 100MHz Pipeline ADCs, in einer 130nm CMOS Technologie.

### Abstract

#### Systems on Chip (SoC) for applications in High-Energy Physics

In view of the Time Projection Chamber for the future Linear Collider (LCTPC), a new front-end Application-Specific Integrated Circuit has been developed: the 16 channels Super-Altro Demonstrator. Given the small pad area of  $1 \times 4$ mm<sup>2</sup>, the chip is a compact integrated system, including signal preamplification/shaping, 10-bit analog-to-digital conversion and digital signal processing. Adequate design techniques were used to reduce noise coupling between analog and digital parts of the system. The bunch train structure of the linear collider is exploited by the introduction of power pulsing features in the design, which result in a significant reduction of the power consumption. The tests carried out show noise as low as 316 electrons and effectiveness of the power pulsing approach. Super-Altro can be used for studies of gaseous detector readout with classical wire chambers as well as modern GEMs and MicroMegas.

This thesis also studies Analog-to-Digital Converters (ADC) suitable for integration in High-Energy Physics front-end systems. Simulations show the feasibility of a 12-bit 100MHz pipeline ADC in a 130nm CMOS technology.

### Acknowledgements

I want to thank Prof Stachel for offering me this PhD opportunity, for her support and in particular for her invaluable help when I had to take important decisions. I also want to thank Prof Fischer, who kindly accepted to be the second referee for this thesis, and the other members of the Committee: Prof Komnik and Prof Männer.

My first thoughts go to my parents and my sister Sara, who where always there when I needed them, and to Angela, an infinite source of encouragement.

Many thanks to my direct supervisors Paul Aspell, Luciano Musa and Hans-Kristian Soltveit for their support and guidance. Thanks also to other people who made my experience at CERN possible: Lucie Linssen, Alessandro Marchioro, Jorgen Christiansen, Philippe Farthouat.

From Heidelberg I thank and greet the whole KP group, in particular my office mates Sara and Rachik. Thanks to the friends who made the years in Heidelberg unforgettable: Giuliana, Katharina, Lisa, Malte, Sascha, Wiebke. Among the many flatmates, I thank Angelika, Pia, Ricardo, Steffen and Valérie, with whom I shared not only a flat, but a life experience. I want to thank also the AEGEE students' association for their many funny activities, the staff of the Internationales Studienzentrum (Max-Weber-Haus) and of the Zentrales Sprachlabor, for the interesting German and English courses.

From CERN, I would like to express my deepest gratitude to the whole Microelectronics group and to the many people in the ALICE TPC group who helped a lot, especially during the testing activities. Of course, a huge thank you goes to the other designers of the Super-Altro team: Christian, Eduardo and Hugo. Out of the many, I would like to thank my office mates David, Maria, Michal, Rafael and Winnie, with whom I shared every day pain and joy. Thanks to the flatmates in Saint Genis: Andrew, Christopher, Georg, Philipp, Serena; together we had the terrific experience of an all-physicists flat.

From Padova, I would like to thank my friends, those members of the PAPA Association, especially Eduard for his many suggestions.

Thanks also to the staff and the sporty friends of my athletics, ski and swimming clubs.

viii

## Contents

| 1        | Intr | roduction                                                    | 1  |

|----------|------|--------------------------------------------------------------|----|

|          | 1.1  | The present: CERN, the LHC, and ALICE                        | 1  |

|          |      | 1.1.1 Wire chambers, GEMs, MicroMegas                        | 2  |

|          | 1.2  | Front-end architectures for detectors                        | 3  |

|          |      | 1.2.1 Binary chips                                           | 3  |

|          |      | 1.2.2 Analog memories                                        | 3  |

|          |      | 1.2.3 DSP chips                                              | 4  |

|          |      | 1.2.4 Comparison between the three front-end architectures . | 4  |

|          | 1.3  | The future: FAIR, ILC/CLIC                                   | 5  |

|          |      | 1.3.1 Motivation for this work                               | 6  |

|          |      | 1.3.2 Summary of the thesis                                  | 7  |

| <b>2</b> | Tec  | hnological overview                                          | 11 |

|          | 2.1  | The MOS transistor                                           | 11 |

|          | 2.2  | Noise                                                        | 16 |

|          | 2.3  | Short-channel                                                | 17 |

|          |      | 2.3.1 Effects and model                                      | 17 |

|          |      | 2.3.2 Leakage currents                                       | 18 |

| 3        | Ana  | alog-to-digital converter                                    | 21 |

|          | 3.1  | Specifications                                               | 21 |

|          |      | 3.1.1 Quantization error                                     | 21 |

|          |      | 3.1.2 Transfer curve of an ADC and non-linearity             | 22 |

|          |      | 3.1.3 Signal-to-noise ratio                                  | 23 |

|          | 3.2  | ADC architectures                                            | 24 |

|          |      | 3.2.1 Successive Approximation Register                      | 24 |

|          |      | 3.2.2 Flash                                                  | 24 |

|          |      | 3.2.3 Pipeline                                               | 25 |

|          |      | 3.2.4 Delta-Sigma (Oversampling)                             | 25 |

|          |      | 3.2.5 Architecture choice                                    | 26 |

|          | 3.3  | The pipeline architecture                                    | 27 |

|          |     | 3.3.1 Multiplying Digital-to-Analog Converter                                                                                           |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

|          |     | 3.3.2 Sample and multiply capacitors                                                                                                    |

|          |     | 3.3.3 Stage downscaling                                                                                                                 |

|          |     | 3.3.4 Noise                                                                                                                             |

|          |     | 3.3.5 Amplifier requirements                                                                                                            |

|          | 3.4 | Amplifier                                                                                                                               |

|          |     | 3.4.1 Architecture choice                                                                                                               |

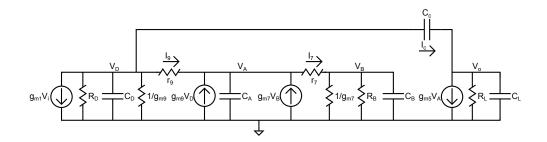

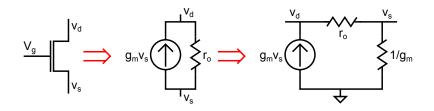

|          |     | 3.4.2 Small-signal model                                                                                                                |

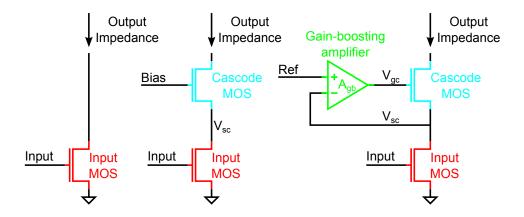

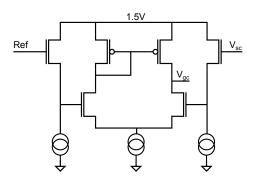

|          |     | 3.4.3 Gain boosting $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 45$                                          |

|          |     | $3.4.4  \text{Simulations}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                            |

| 4        | Des | ign of the Super-Altro Demonstrator 53                                                                                                  |

|          | 4.1 | Programmable pre-amplifier shaper                                                                                                       |

|          |     | 4.1.1 ESD protections                                                                                                                   |

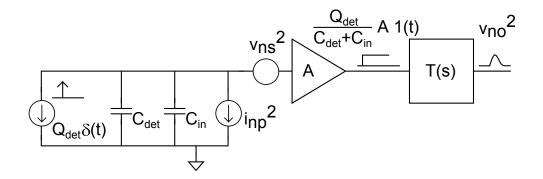

|          |     | 4.1.2 Noise in the PASA                                                                                                                 |

|          |     | 4.1.3 Filters and power consumption 60                                                                                                  |

|          | 4.2 | ADC                                                                                                                                     |

|          | 4.3 | Bias circuitry for the ADCs                                                                                                             |

|          | 4.4 | Digital Error Correction                                                                                                                |

|          | 4.5 | Digital Signal Processing block                                                                                                         |

|          |     | 4.5.1 Interface and system timing                                                                                                       |

|          | 4.6 | Timing and clock tree                                                                                                                   |

|          | 4.7 | Testability $\ldots \ldots 85$ |

|          | 4.8 | Floorplan and layout                                                                                                                    |

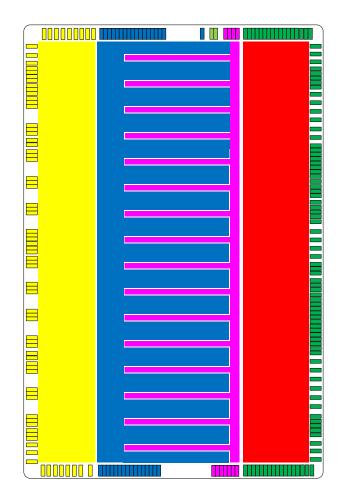

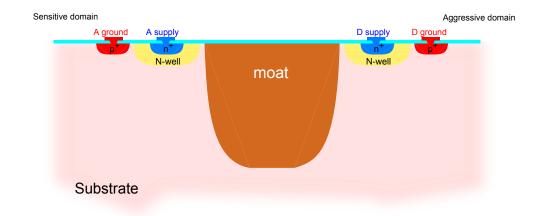

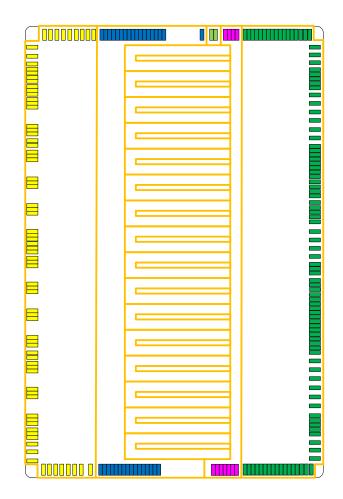

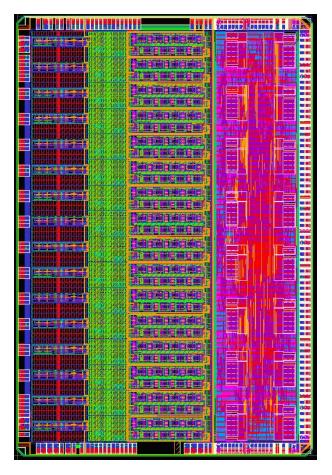

|          |     | 4.8.1 Noise coupling, power domains and substrate isolation 92                                                                          |

|          |     | 4.8.2 Final layout and packaging                                                                                                        |

|          | 4.9 | Top-level simulation                                                                                                                    |

| <b>5</b> | Sup | per-Altro tests 103                                                                                                                     |

|          | 5.1 | Test plan                                                                                                                               |

|          |     | 5.1.1 Testing the power pulsing features                                                                                                |

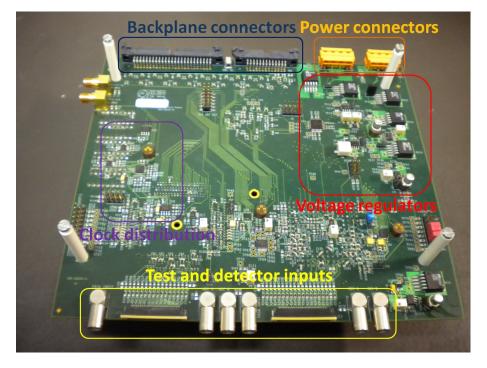

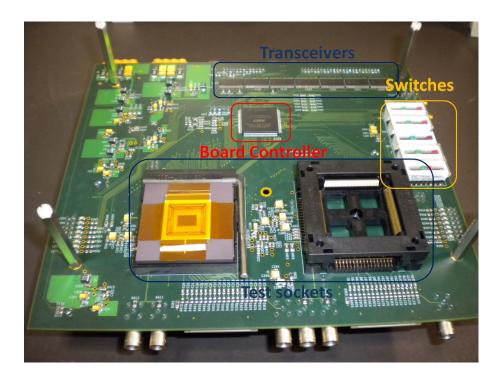

|          | 5.2 | The Super-Altro test board                                                                                                              |

|          |     | 5.2.1 Concept of the test board                                                                                                         |

|          |     | 5.2.2 Design of the test board                                                                                                          |

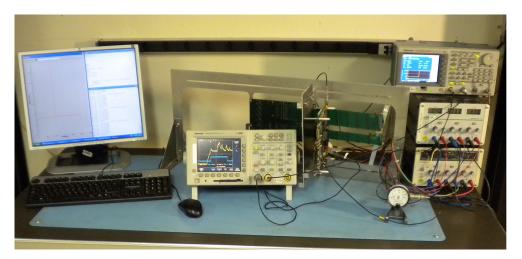

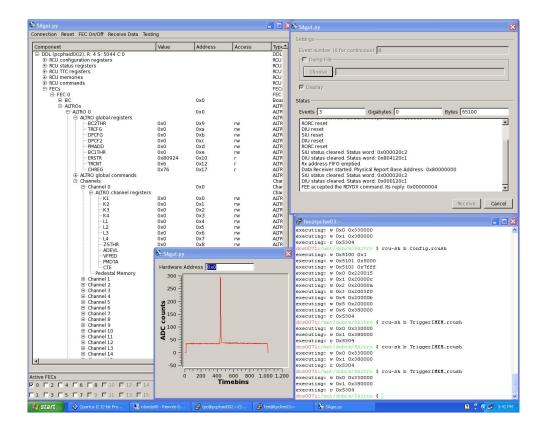

|          |     | 5.2.3 Test setup                                                                                                                        |

|          | 5.3 | Test results                                                                                                                            |

|          |     | 5.3.1 Analog tests $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $113$                                        |

|          |     | 5.3.2 Digital tests                                                                                                                     |

|          |     | 5.3.3 Power measurements and power pulsing tests 120                                                                                    |

|          |     |                                                                                                                                         |

### CONTENTS

| 6            | Conclusions and outlook |                                    |     |  |  |

|--------------|-------------------------|------------------------------------|-----|--|--|

|              | 6.1                     | Conclusions                        | 125 |  |  |

|              | 6.2                     | Outlook                            | 126 |  |  |

| $\mathbf{A}$ | Am                      | plifier small-signal models        | 129 |  |  |

|              | A.1                     | Miller compensation                | 130 |  |  |

|              | A.2                     | Compensation on the cascoded load  | 137 |  |  |

|              | A.3                     | Compensation on the cascoded input | 142 |  |  |

| в            | Verilog-AMS models 14   |                                    |     |  |  |

|              | B.1                     | PASA                               | 149 |  |  |

|              |                         | ADC                                |     |  |  |

|              |                         | B.2.1 ADC 1.5bit Stage             |     |  |  |

|              |                         | B.2.2 Flash ADC 2bit               |     |  |  |

|              | B.3                     | Clock Tree                         |     |  |  |

| $\mathbf{C}$ | Clo                     | ck Tree                            | 157 |  |  |

| Bi           | Bibliography            |                                    |     |  |  |

### xi

CONTENTS

xii

## Chapter 1

## Introduction

## 1.1 The present: CERN, the LHC, and ALICE

The European Organization for Nuclear Research (CERN) [Ce] operates the world's most powerful particle accelerator, the Large Hadron Collider (LHC) [LHC]. This facility accelerates and collides alternatively protons, currently at an energy of 3.5TeV (design energy 7TeV), or lead ions, currently at 2.76TeV per nucleon (design energy 5.5TeV/nucleon); the bunch crossing is synchronized with the global clock, at a frequency of 40MHz.

A Large Ion Collider Experiment (ALICE) [AL1] is located at one of the collision points along the LHC, and targets primarily Pb-Pb collisions. The main tracking and particle identification sub-detector of ALICE is the Time-Projection Chamber (TPC). The TPC has the shape of a cylinder, whose axis is on the trajectory of the LHC beam. In the middle of the cylinder, perpendicular to the beam, a central electrode is kept at a high positive voltage; particles resulting from collisions ionize the gas in the TPC along their trajectory, which is bent by a magnetic field; the ionization produces electrons, which drift towards one of the end caps of the TPC, under the action of a uniform electric field generated by the high voltage electrode. Detecting the arrival area of these electrons on the endplate gives information

on the trajectory of the ionizing particle; thus, the momentum of the particle can be inferred. At the same time, the amount of charge collected gives a measure of the energy loss per unit length (called dE/dx). A combination of momentum and dE/dx measurements is used to identify the initial particle originating from the collision.

### 1.1.1 Wire chambers, GEMs, MicroMegas

The charge generated through ionization by the initial particle is small and must be amplified and detected. Three main architectures are used for this scope: Multi-Wire Proportional Chamber (MWPC), Gas Electron Multiplier (GEM), Micro-MEsh GAs detector (MicroMega).

The readout of the ALICE TPC is based on MWPC.

Using MWPC, electrons drift towards the end cap, where they find anode wires [Ro, 3]. The electrical field in the proximity of the anodes increases, and avalanches occurs; therefore, the initial electrons produce many more electron-ion pairs. The TPC end cap is populated by metal pads where these charges induce an electrical signal. Electrons reach immediately the anode wires, while ions are much slower; a gating grid is added between the drift volume and the anode wires to prevent the backflow of ions towards the central electrode. The positive signal induced on the pads has a fast rise and a slow fall (tenths of microseconds), due to the slower ions (ion tail). Each pad is connected with a dedicated Front-End Electronics module (FEE), for the amplification, filtering and measurement of the signal; in ALICE, the connection is done with kapton cables, and the FEE is composed of Pre-Amplifier Shaping Amplifier (PASA) and ALICE TPC ReadOut chip (ALTRO). The minimum pad size of the ALICE TPC is 7mm×4.5mm.

The Gas Electron Multiplier [Sa] is a thin polymer foil, coated on both sides with metal. Holes with diameter of the order of  $70\mu$ m are regularly distributed across the foil. A voltage difference, applied between the two metal coatings, creates an intense electric field in the hole regions. Electrons arriving from the drift region are multiplied by the avalanche, which occurs due to the high electric field. Afterwards, the resulting electrons continue their trip towards the pads on the end cap of the detector.

Signals produced by GEMs are only due to electrons; therefore they are negative, fast and do not present any ion tail; the duration of signals is in the order of a few tenths nanoseconds.

MicroMegas [CD] replace the anode wires of a MWPC with a metallic mesh, which is held by insulating pillars at a very short distance (in the order of 100 $\mu$ m) from the pad plane. A high voltage applied to the mesh creates an amplification region between the pad plane and the mesh itself; electrons resulting from the avalanche travel towards the pads, while the corresponding ions are collected by the mesh.

Signals produced with MicroMegas have a fast rise due to electrons and a tail due to ions. The important point is that, given the short distances, the collection of ions is much quicker than in MWPC, in the order of 100ns.

### **1.2** Front-end architectures for detectors

There exist three main categories of chips for the read-out of signals produced by detectors:

- **Binary chips:** each analog signal is converted in a digital line by a discriminator. This architecture has low power consumption and produces a simple digital output.

- **Analog memories:** the analog signal is sampled on capacitors, and later sent off-chip to an external ADC.

- **Digital Signal Processing (DSP) chips:** the analog signal is sampled, and each sample is converted in a digital word. This allows further processing of the signal in the digital domain. Zero suppression reduces the amount of data and discards non relevant data.

Some examples of existing chips, using the three different architectures, are given in the next paragraphs.

### 1.2.1 Binary chips

In a binary chip like VFAT2 [A1], an analog front-end amplifies and shapes the signals coming from a detector. The resulting pulse is fed to a discriminator, which performs the comparison with an analog threshold and generates a digital output. A "fast OR" of the outputs of all 128 channels generates a trigger output. Moreover, VFAT2 offers a tracking function, where it tells which channels have been hit after a given trigger.

Another interesting binary chip is the TimePix [L1]. The architecture of the front-end is based on a preamplifier followed by a discriminator; the digital output of the discriminator can be used in various operating modes. In particular, in Time-Over-Threshold (TOT) mode, a clocked counter measures the time duration of the signal being above threshold; this is proportional to the amplitude of the analog pulse, and, therefore, to the detected charge.

### 1.2.2 Analog memories

The PACE3 assembly [A2] is an example of analog memory. Pre-amplifier and shaper are followed by a Switched-Capacitor (SC) circuit with a set of 192 capacitors, which constitute an analog memory. At each clock period, a sample of the analog signal is stored on a different capacitor. After receipt of an external trigger, three capacitors are protected from overwriting; in this way, the analog memory saves the three consecutive samples which follow the trigger and contain the pulse. Later, the saved samples are buffered off-chip, where they are digitized by an external converter. The three samples allow some processing, e.g. baseline subtraction.

Another example of analog memory is N-XYTER [BB]: after a preamplifier, the signal is delivered to a fast shaper and to a slow shaper in parallel. Following the fast shaper, a discriminator generates a trigger, which provides digital information on the arrival time of the pulse. The slow shaper is followed by a peak detector, instead; the peak detector holds the maximum amplitude of the pulse, which is then stored across a capacitor in an analog memory.

With this architecture, N-XYTER is capable of self-triggering, and provides as outputs the sampled analog voltage together with the corresponding digital time stamp; an off-chip Analog-to-Digital Converter (ADC) is needed to digitize the analog sample.

### 1.2.3 DSP chips

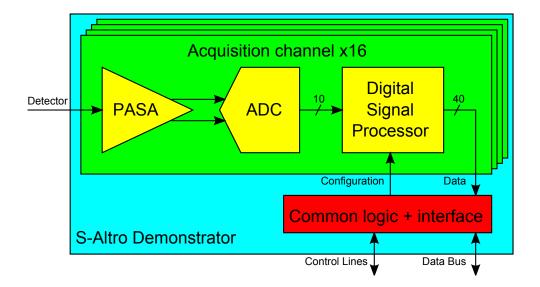

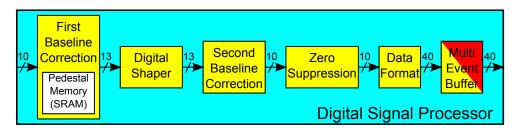

The ALTRO chip [Bl], is an example of DSP-based architecture, and it was initially developed for the Alice TPC. Each channel contains a 10bit pipelined ADC and a data processor, while another chip is needed to perform preamplification and shaping of the signal coming from the detector. A clock up to 20MHz triggers the sampling in the ADC; the samples are passed in a pipelined fashion to the data processor. The DSP part of the chip is similar to that of the Super-Altro, described in section 4.5; it allows correction of nonidealities or perturbations in the signal, e.g., systematic offsets or patterns, distortions of the pulse shape, temperature drifts, supply voltage variations. The large amount of data produced is reduced with a digital threshold for zero suppression: only the pulses exceeding the threshold are saved in the memories, and later read-out.

## 1.2.4 Comparison between the three front-end architectures

Binary chips have small size and power consumption per channel. They are particularly appealing when the detector is quiet and perturbations are small. They are not capable of filtering fluctuations of the baseline. With a negative fluctuation, the discriminator may not detect signals smaller than the fluctuation; with a positive fluctuation, the discriminator may be triggered even when no real signal is present. A solution is to increase the threshold; the discriminator would not detect fake events, but it would also miss many more real events.

If the system noise is considerable, it will also trigger the discriminator; a solution is, again, to increase the threshold, which leads to the loss of many small signals which do not exceed the threshold.

A purely binary readout provides only hit information, and no information on the signal amplitude, which is required in TPC applications. Therefore, it is not used in TPCs.

Analog memories allow some digital signal processing (PACE3) and selftriggering (N-XYTER). Their disadvantages are the maximum time they can hold the information and the difficulty in implementing zero suppression before storing the information in the memories.

The advantage of DSP-based chips is that they can filter fluctuations of the baseline; therefore, the threshold for the zero suppression can be kept at a minimum, allowing the detection of the smallest signals. Moreover, DSP chips can correct distortions of the signals due, for example, to long ion tails; this results in better measurements when pile-up of pulses occurs.

The drawback of DSP chips is that large power is needed for the ADCs and for the data processor.

## 1.3 The future: FAIR, ILC/CLIC

$1 \text{mm} \times 4 \text{mm}$ .

In the close future, a new accelerator facility will enter operation at the GSI Helmholtzzentrum für Schwerionenforschung GmbH (GSI) [GSI]. The Facility for Antiproton and Ion Research in Europe GmbH (FAIR) [Fa] will host the Compressed Baryonic Matter experiment (CBM) [CBM].

At the same time, new accelerators are under investigation for the post-LHC era. The International Linear Collider (ILC) [IL] and the Compact LInear Collider (CLIC) [CL] are two proposals of linear electron-positron colliders. In both cases, bunches of particles are grouped together in trains; in ILC, each train is about  $900\mu$ s long, and trains are repeated every 200ms (5Hz); in CLIC, the train duration is 156ns, and the train repetition rate is 50Hz (20ms). Therefore, front-end electronics do not need to be continuously powered, as in the LHC; a duty cycle can be applied to turn on the electronics only during collisions, thus dramatically reducing the power consumption. For ILC/CLIC there are two detector proposals: International Large Detector (ILD) [ILD] and Silicon Detector (SiD) [SiD]. The ILD includes a TPC, which is being developed in a collaboration named Time Projection Chamber for a future Linear Collider (LCTPC) [LT]; the pad size in the LCTPC is

### **1.3.1** Motivation for this work

The trend in microelectronics goes towards the implementation of Systems on Chip (SoC), where different analog and digital components are integrated on the same silicon die. SoC are compact solutions, which usually need less space and less power than multi-chip systems; they also reduce assembly costs, while improving reliability. Technology scaling decreases the area of digital circuitry; therefore, modern designs tend to increase the intelligence in a chip in terms of digital functionalities. The main drawback with SoC is signal integrity: coupling mechanisms between signals of different nature endanger the quality of analog signals.

In view of the experiments planned for the next years, a new SoC is under conceptual development. The signal coming from the detector is preamplified, and sent to two shapers in parallel, with different shaping times; gain, polarity and shaping times are programmable by the user. The fast shaper feeds a discriminator, which provides trigger and timing information. This front-end is replicated for many channels (32, 64 or 128). Upon reception of a trigger, the output of the corresponding slow shaper is routed to a peak detector, and the voltage held by the peak detector is converted to digital by an ADC.

Depending on the expected occupancy of the detector, an average number of channels will receive events in the same time interval, while the other channels will not register any relevant data. Therefore, a small set of peak detectors is sufficient; when an event is detected by the discriminator of a channel, the output of the slow shaper of that channel is routed to the next available peak detector. The same argument is applied to ADCs, which are a much smaller number than the channels.

The result is a self-triggering SoC, which outputs digital information on pulse heights with the corresponding time stamps. Some control logic implements the routing of analog signals from many channels to smaller sets of peak detectors and ADCs. The minimum numbers of channels, peak detectors and ADCs depend on the specific application, as well as the requirements of each functional block. The ADC, for example, can be designed with a high resolution, and can be maskable, so that the application selects the appropriate number of bits. Also the design sampling frequency can be high; in case a lower frequency is required, either the ADCs are clocked with the appropriate frequency, or some of them are masked, so that they do not consume power, while the operating ADCs provide the necessary speed.

For this thesis, the chosen ADC specifications are 12 bits of resolution and a maximum sampling frequency of 100MHz. These are demanding values, which push the design to the limits of the technology in use.

#### 1.3. THE FUTURE: FAIR, ILC/CLIC

In view of the future Linear Collider (ILC/CLIC), the development of a new DSP-type front-end chip has started. The basis is the ALTRO chip, evolving into a complete SoC: the Super-Altro. Given the small 1mm×4mm pads of the LCTPC, the ALTRO chipset, which includes the pre-amplifier in a separate chip, occupies too much area; a compact solution is required, where pre-amplifiers are integrated with ADCs and digital processor; this also implies that the technology used must be modern, in order to benefit from the small transistor size. Additionally, new designs have to take advantage of the bunch timing of the Linear Collider, including power pulsing features which decrease dramatically the power consumption of the system. Ongoing testing activities on GEMs and MicroMegas are also potential applications of the new SoC; in this case, a required additional feature is versatility, so that the chip can be used in a variety of configurations according to the specific needs.

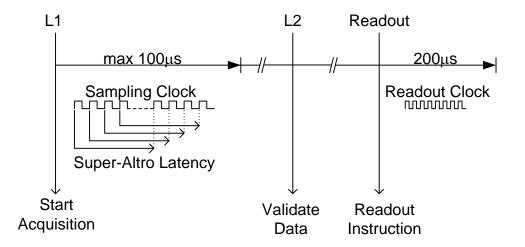

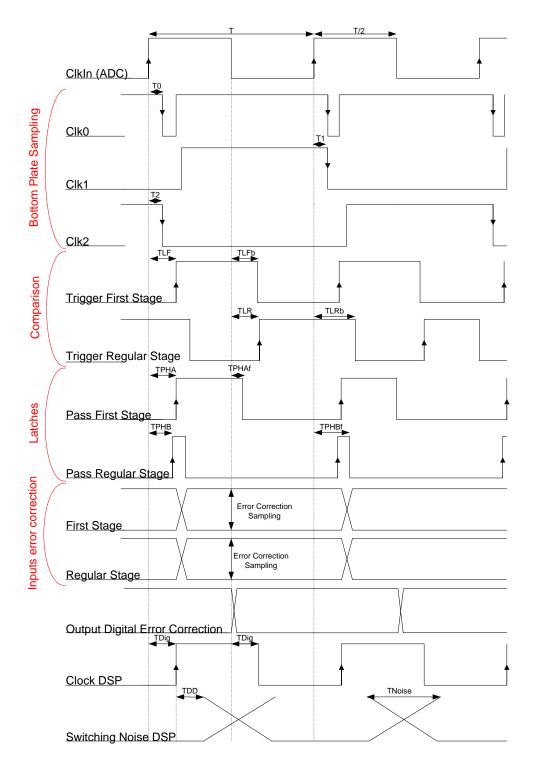

The 16 channels Super-Altro Demonstrator (S-Altro) addresses all these requirements. The pre-amplifier and shaper is programmable in terms of gain, polarity and shaping time. The detected charge spans from a Minimum Ionizing Particle (MIP) of 4.8fC (30000 electrons) to a maximum of 30MIP (900k electrons); a good Signal-to-Noise Ratio (SNR) is achieved with noise lower than 1000 electrons, which sets a requirement for the pre-amplifier. An ADC with a resolution of 10 bits ( $2^{10} = 1024$ ) fits best the dynamic range between the acceptable noise and the maximum charge. The minimum shaping time of 30ns sets a condition on the maximum sampling frequency of the ADC: in order to collect at least one sample during the rising edge of the pulse, the ADC must operate up to 40MHz. Another important aspect of the design is that the communication protocol of the S-Altro must be compatible with the ALTRO protocol, so that existing systems developed for ALTRO can be easily updated to the new front-end.

### 1.3.2 Summary of the thesis

The work presented in this thesis is based on a modern 130nm CMOS technology. An understanding of the devices and effects present when designing with such technology is necessary. **Chapter 2** reviews the theory of operation of transistors in modern technologies.

A feasibility study of the ADC introduced in the previous paragraph has been done, and is described in **chapter 3**:

• Specifications are resolution of 12 bits and maximum sampling frequency of 100MHz.

- Low power consumption is essential, to allow integration of many channels.

- General models for the design of pipelined ADCs are studied.

- Good design of the main amplifier is the bottleneck of this ADC. The amplifier has been designed in schematic, using the small-signal models reported in **appendix A**, and simulation results are shown.

The work on ADCs was carried out at the Physikalisches Institut in Heidelberg and was preparatory for the work on the Super-Altro, which was carried out at CERN in Geneva.

The design of the Super-Altro 16 channels Demonstrator is reported in **chapter 4**. Main challenges and innovations in the Super-Altro include:

- System integration decreases the area.

- Having analog together with so much digital functionalities on the same silicon die, with acceptable performance degradation is a major challenge.

- Measuring the noise is one of the main goals, which should tell whether it is possible to continue in this path of system integration for future High-Energy Physics (HEP) experiments.

- With the bunch train schemes of future linear colliders, power pulsing features are now vitally important. This project must include such features, and provide estimations of attainable reductions of the power consumption.

The Pre-Amplifier and Shaping Amplifier (PASA) are based on the PCA16 prototype, developed as a follow-up to PhD Thesis [Tr], while the ADC is based on the prototype presented in [FS]. The DSP is similar to ALTRO, with some modifications explained in [GB]. The main points of the work carried out are:

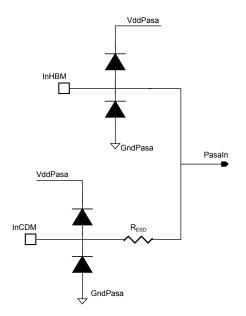

- The PCA16 was designed with different technology options, not suitable for Super-Altro. Therefore the design has been modified and fully re-simulated before integration in the Super-Altro; more robust ESD protections have been included.

- The biasing of the ADC was conceived for power pulsing (external biasing resistor). The ADC prototype was completed with the error correction logic.

#### 1.3. THE FUTURE: FAIR, ILC/CLIC

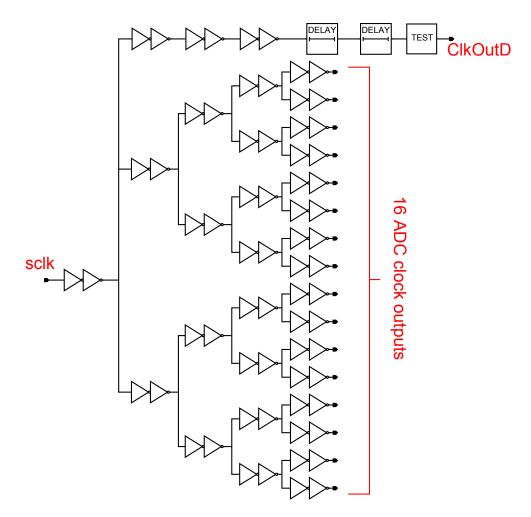

- A clock tree for the whole chip has been designed, and testability features have been added to the chip. The much simplified idea behind the clock tree is depicted in **appendix C**.

- The full system has been assembled, with careful choice of the chip floorplan.

- Special attention was paid to techniques to reduce noise coupling and crosstalk in the system.

- A Verilog-AMS model of the full chain has been written, allowing simulations to validate the integration of all blocks. This type of simulations may assume primary importance in the future, due to the complexity of advanced analog and digital functionalities in SoC. It is also useful for performance evaluations of complex systems, including detectors and any external component. The models are included in **appendix B**.

After submission of the Super-Altro, a test plan has been prepared. A test board has been designed, capable of handling all the possible operations of the chip. The details of the test board are reported in **chapter 5**, together with the results of the tests which have been carried out on the chip.

**Chapter 6** draws the conclusions of this thesis, and gives a glimpse into the future of SoC for HEP applications.

## Chapter 2

## Technological overview

This chapter summarizes the knowledge about semiconductor devices needed in order to understand the topics discussed in this thesis. This theory can be found in several textbooks; in general the discussion in this chapter follows references [Ba] and [MK].

## 2.1 The MOS transistor

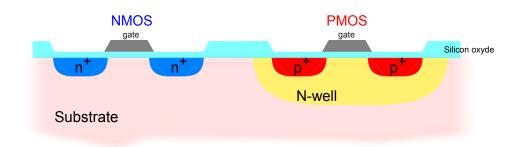

Semiconductor foundries implement complicated processes, based on lithography, to manufacture chips. In the technology available for this thesis, the minimum component size which can be drawn is 130nm. The semiconductive material (silicon) becomes n-doped with the addition of donor atoms, or p-doped with the addition of acceptor atoms. In most chip manufacturing technologies, the substrate is a p-type material; for technological reasons, it follows that the structure of n-channel transistors is simpler than in the p-channel case. Therefore, the discussion refers to the NMOS transistor; nevertheless, these considerations and equations are valid in an analogous way also for the PMOS transistor, leading to symmetrical results.

The Metal-Oxide-Semiconductor system (MOS) is the basic structure to build up the transistors in our technology. A silicon oxide layer is grown on the substrate and some conductive material is deposited on the oxide; in the past, this material was aluminum, which has been later replaced by polisilicon. The thickness of the oxide is of the order of a few tens of Angstrom. This basic system can be seen as a capacitor, whose plates are the metal and the substrate; the oxide is considered in most cases as an ideal insulator, although some small leakage may exist, as explained in paragraph 2.3.2.

A voltage applied to the metal induces some variations in the substrate, namely a positive voltage attracts electrons on the surface; when the voltage applied to the metal is high enough (higher than the substrate voltage plus the threshold voltage, discussed later), a channel is formed by the electrons in the substrate in the surface region close to the interface between substrate and oxide. This condition is called inversion, because the holes which populate the p-type substrate are replaced by electrons.

In the case of PMOS devices, an N-well is created in the p-type substrate; therefore, if the voltage applied to the metal is low enough, a holes inversion layer is formed on the surface, and the system can be described as in the NMOS case.

The region of the substrate which lies under the metal is called channel and at its both sides a heavily-doped n+ diffusion is present. This diffusion allows the creation of contacts with the metal layer that can be deposited on its top. At this point, the system with three metal terminals is a NMOS transistor and the metal above the channel is the gate; of the remaining two contacts, the one held at the lower voltage is called source and the other one drain. The system is depicted in figure 2.1.

Figure 2.1: Section of an NMOS on the left. The PMOS on the right is the complement of the NMOS, built inside an N-well.

Two design parameters, namely the voltage of the body and the voltage of the source of the transistor, affect the threshold voltage. With the available technology, PMOS transistors have an n-well which can be biased independently; usually this well is tied to the source, such that the source-body voltage difference is zero. On the other hand, NMOS transistors are built on the substrate, which means that their bodies are tied to the substrate, which is held at ground potential; in this case, the source-body voltage  $V_{SB}$  can be greater than 0V. Electrons in the inversion layer are attracted towards the source, which is at a higher potential than the body; therefore, they depopulate the channel, and a voltage higher than the nominal threshold voltage is needed at the gate in order to keep the channel inverted. This phenomenon is known as body effect.

#### 2.1. THE MOS TRANSISTOR

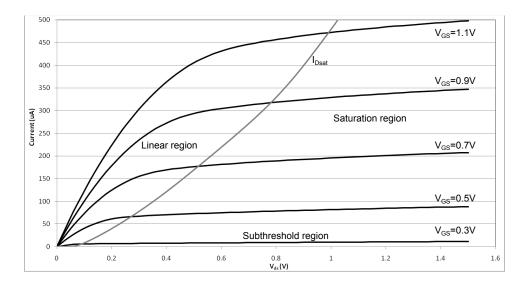

Characteristic curves of transistors in different operating regions are plotted in figure 2.2.

With the help of the threshold voltage, we can define three regions of operation for a MOS transistors according to its gate-to-source and drain-to-source voltages  $V_{GS}$  and  $V_{DS}$ .

Figure 2.2: Channel currents of an NMOS, as a function of the drain-source voltage  $V_{DS}$ , simulated for different values of  $V_{GS}$  [Ba, 6.3.2].

- **Linear region:**  $V_{GS}$  is greater than the threshold voltage  $V_{th}$ ; the channel is in inversion, therefore the system behaves like a resistor and the current is proportional to  $V_{DS}$ .

- **Saturation region:**  $V_{GS}$  is greater than the threshold voltage, and  $V_{DS}$  is greater than the overdrive voltage  $V_{OV} = V_{GS} V_{th}$ ; under this condition, the high voltage at the drain attracts many electrons from the inversion layer, and the channel is said to be pinched off. The current flowing along the channel is almost constant and independent of the drain voltage.

- Subthreshold region:  $V_{GS}$  is smaller than  $V_{th}$ , the channel is not inverted and nominally no current flow takes place. Still, the short-channel effect of subthreshold current may happen, as explained in 2.3.2.

In digital circuits, the allowed voltage levels are 0V and the supply voltage  $V_{DD}$ . Therefore, in the standard case of the digital inverter, each transistor is

either in the OFF state (gate voltage  $V_G = 0$ ) or in the ON state ( $V_G = V_{DD}$ ,  $V_{DS} = 0$ ).

In analog circuits, transistors are usually biased in the saturation region, which provides high gain (in figure 2.2, the curves in this region are closest to horizontal). In the case of transistors used as switches, the gate voltage  $V_G$  is either 0V (open switch) or  $V_{DD}$  with  $V_{DS}$  close to 0V (closed switch).

Before proceeding with the equations which describe the behaviour of MOS transistors in the different operating conditions, some parameters have to be defined.

When an electric field is applied across the channel of the transistor, the carriers reach a certain velocity. The ratio between velocity and electric field is defined as mobility [Ba, 5]:

$$\mu_{n,p} = \frac{Average \ velocity \ (cm/s)}{Electric \ field \ (V/cm)} \tag{2.1}$$

The mobility of electrons  $\mu_n$  is about three times larger than the mobility of holes  $\mu_p$ .

Indicating the oxide capacitance per unit area as  $C'_{ox}$ , the transconductance parameter  $KP_{n,p}$  can be defined as [Ba, 6.3.1]:

$$KP_{n,p} = \mu_{n,p} \cdot C'_{ox} \tag{2.2}$$

The  $\beta$  parameter, which includes not only technological constants, but also design parameters, is defined by:

$$\beta = KP \cdot \frac{W}{L}$$

where W and L are the width and length of the MOS transistor.

With these definitions, the characteristic equations of MOS transistors can be written [Ba, 6]. The NMOS case is considered here; for PMOS transistors, the equations are complementary ( $V_{GS}$  and  $V_{DS}$  have opposite sign).

In the linear region, the current flowing through the inverted channel of the transistor is [Ba, 6.3.1]:

$$I_D = KP \cdot \frac{W}{L} \cdot \left[ \left( V_{GS} - V_{th} \right) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.3)

In the saturation region, the current through the transistor is given by [Ba, 6.3.2]:

$$I_D = \frac{KP}{2} \cdot \frac{W}{L} \cdot \left(V_{GS} - V_{th}\right)^2 \tag{2.4}$$

#### 2.1. THE MOS TRANSISTOR

An improvement can be applied to this equation by taking into account an effect called channel length modulation. Equation 2.4 can be rewritten in the form:

$$I_D = \frac{KP}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_{th})^2 \left[1 + \lambda \left(V_{DS} - V_{DSsat}\right)\right]$$

(2.5)

where  $V_{DSsat}$  is the  $V_{DS}$  at the border between linear and saturation region for a given  $V_{GS}$ , and is equal to the overdrive voltage  $V_{OV}$ . The current when  $V_{DS} = V_{DSsat}$  is symbolized as  $I_{Dsat}$ . The channel length modulation parameter  $\lambda$  originates from the fact that part of the geometrical length of the channel is occupied by the width of the depletion layer (this effect is called channel length modulation).

From these equations, called square-law equations, the channel resistance and the transconductance of the transistor in the saturation region can be derived. By definition, the transconductance  $g_m$  is the derivative of the current with respect to the gate-to-source voltage; from equation 2.4, it follows that [Ba, 9.1.2]:

$$g_m = \frac{\partial I_D}{\partial V_{GS}} = KP \cdot \frac{W}{L} \cdot (V_{GS} - V_{th}) = \frac{2I_D}{V_{OV}}$$

(2.6)

If we derive the same equation with respect to the drain-to-source voltage  $V_{DS}$ , we obtain the resistance of the channel  $r_0$ :

$$r_0 = \frac{\partial V_{DS}}{\partial I_D} = \frac{1}{\lambda I_{Dsat}} \tag{2.7}$$

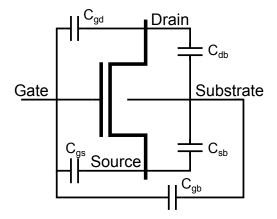

The symbol of an NMOS transistor is depicted in figure 2.3, together with the associated junction capacitances.

Reference [Ba, 6.1] reports the equations to calculate these capacitances in the saturation region:

- The drain-to-bulk  $C_{db}$  and source-to-bulk  $C_{sb}$  capacitances are constants (they depend on the technology).

- The gate-to-bulk  $C_{gb}$  capacitance is proportional to the channel length L.

- The gate-to-drain  $C_{gd}$  capacitance is proportional to the channel width W.

- The gate-to-source  $C_{gs}$  capacitance is proportional to the channel area WL.

Figure 2.3: The parasitic capacitances in an NMOS [Ba, 6.1].

Therefore, designers have control over the parasitic capacitances through the design parameters W and L.

In a comparison between an NMOS and a PMOS transistor with the same drain current and overdrive (giving the same transconductance), the NMOS transistor is smaller, because of the larger mobility  $\mu_n$  (equations 2.2-2.5); as a consequence, the parasitic capacitances  $C_{gd}$  and  $C_{gs}$  of the NMOS are roughly three times smaller than in the PMOS case.

Other necessary components available in semiconductor technologies are resistors and capacitors. Resistors can be built in several different ways, for example as strip of polichristalline silicon on the oxide, or as narrow metal paths. The designer chooses the width and length of these structures according to the desired resistance.

Capacitors are created, for example, as two horizontal metal plates separated by an insulating dielectric (MIM=Metal-Insulator-Metal structures) and the capacitance depends on the area of the plates. In MIM capacitors, the bottom plate forms also a parasitic capacitor with the substrate, and therefore sees a slightly bigger capacitance than the top plate.

Every technology provides also a stack of electrically isolated metal layers, that designers use to interconnect the devices.

### 2.2 Noise

Resistors and MOS transistors are affected by noise; equations exist for the spectral density of white thermal noise and flicker 1/f noise. In the next equations, f is the frequency, k is the Boltzmann's constant and T is the

#### 2.3. SHORT-CHANNEL

absolute temperature.

In MOS transistors, noise can be represented as concentrated on a single voltage source, placed at the gate of the transistor. When the transistor is in the saturation region, the power spectral density of this source has a thermal white component and a flicker one given, respectively, by [JM, 4.3]:

$$v_{ts}^2(f) = \frac{8kT}{3g_m}$$

(V<sup>2</sup>/Hz) (2.8)

$$v_{fs}^2(f) = \frac{K_F}{C'_{ox}WL \cdot f} \qquad (V^2/Hz)$$

(2.9)

where  $K_F$  is a constant depending on the technology and on the device, while  $C'_{ox}$  is the gate capacitance per unit area.

Thermal noise in a resistor is represented by a voltage source in series with it or equivalently, by a current source in parallel; their power spectral densities are, respectively [JM, 4.3]:

$$v_n^2(f) = 4kTR$$

(V<sup>2</sup>/Hz) (2.10)

$$i_n^2(f) = \frac{4kT}{R}$$

(A<sup>2</sup>/Hz) (2.11)

where R is the value of the resistance.

### 2.3 Short-channel

In modern technologies, transistors can be fabricated smaller and smaller. As a consequence, some effects, named short-channel effects arise; these are described in the literature, for example in [MK, 9, 10] and [Ba, 6, 9].

### 2.3.1 Effects and model

Source-drain charge sharing, drain-induced barrier lowering and punchthrough are short-channel effects that decrease the threshold voltage of the transistor; here they are briefly addressed, based on [MK, 9.2] and [Ba, 6.5.2].

Source-drain charge sharing refers to the fact that the width of the depletion region surrounding the drain and source is not negligible any more, in comparison with the short length of the channel.

Drain-Induced Barrier Lowering (DIBL) is a decrease of the threshold voltage, due to the electrons which are attracted in the channel by the positive voltage of the drain. As a consequence, the output (channel) resistance of short-channel transistors decreases, and this leads to the unwanted effect of a lower gain of the amplifiers.

Punchthrough is a short between the drain and source depletion regions, which can happen in the bulk of the transistor (far from the oxide-silicon interface).

Mobility degradation originates from the fact that, as the transistor sizes are reduced, also the oxide thickness is reduced. Therefore, the electrical field across the oxide, between gate and channel, increases; this results in a decrease of the mobility of electrons in the channel.

When the electric field across the channel, between source and drain, is large, the velocity of carriers does not increase any more as expected from equation 2.1, and a saturation velocity  $v_{sat}$  is reached.

Equation 2.4 is rewritten for short-channel transistors [MK, 9.2]:

$$I_{Dsat} = WC'_{ox} \cdot (V_{GS} - V_{th} - V_{DSsat}) \cdot v_{sat}$$

$$(2.12)$$

where  $V_{DSsat}$  is not equal any more to the overdrive voltage, as it was in the long-channel case. Equation 2.6 becomes [Ba, 9.2.1]:

$$g_m = v_{sat} \cdot C'_{ox} \cdot W \tag{2.13}$$

### 2.3.2 Leakage currents

Leakage currents are present in every transistor, but they become more relevant as the dimensions decrease. A brief overview follows, based on [MK, 10.2, 10.3] and [Ba, 6.5.2].

Electrons with a sufficiently high kinetic energy (hot electrons) can hit the atoms and ionize them (impact ionization); this results in new free electronhole pairs. The resulting electron feels the positive voltage of the drain. The resulting hole, instead, travels in the substrate and, by doing this, contributes to the leakage current  $I_{sub}$ .

The gate is not actually a perfect insulator, and some current can flow through it. The gate leakage current is generated by channel hot electrons (they gain an energy higher than the potential barrier between silicon and gate), drain-avalanche hot carriers (carriers generated by impact ionization events) and cold electrons (which pass through the oxide by means of the tunnel effect).

If the field across the oxide becomes too large, the oxide breaks down; therefore, the voltage difference between gate and channel must be kept below very few Volts in modern technologies.

When the gate-to-source voltage of a transistor is less than its threshold voltage, the device is in subthreshold region [Ba, 6.4.2]. Still, some current

### 2.3. SHORT-CHANNEL

flows through it, with an exponential dependency on  $V_{GS} - V_{th}$ . In shortchannel technologies the threshold voltage is, generally speaking, lower, and therefore the unwanted subthreshold current is higher.

## Chapter 3

## Analog-to-digital converter

## 3.1 Specifications

In any analog-to-digital converter, a sample of an analog signal is converted in a digital code; the numerical value of the digital code is proportional to the amplitude of the analog sample. The input signal will be differential in order to reject common-mode noise; each half-signal will vary between a maximum  $V_{ref+}$  and a minimum  $V_{ref-}$ . Therefore, the differential signal will assume positive or negative values, between a maximum  $+V_{ref}$  and a minimum  $-V_{ref}$ , defined as  $V_{ref} = V_{ref+} - V_{ref-}$ ; the differential voltage span  $V_{pp}$  (peak-to-peak voltage) is equal to  $2V_{ref}$ .

The number of bits N, which makes up the digital word, determines the resolution of the converter.

The minimum signal which can be discerned is called Least Significant Bit (LSB), and is expressed by:

$$LSB = \frac{V_{pp}}{2^N} \tag{3.1}$$

In the next paragraphs, this simplified model will be expanded, including several parameters which are helpful in expressing the performance of ADCs. The literature offers several sources of information about ADC parameters; in general here the discussion follows references [JM, 11] and [Ba, 28].

### 3.1.1 Quantization error

ADCs convert an analog signal, which is by definition continuous, in a digital representation, which is discrete. The higher the number of bits, the more precise this conversion is. Anyhow, an infinite number of bits is not realistic, and therefore there will always be a loss of resolution when a digitization takes place. The difference between an analog signal and its digital approximation can be calculated statistically, and its root mean square is the quantization error (quantization noise).

It has been shown [Ba, 28.5] that the dependency of the quantization error  $Q_{error}$  on the *LSB*, and therefore (equation 3.1) on the number of bits is:

$$Q_{error} = \frac{LSB}{\sqrt{12}} = \frac{V_{pp}}{2^N} \cdot \frac{1}{\sqrt{12}}$$

(3.2)

### 3.1.2 Transfer curve of an ADC and non-linearity

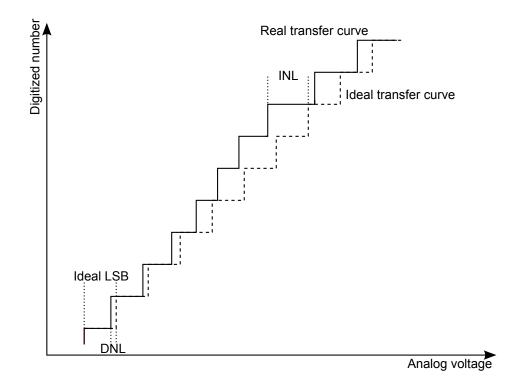

ADC transfer curves can be plotted. They typically look like figure 3.1.

Figure 3.1: Example of transfer function of an ADC, with graphical explanation of DNL and INL.

The figure shows an ideal transfer curve (dotted), where all steps are equal. The continuous line represents the transfer curve for a real ADC, affected by non-linearities.

An horizontal step represents the range of analog voltage which is discretized in the same digital code. Ideally, this analog range would be given by the LSB; the difference between the ideal value and the real one, expressed in LSBs, is called Differential Non-Linearity (DNL). The DNL for a converter can be plotted as a function of the analog input, or also given as a number; in this last case, only the maximum value of the DNL is given, as a worst-case.

One important property of ADCs is the monotonicity of their transfer curve. In order to ensure it, designers typically try to keep the DNL smaller than 1LSB, because if this condition is satisfied, then the ADC is monotonic [JM, 11.5].

Figure 3.1 also shows that, due to the accumulation of the DNL of many digital steps, the real transfer curve may, at, some point, be significantly far from the ideal one. The maximum displacement between each real vertical steps and its corresponding ideal vertical step is defined as Integral Non-Linearity (INL).

The discussion so far voluntarily neglected the fact that the transfer curve may not start from the origin and may have a slope different from the ideal  $2^N/V_{pp}$ . The first effect is an offset, while the second one is called gain error. They are subtracted from the transfer curve before calculating DNL and INL.

### 3.1.3 Signal-to-noise ratio

The concept of quantization error (or noise) has been introduced. Even in the case of an ideal ADC, without additional noise sources, this noise is present and limits the maximum Signal-to-Noise Ratio that the converter can achieve.

The maximum analog input signal is  $V_{pp}$ ; a sinusoidal signal with this amplitude carries a power of  $V_{pp}^2/8$ . Therefore, with the presence of the quantization noise, using equation 3.2, the maximum Signal-to-Noise Ratio (SNR) achievable is given by:

$$SNR_{max} = \frac{V_{pp}^2}{8} \cdot \left(\frac{\sqrt{12} \cdot 2^N}{V_{pp}}\right)^2 = 1.5 \cdot 2^{2N}$$

Usually, the SNR is expressed in dB, and the espression for the ideal SNR becomes [Ba, 28.5]:

$$SNR_{max} = 6.02 \cdot N + 1.76 \ (dB)$$

(3.3)

In real ADCs, also other random noise sources are present; they add quadratically to the quantization error. Therefore, they degrade the SNR, which becomes lower than  $SNR_{max}$ . Equation 3.3 can be used also to express

the resolution in terms of a measured SNR; this is the Effective Number Of Bits (ENOB):

$$ENOB = \frac{SNR - 1.76}{6.02} \tag{3.4}$$

Sometimes, also the SIgnal-to-Noise and Distortion ratio (SINAD) is used instead of the SNR, to include the effect of the harmonic distortion of the ADC, and give a more accurate value of the ENOB.

## **3.2** ADC architectures

A number of architectures have been developed for ADCs to meet a broad range of application requirements. In this section an overview will be given, following [JM, 13, 14] and [Ba, 29.2], focusing on the architectures which suit best our needs. The last paragraph motivates the choice of the pipeline architecture for the ADC object of this thesis.

Among the most popular ADC architectures, the focus is on flash, pipeline, delta-sigma. Additionally, successive approximation ADCs, which will be mentioned in section 6.2, are briefly introduced.

### 3.2.1 Successive Approximation Register

In Successive Approximation Register (SAR) converters [JM, 13.2], a threshold is set at the middle of the maximum voltage range, and the input signal is compared to this threshold; after this first comparison, the voltage range which contains the input signal is divided into two more equal sub-ranges by a second threshold. The input signal is then compared to this second threshold to determine in which sub-range it lies. After that, a third sub-range is determined by a third threshold, a new comparison has place and so on for a number of cycles N equal to the number of bits of resolution required.

### 3.2.2 Flash

As explained in [JM, 13.4], the flash architecture generates at the same time all the  $2^N - 1$  fixed thresholds corresponding to the number of digital steps. These thresholds are created by a resistive divider from a given reference voltage. Per each threshold, a comparator determines whether the signal is larger or smaller than the threshold.

It is clear that, as the number of bits N increases, the number of comparators increases exponentially. Apart from the complexity, this is bad also because many comparators add up to a large capacitance seen by the input signal. As a consequence, for high resolution, flash converters become slow or require more power.

Most of all, the accuracy of each comparator and of the voltage divider must be good (offset lower than 0.5LSB) in order to avoid errors in the output code. Some digital correction techniques are available to relax the requirement on the comparator offset and on the resistor mismatch, to 4LSB.

# 3.2.3 Pipeline

Pipeline is an evolution of two-step ADCs. Two-step ADCs, described in [JM, 13.5] and [Ba, 29.2.2], are used to compensate the drawbacks of flash ADCs: they have less capacitive load and they need fewer comparators with relaxed resolution and offset requirements.

The main idea of two-step ADCs is to split a big flash converter into two smaller blocks, each one being itself a flash ADC. The first block resolves the most significant  $N_1$  bits and passes the residue (difference between the analog signal and the voltage equivalent to the  $N_1$ -bit code digitized so far) through a DAC to an amplifier with a gain of  $2^{N_1}$  and then to the second block, which resolves the remaining  $N_2 = N - N_1$  least significant bits.

This principle can be extended to more than two blocks, each one resolving a lower number of bits, the so-called pipeline architecture [JM, 13.8] [Ba, 29.2.3]. In the extreme case, N stages can be implemented, with 1-bit of resolution each.

Pipeline requires a much lower number of comparators than flash ADCs, especially for higher resolutions. Moreover, the offset requirements of comparators is much more relaxed. On the other side, the implementation of the gain stages to generate the residue is a challenge. Pipeline also has a long latency, because N clock cycles after the signal sampling are needed before the digital output is ready.

# 3.2.4 Delta-Sigma (Oversampling)

Delta-Sigma converters, explained in [JM, 14] and [Ba, 29.2.6], are different from the other converter architectures covered so far. In fact, SAR, flash and pipeline ADCs belong to the category of Nyquist rate converters because, according to the Nyquist sampling theorem, their sampling frequency  $S_R$ must be higher than the Nyquist frequency, defined as twice the maximum frequency component of the signal that they have to digitize.

In Delta-Sigma converters, the signal is converted at low resolution and at a much higher frequency than its bandwidth. The ratio between conversion frequency and Nyquist frequency, called OverSampling Ratio (OSR), can be in the order of hundreds (typically powers of 2 are implemented for convenience).

The advantage of oversampling is that the power spectrum of the quantization noise is spread over a frequency range up to the conversion frequency, while the power spectrum of the input signal is limited to its bandwidth. Therefore, a digital low-pass filter can keep the signal power at low frequencies, and filter out much of the quantization noise at high frequencies.

Often the core of a Delta-Sigma converter is a 1-bit ADC (one single comparator). The comparator converts the same sampled signal many times (at the high conversion frequency) and produces a series of bits. A digital decimation filter reduces the number of 1-bit samples and yields a higher resolution digital output, updated at the (low) sampling frequency.

The main drawback is the low speed: typically, the sampling frequency is of the same order as the maximum signal frequency, while the clock (conversion) frequency is a few hundred times (OSR) the sampling frequency. This means that, even with a clock frequency in the GHz region, the sampling frequency will be in the MHz region.

## 3.2.5 Architecture choice

The requirements for the ADC object of this thesis are up to 100MHz clock frequency and resolution up to 12 bits.

Delta-Sigma ADCs are used when high resolution, for example 16 bits, is required. The price to pay for this resolution is their low speed.

Flash architecture requires  $2^N - 1$  comparators: 4095 for a 12-bit converter. In the present case, their offset should be as low as  $200\mu V$  (without digital correction), which is a very harsh requirement. Flash converters are fast and have no latency, but they are typically found with a resolution of 8 bits.

Pipeline ADCs require only 2N comparators in the case of 1.5 bits of resolution per pipeline stage. The offset of the comparator is not critical because some digital correction techniques can compensate any error as long as the offset is lower than 200mV in the present application (section 3.3). The main disadvantage is that the signal has to travel through all the stages. This travel, controlled by the clock, introduces a latency between the sampling instant of the analog signal and the instant when the corresponding digital code is available at the output. Anyhow, for applications in High-Energy Physics (HEP), latency is usually not an issue, because the digitized data will be further processed, thus delayed.

In the trade-off between speed and resolution, pipeline ADCs are the solution which suits best the needs of the present application, as shown in [AB] and [FS].

In the next sections, a deeper description of the pipelined architecture will be given in order to understand better its theory of operation and its implementation.

# 3.3 The pipeline architecture

Pipeline ADCs are widely described in the literature, for example in [Su].

The operating principle of a 1bit/stage pipeline ADC is shown in figure 3.2. The input signal to be digitized is compared with a fixed threshold.

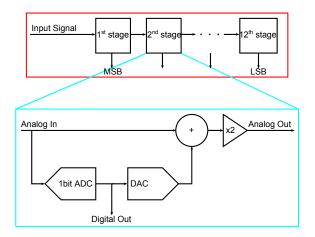

Figure 3.2: Diagram of a pipelined ADC with a resolution of 1bit per stage.

According to the result of the comparison, the residue is calculated as the voltage difference between the signal and the threshold. The residue is then multiplied by two and passed over to the next stage. The algorithm adds one bit of resolution at each stage, in order to figure out which of the  $2^N$  bins contains the signal. From the diagram, one can see the reason why each stage is named Multiplying Digital-to-Analog Converter (MDAC).

With this straightforward implementation, the offset of the comparators must be very small (less than half LSB, or  $390\mu$ V), otherwise an error in the comparison in the first stages leads to a wrong digital output. This is practically not implementable.

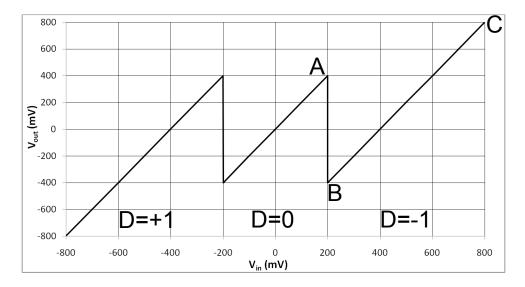

A more robust implementation exists, which uses some redundancy in order to correct for offsets or possible errors of the comparators. In this architecture, each MDAC has 1.5bit of resolution. In each pipeline stage, two comparators compare the input voltage with two thresholds  $\pm V_{ref}/4$ . The ideal transfer function of this MDAC, plotted in figure 3.3, is:

$$V_{out} = 2 \cdot V_{in} + D \cdot V_{ref} \tag{3.5}$$

where D corresponds to the decision of the comparators, and can assume values 0, 1, -1.

Figure 3.3: Plot of the ideal transfer function of a 1.5bit MDAC. When  $V_{in} < -200mV$ , D = +1; when  $-200mV < V_{in} < +200mV$ , D = 0; when  $V_{in} > 200mV$ , D = -1.

In this implementation, the important requirement is that a signal in the upper range ( $\geq +V_{ref}/4$ ) must not be classified in the lower range ( $\leq -V_{ref}/4$ ) and vice versa. Any other error can be corrected, as will be detailed in section 4.4, where the digital error correction is explained. Therefore, the requirement for the comparator offset is relaxed to  $< V_{ref}/4$  (200mV).

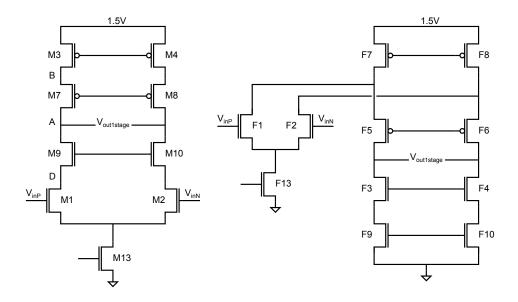

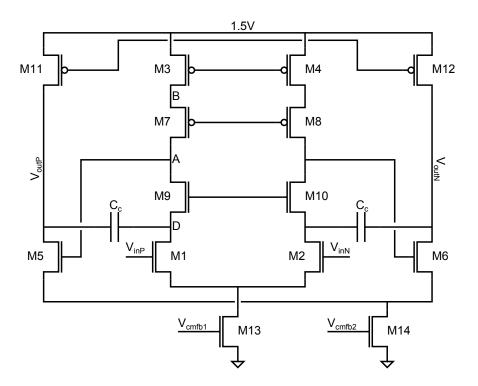

Figure 3.4 is a diagram of the pipeline ADC, including the digital error correction. It shows also that the first stage acts as a Sample-and-Hold (S/H), as well. The spectrum of the input signal is known, and lays in the baseband of the ADC; therefore, the skew between the comparison instant and the sampling instant is not crucial, and there is no need of a dedicated, noisy and power-hungry S/H.

The commonly-used figure of merit fom for this type of ADC is the energy required for the effective conversion of an analog signal in one bit:

$$fom = \frac{energy}{conversion} = \frac{power}{2^{ENOB} \times S_R}$$

(3.6)

where  $S_R$  is the sampling rate of the ADC.

28

Figure 3.4: Diagram of a 1.5bit/stage pipeline ADC, including stage scaling and digital error correction, which will be explained in section 4.4 [AB].

## 3.3.1 Multiplying Digital-to-Analog Converter

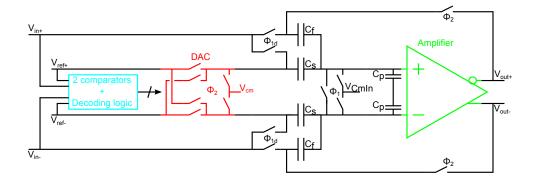

Figure 3.5 shows how a 1.5bit MDAC is implemented. The implementation must be differential for noise reasons. Two comparators decide in which range the input voltage lays, by comparing it with the two thresholds  $\pm V_{ref}/4$ ; two reference voltages,  $V_{ref+}$  and  $V_{ref-}$ , define  $V_{ref} = V_{ref+} - V_{ref-}$ .

The digital outputs of the comparators are latched and then passed to the decoding logic, which controls the switches in order to provide the correct voltage output to be subtracted to the input signal by the amplifier.

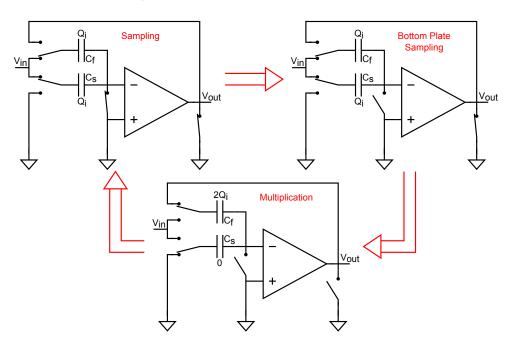

The amplifier uses Switched Capacitors (SC) to implement the multiplication by a factor of 2. The input signal is first sampled on capacitors  $C_s$  and  $C_f$ ; bottom-plate sampling must be used to reduce the charge injection dependency on the input signal [Ba, 25.2.1]. In the next phase,  $C_f$  is flipped and becomes the feedback capacitor of the amplifier. The clock  $\phi_{1d}$  is a delayed copy of  $\phi_1$ ; clocks  $\phi_1/\phi_{1d}$  and  $\phi_2$  are non-overlapping.

Figure 3.5: Scheme of one pipeline stage, with reference voltages  $V_{ref+}$  and  $V_{ref-}$  and  $V_{cm}$ , and clocks  $\phi_1$ ,  $\phi_{1d}$  and  $\phi_2$  [AB].

Figure 3.5 suggests that equation 3.5 represents an ideal transfer function; a more realistic transfer function is given by 3.7 (derived from [AB]):

$$v_o(t) = \frac{\beta A_o}{1 + \beta A_o} \cdot \left(1 - e^{-\frac{t}{\tau}}\right) \cdot \left[\left(1 + \frac{C_s}{C_f}\right) \cdot V_{in} + D \cdot \frac{C_s}{C_f} \cdot V_{ref}\right]$$

(3.7)

The first term gives the effect of the finite open-loop gain, which depends on the feedback factor  $\beta$  and on the open-loop DC gain of the amplifier  $A_o$ . The exponential term corresponds to the finite bandwidth of the amplifier, with time constant  $\tau$ . The term with capacitances  $C_s$  and  $C_f$  quantifies the influence of the mismatch between capacitors.

In the next pages, these aspects will be analysed and applied to the design of the main amplifier for the MDAC.

The issue of capacitor mismatch, which determines the size of  $C_s$  and  $C_f$ , will be addressed in 3.3.2.

An helpful technique used in pipeline ADCs is stage scaling, which is included in figure 3.4 and will be explained in 3.3.3.

Noise issues are dealt with in 3.3.4; in this design, they mainly affect the sizing of the compensation capacitors in the main amplifier.

Finally, gain and bandwidth requirements of the amplifier are calculated in 3.3.5.

Currently, a state-of-the-art 12bit pipeline ADC is described in [AB], which is taken as a reference in this chapter.

#### Comparator, decoder and switching block

Since the thresholds are  $\pm V_{ref}/4$ , the main requirement for each comparator is an offset lower than  $V_{ref}/4$ ; moreover, the power consumption should be kept as low as possible. The speed should be such that the delay introduced by comparators, logic and switches fits in the time budget; for a sampling frequency  $S_R = 100MHz$ , these delays should be shorter than 1ns [AB]. When it comes to the decision on the topology for comparators, the aim at a low power consumption makes dynamic comparators the most suitable solution to the power issue. Dynamic comparators do not dissipate DC power; when the comparison takes place, parasitic capacitances have to be loaded or discharged by some transient currents, which represent the only source of power consumption in dynamic comparators.

Some different topologies for dynamic comparators can be found in [Su, 4.1].

### 3.3.2 Sample and multiply capacitors

The operation of the SC amplifier is shown in its three phases in figure 3.6; the total sampling capacitance can be defined as  $C_h = C_f + C_s$ . The input voltage  $V_{in}$  charges  $C_h$ ; at the instant of the bottom-plate sampling, the charge  $Q_{in}$  corresponding to  $V_{in}$  is stored at the amplifier input node. When  $C_f$  is connected in feedback and D = 0,  $C_s$  is discharged, because both its terminals are at ground (virtual), and  $Q_{in}$  is completely transferred to  $C_f$ ; if  $C_f = C_s$ , this implements a multiplication by two.

If  $D \neq 0$ , it is straightforward to see that the MDAC performs a multiplication by one of  $D \cdot V_{ref}$ .

Figure 3.6: MDAC multiplies by 2 the input voltage and by 1 the reference voltage. Single-ended version shown [Ch, App 2].

From equation 3.7, including a mismatch  $\Delta C_{f,s}$  between  $C_f$  and  $C_s$ , the gain of the stage can be written as:

$$\left(2 + \frac{\Delta C_{f,s}}{C_{f,s}}\right) \cdot V_{in} + D \cdot \left(1 + \frac{\Delta C_{f,s}}{C_{f,s}}\right) \cdot V_{ref}$$

(3.8)

As explained in [Ma], the capacitor mismatch can be expressed by equation:

$$\frac{\Delta C}{C} = \frac{6 \cdot 10^{-4}}{\sqrt{C_h(pF)}} \tag{3.9}$$

where the capacitance is expressed in pF, and the mismatch is intended as  $3\sigma$  variation; the conventional mismatch coefficient (numerator in the equation) actually depends on the technology. Now, the mismatch requirement for 1/4 LSB of linearity error in an N-bit resolution, 1.5bit/stage pipeline ADC, is:

$$\frac{\Delta C_h}{C_h} < \frac{1}{2^N} \tag{3.10}$$

From the last two equations, it follows that [Ma]:

$$C_h(pF) \ge 3.6 \cdot 10^{-7} \cdot 2^{2N}$$

(3.11)

Therefore, for 12bit and 1/4 LSB error,  $C_h=6pF$ ; for 12bit and 1/2 LSB error,  $C_h=1.5pF$ . Since large capacitors need large currents (paragraph 3.4.2), the choice of the value of the capacitors is a trade-off between good matching and low power. The design choice is  $C_h=2.4pF$  ( $C_f=C_s=1.2pF$ ); this value also gives good sampling noise, as explained later in 3.3.4.

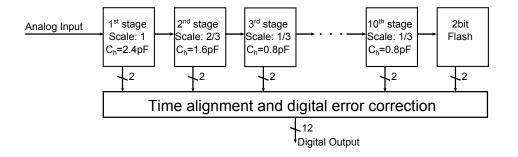

#### 3.3.3 Stage downscaling

In a system made up of several stages, the equivalent input noise of stage i is its noise  $N_t(i)$  divided by the gain of the previous stages; therefore the total input referred noise  $N_{tot}$  for this pipeline ADC with stage gain of 2 is:

$$N_{tot}^2 = N_t(1)^2 + \frac{N_t(2)^2}{2^2} + \frac{N_t(3)^2}{4^2} + \frac{N_t(4)^2}{8^2} \dots$$

(3.12)

A noise increase of a factor of two (RMS) from one stage to the next one leads to the same noise per stage. As a consequence, the requirements of the later stages can be relaxed. In the present ADC, this translates into a scaling of the stage capacitors along the pipeline, with the clear advantage of a significant decrease in the area and power consumption.

The literature offers some studies of the optimum scaling factor, as in [CG]: the two opposite cases are a scaling factor of 1 (equal stages or no scaling) and a scaling factor of 4. If the factor is 1, only the first stage contributes noise, while the noise of the other stages is negligible; all stages have the same power consumption. If the factor is 4, all stages introduce an equal amount of noise, and the power consumption is concentrated on the first stage; the problem is that the power of the first stage must be significantly increased, in order to compensate for the noise contributions from the later stages. Therefore, an optimum exists, when the capacitors are scaled by the stage gain, in this case 2.

In many implementations, the chosen scaling factor is a bit smaller than 2,

and a good choice is 1.5 for the second stage and 3 (twice the second stage) for the following stages [AB], as shown in figure 3.4.

Table 3.2 will show that, with this scaling scheme, only the noise of the first stages is relevant.

### 3.3.4 Noise

The main noise sources considered in this thesis are quantization noise, sampling noise, and amplifier noise.

The quantization noise was already given by equation 3.2, reported here:

$$Q_{error} = \frac{LSB}{\sqrt{12}} = \frac{V_{pp}}{2^N} \cdot \frac{1}{\sqrt{12}} = \frac{2V_{ref}}{2^N \cdot \sqrt{12}}$$

(3.13)

Sampling noise and amplifier noise are calculated next.

#### Sampling noise

The sampling noise is the thermal noise of resistors (the switches used in the Switched Capacitor circuit), sampled by the capacitors; it is often named kT/C noise. The general equation for the sampling noise  $N_{sampling}$  on a capacitor  $C_{sampling}$  is:

$$N_{sampling}^2 = \frac{kT}{C_{sampling}}$$

where k is the Boltzmann's constant, and T is the temperature expressed in °K. In the specific case of this MDAC, the sampling noise  $V_{nsi}$  of a pipeline stage can be calculated as suggested in [Ch, pag 136-138].

Figure 3.6 shows that, during the sampling phase, the kT/C noise on the sampling capacitors (single-ended) is:

$$V_{nsi}^2 = \frac{kT}{C_s + C_f + C_p}$$

where  $C_p$  is the parasitic input capacitance of the amplifier. The corresponding charge  $Q_{nsi}$  accumulated across the capacitors is:

$$Q_{nsi}^2 = kT \cdot (C_s + C_f + C_p)$$

When  $C_f$  is flipped in the multiply phase, the output voltage  $V_{nso}$  due to  $Q_{nsi}$  is:

$$V_{nso}^{2} = \frac{Q_{nsi}^{2}}{C_{f}^{2}} = kT \cdot \frac{C_{s} + C_{f} + C_{p}}{C_{f}^{2}} = \frac{kT}{C_{f}} \cdot \frac{1}{\beta}$$

where the feedback factor  $\beta$  is defined in equation 3.20. The last equation, divided by the stage gain, gives the input referred sampling noise  $N_s$  of the MDAC (single-ended):

$$N_s^2 = \frac{V_{nso}^2}{G^2} = \frac{kT}{C_f} \cdot \frac{1}{\beta} \cdot \left(\frac{C_f}{C_s + C_f}\right)^2 = \frac{kT \cdot (C_s + C_f + C_p)}{(C_s + C_f)^2}$$

(3.14)

If the input capacitance of the amplifier is small enough, it is possible to approximate:

$$N_s^2 = \frac{kT \cdot (C_s + C_f + C_p)}{(C_s + C_f)^2} \approx \frac{kT}{C_s + C_f}$$

Since the noise of the two single-ended inputs adds in an uncorrelated way to the differential noise, the differential input-referred sampling noise  $N_{sd}$  is twice as big, and can be approximated by:

$$N_{sd}^{2} = 2 \cdot N_{s}^{2} = 2 \frac{kT}{C_{s} + C_{f}} \cdot \frac{C_{s} + C_{f} + C_{p}}{C_{s} + C_{f}} \approx 2 \frac{kT}{C_{s} + C_{f}} = \frac{kT}{C_{s}}$$

(3.15)

#### Amplifier noise

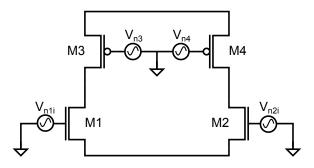

In section 3.4.1, it will be explained that the chosen architecture for the MDAC amplifier is a two stage with telescopic cascode input. The noise of the output stage is negligible, because it is divided by the high gain of the first stage, when referred to the input. In the telescopic stage, the cascode transistors do not change the currents in the two branches; therefore, also their noise contribution is negligible. As a consequence, the noise in this amplifier can be calculated as explained in [Ra, 7.5, 9.10], using the simplified model of a differential pair, shown in figure 3.7.

Figure 3.7: Model of the amplifier for noise calculations. Due to symmetry, the noise power of the input transistor M1 is equal to that of M2; also the load transistors M3 and M4 have the same noise power;  $V_{n1i}$ ,  $V_{n2i}$ ,  $V_{n3}$  and  $V_{n3}$  represent the noise sources. All other noise sources in the amplifier are negligible, as explained in the text.

#### 3.3. THE PIPELINE ARCHITECTURE

The amplifier will have a large GBW, which will make thermal noise the dominant noise source; flicker noise is therefore neglected in the following calculations.

The noise spectral density of the two input transistors is  $V_{n1i}(f) = V_{n2i}(f) = v_{ts}^2(f)$ , as in equation 2.8. Also the noise of one current source transistor  $M_3$  (or  $M_4$ ) is given by its  $v_{ts}^2(f)$ ; since the gain from the gate of  $M_3$  (or  $M_4$ ) to the output is  $g_{m3}(r_{o1}||r_{o3})$ , the output noise spectral density  $V_{n3o}(f)$  due to a current source transistor is:

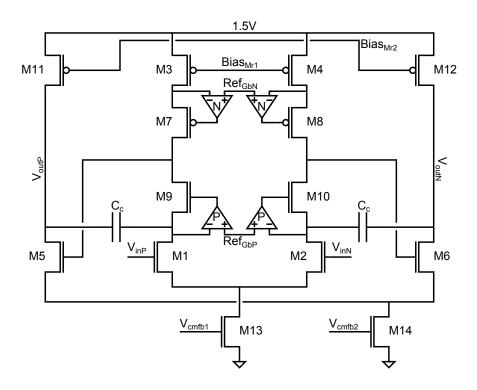

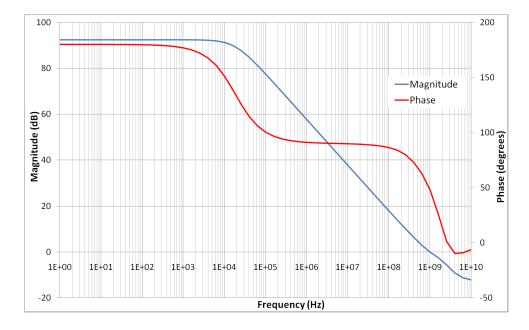

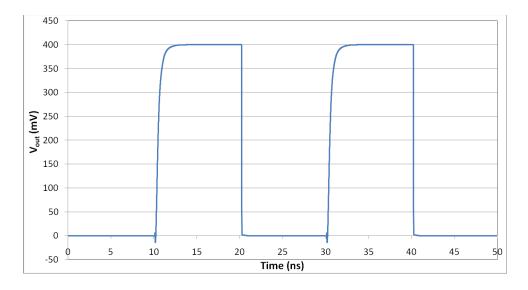

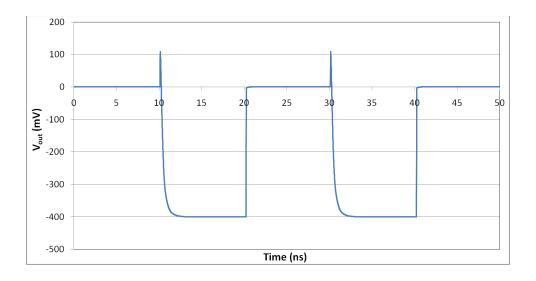

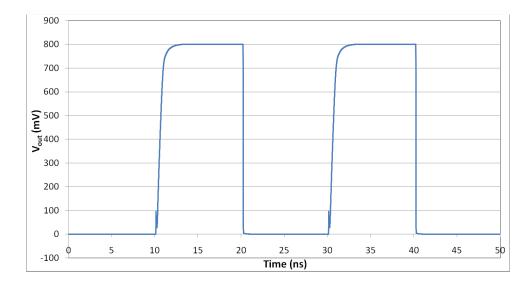

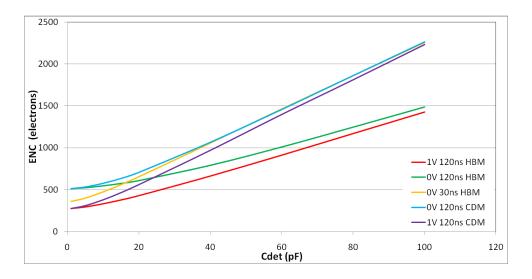

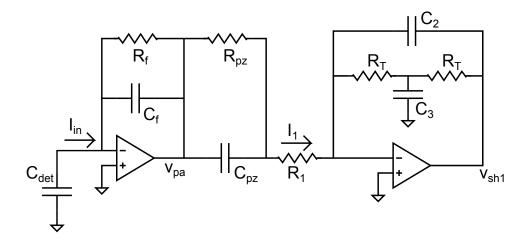

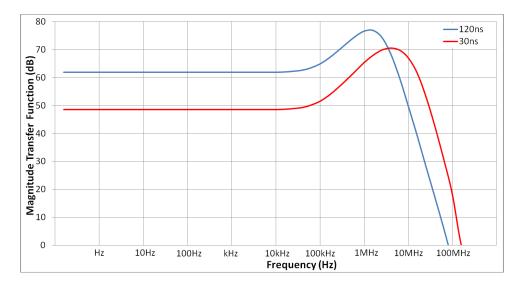

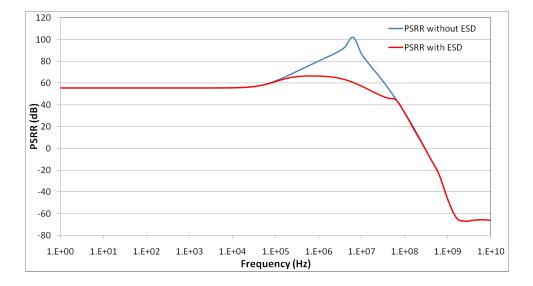

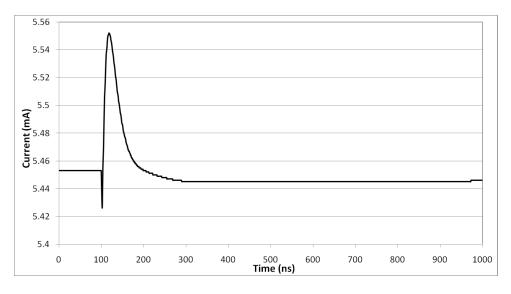

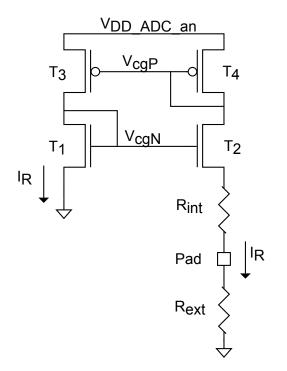

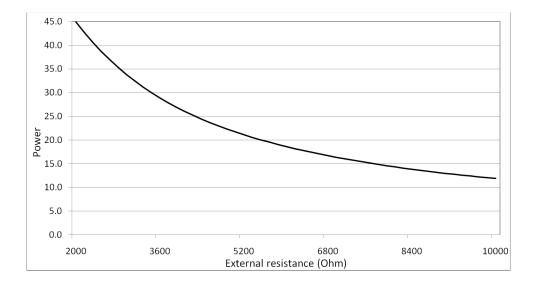

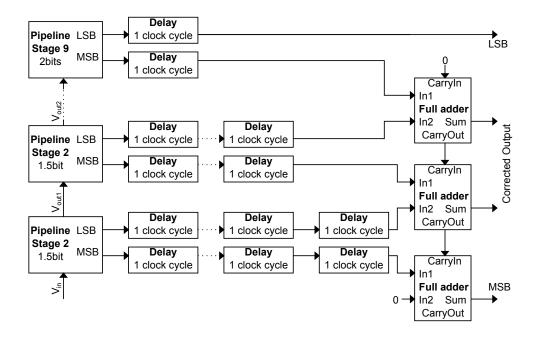

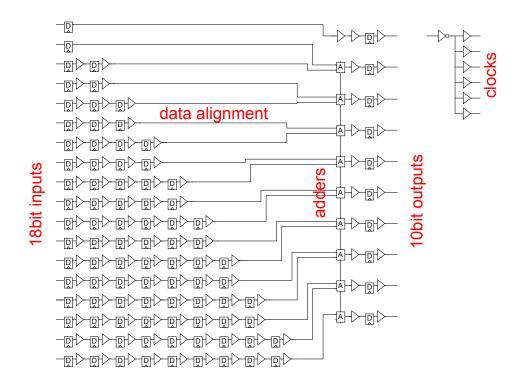

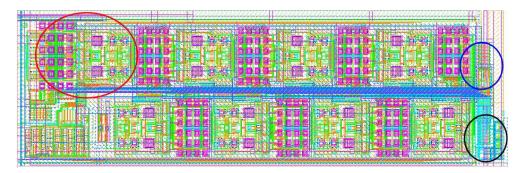

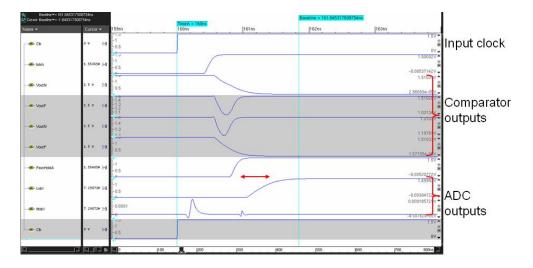

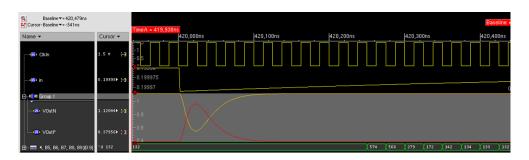

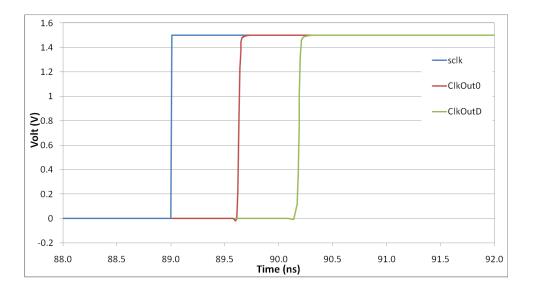

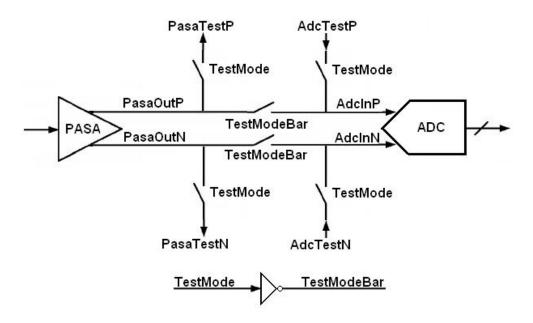

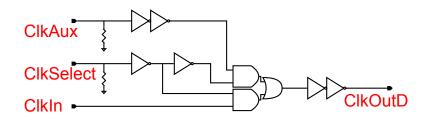

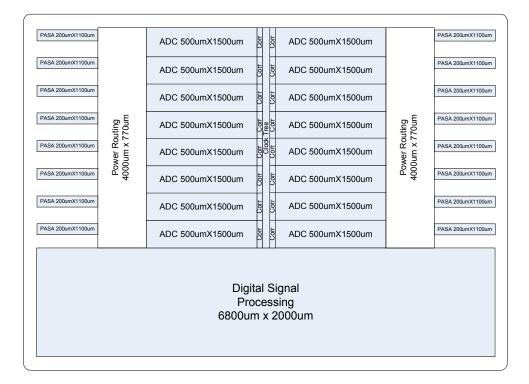

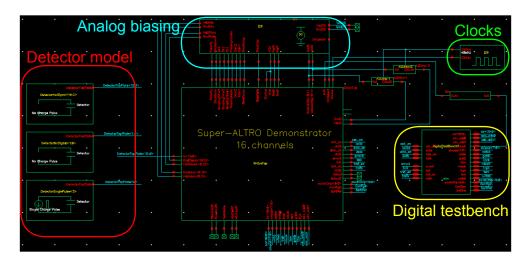

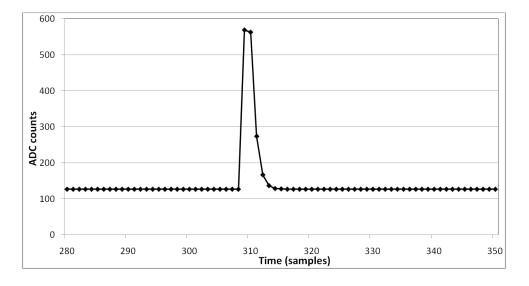

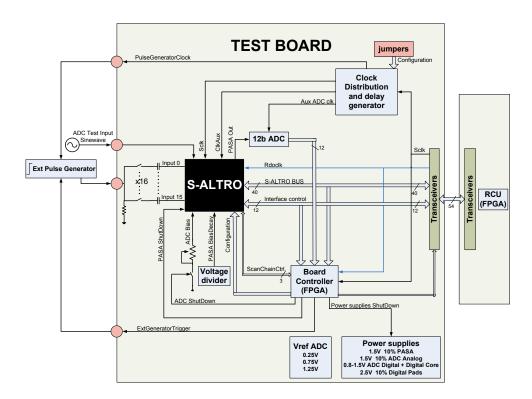

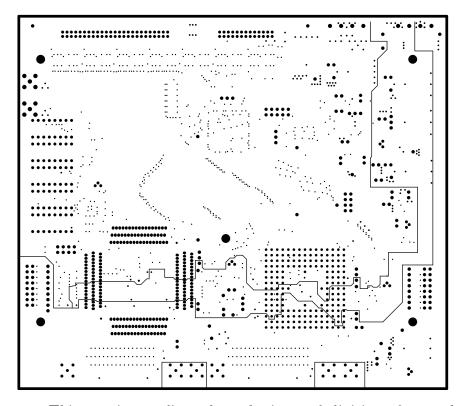

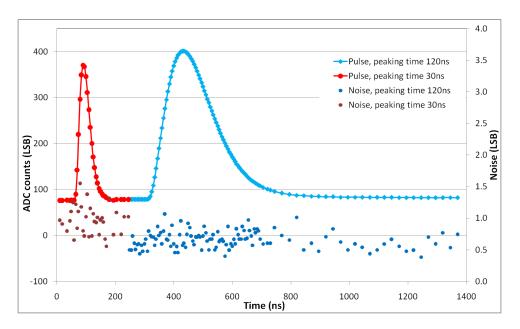

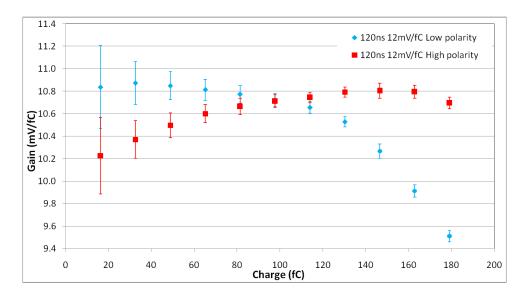

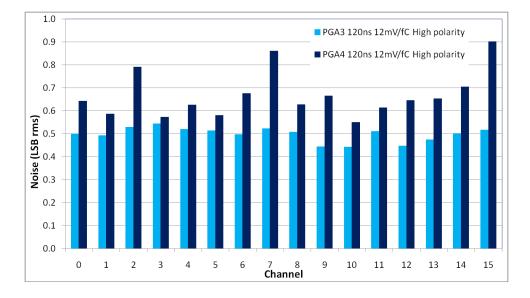

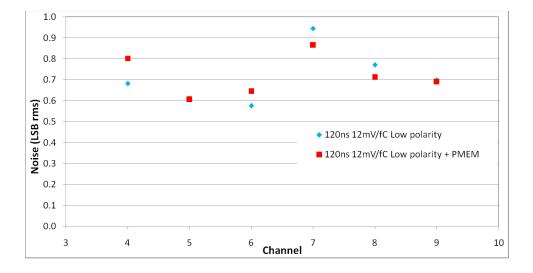

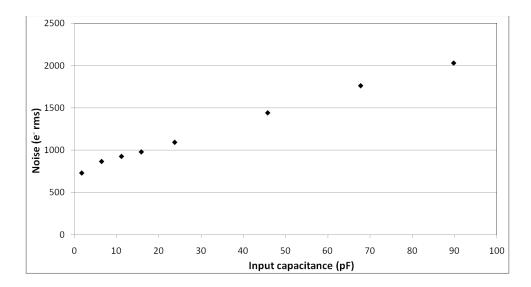

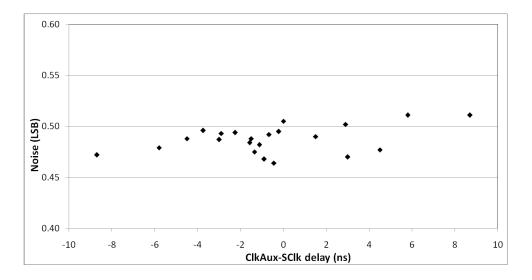

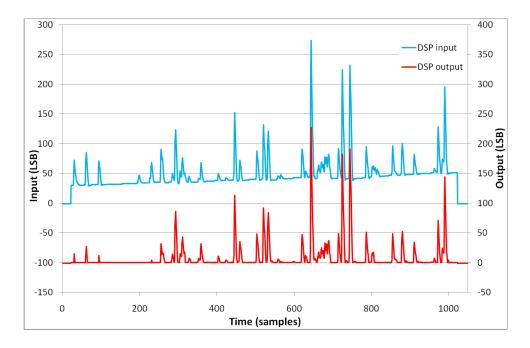

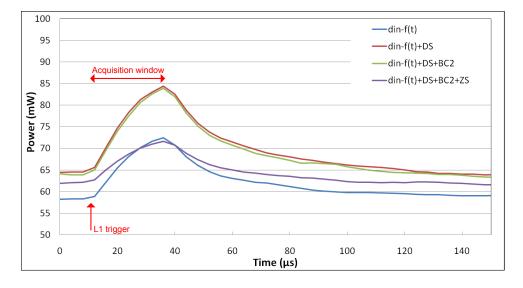

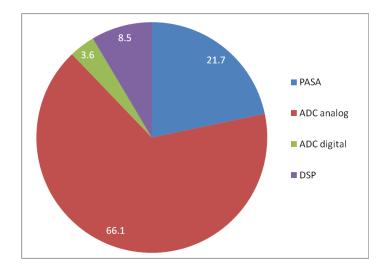

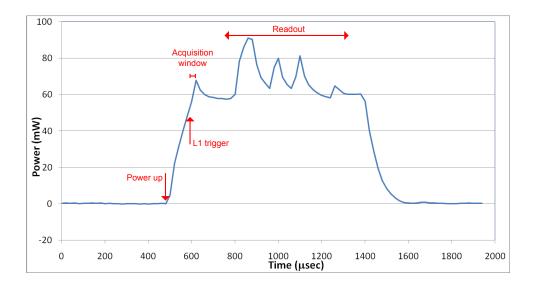

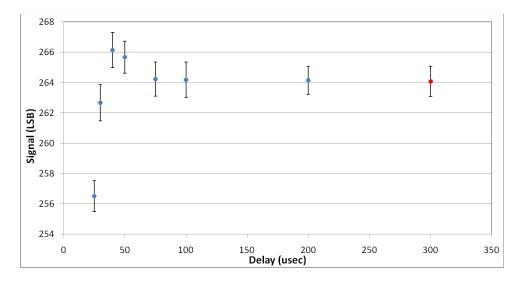

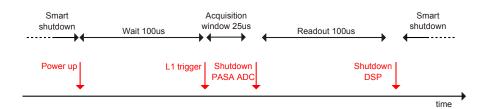

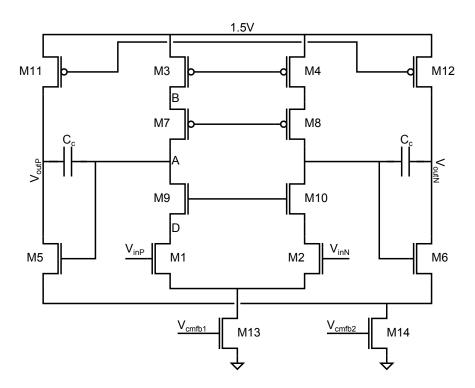

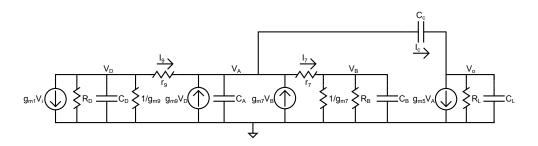

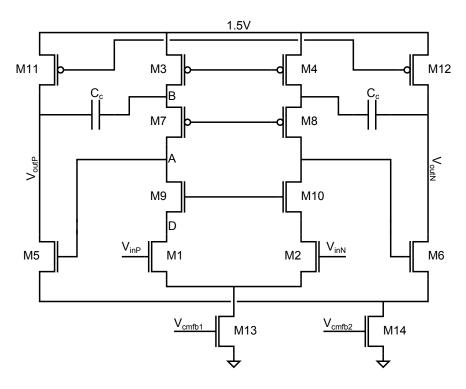

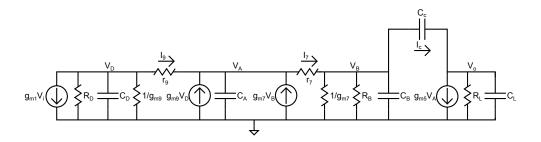

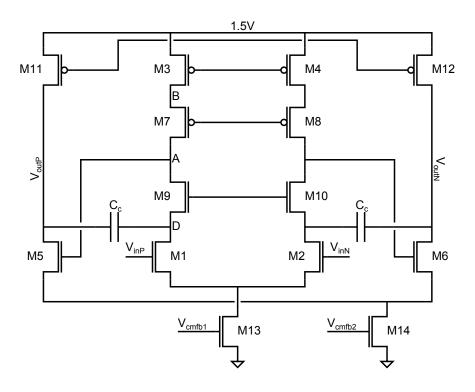

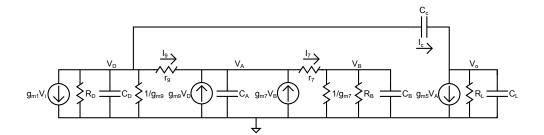

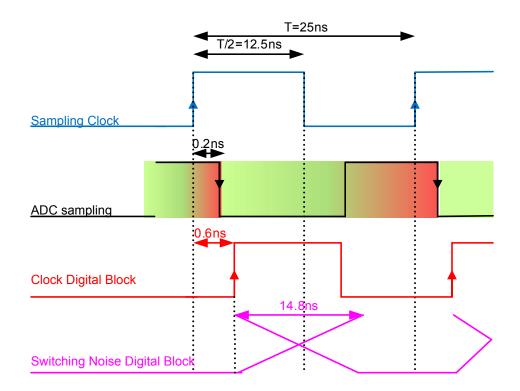

$$V_{n3o}(f) = v_{ts3}^2(f) \cdot g_{m3}^2(r_{o1} || r_{o3})^2$$